CNN已經廣泛用于圖像識別,因為它能模仿生物視覺神經的行為獲得很高識別準確率。最近,基于深度學習算法的現代應用高速增長進一步改善了研究和實現。特別地,多種基于FPGA平臺的深度CNN加速器被提出,具有高性能、可重配置、快速開發周期等優勢。

盡管目前FPGA加速器已經展示了相比通用處理器更好的性能,加速器設計空間并沒有很好發掘。一個嚴重的問題是,一個FPGA平臺的計算吞吐并未很好匹配內存帶寬。因此,已有的方案要么未充分利用邏輯資源,要么未充分利用內存帶寬,都不能獲得最佳性能。同時,深度學習應用不斷增加的復雜度和可擴展性讓這個問題更加嚴重。

為了克服這個問題,我們利用roofline模型提出一種設計分析方法。對于任意CNN設計方案,我們量化分析它使用不同優化技術(循環分塊、變換)的計算吞吐和所需內存帶寬。在roofline模型幫助下,我們可以發現最好性能和最低FPGA資源需求的解決方案。

作為案例研究,我們在VC707 FPGA板卡上實現了一個CNN加速器,并將它與之前的方案對比。我們的實現在100MHz工作頻率下可獲得61.62GFLOPS的峰值處理能力,大大優于之前的方案。

【1. 簡介】

CNN是著名的深度學習架構,從人工神經網絡擴展而來,它已經大量用于不同應用,包括視頻監控,移動機器人視覺,數據中心的圖像搜索引擎等【6】【7】【8】【10】【14】

受生物視覺神經行為的啟發,CNN用多層神經元相連處理數據,在圖像識別中可獲得很高準確率。最近,基于深度學習算法的現代應用快速增長進一步改善了DCNN的研究。

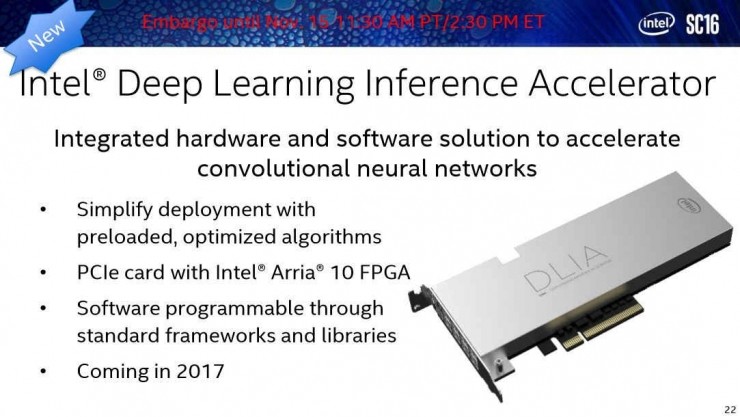

由于CNN的特殊計算模式,通用處理器實現CNN并不高效,所以很難滿足性能需求。于是,最近基于FPGA,GPU甚至ASIC的不同加速器被相繼提出【3】【4】【9】以提升CNN設計性能。在這些方案中,基于FPGA的加速器由于其更好的性能,高能效,快速開發周期以及可重配置能力吸引了越來越多研究者的注意【1】【2】【3】【6】【12】【14】。

對于任意CNN算法實現,存在很多潛在解決方案,導致巨大的設計空間。在我們的實驗中,我們發現使用同樣FPGA邏輯資源的不同方案性能有最大90%差距。尋找最優解不無價值,尤其當考慮FPGA平臺計算資源和內存帶寬限制時。實際上,如果一個加速器結構并未仔細設計,它的計算吞吐與內存帶寬不匹配。未充分利用邏輯資源或內存帶寬都意味著性能下降。

不幸的是,FPGA技術進步和深度學習算法同時將該問題復雜化了。一方面,當前FPGA平臺不斷提升的邏輯資源和內存帶寬擴大了設計空間,采取不同FPGA優化技術(如循環分塊、變換)會進一步擴大設計空間。另一方面,為了滿足現代應用需求,深度學習可擴展性和復雜性在持續增長。因此,在巨大的設計空間中尋找最優解就更加困難,亟需一種高效檢索基于FPGA的CNN設計空間的方法。

為了高效檢索設計空間,本文提出了分析設計的方法。我們的工作優于以前的方法,原因有二:

首先,【1,2,3,6,14】主要關注計算引擎優化,要么忽視了外部存儲器操作,要么直接將他們的加速器接入外部存儲器。我們的工作則考慮了緩沖區管理和帶寬優化。

其次,【12】通過數據重用減少了外部數據獲取從而獲得加速。但是這種方法不必導致最優全局性能。另外他們的方法需要對每層重新配置,不太方便。我們的加速器無需重編程FPGA就能執行不同層的計算。

本文主要貢獻如下:

* 量化分析可能解決方案的計算吞吐和所需內存帶寬;

* 在計算資源和內存帶寬限制下,我們用roofline模型識別所有可能的解決方案,討論了不同層如何尋找最優解;

* 我們提出一種CNN加速器設計,對每層使用統一的循環展開因子;

* 實現了CNN加速器,獲得61.62GFLOPS處理性能,是目前最優的;

【2. 背景】

2.1 CNN基礎

CNN受神經科學研究的啟發,經過長達20多年的演變,CNN在計算機視覺、AI(【11】【9】)領域越來越突出。作為一種經典有監督學習算法,CNN使用前饋處理用于識別,反饋用于訓練。在工業實踐中,很多應用設計者離線訓練CNN,然后用訓練好的CNN實現實時任務。因此,前饋計算速度是比較重要的。本文關注用基于FPGA的加速器設計前饋計算加速。

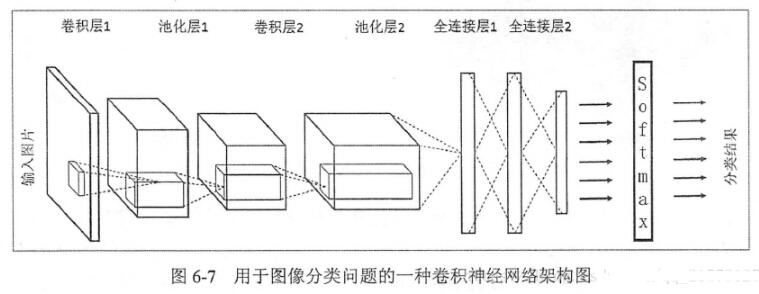

一個典型CNN由兩部分組成:特征提取器 + 分類器。

特征提取器用于過濾輸入圖像,產生表示圖像不同特征的特征圖。這些特征可能包括拐角,線,圓弧等,對位置和形變不敏感。特征提取器的輸出是包含這些特征的低維向量。

該向量送入分類器(通常基于傳統的人工神經網絡)分類器的目的是決定輸入屬于某個類別的可能性。

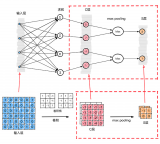

一個典型CNN包括多個計算層,例如,特征提取器可能包括幾個卷積層和可選的下采樣層。圖1展示了卷積層的計算。

?

卷積層收到N個特征圖作為輸入,每個輸入特征圖被一個K * K的核卷積,產生一個輸出特征圖的一個像素。滑動窗的間隔為S,一般小于K。總共產生M個輸出特征圖用于下一卷積層。卷積層的偽代碼如下:

for(row = 0; row < R; row ++)

{

for(col = 0; col < C; col ++)

{

for(to = 0; to < M; to ++)

{

for(ti = 0; ti < N; ti ++)

{

for(i = 0; i < K; i++)

{

for(j = 0; j < K; j++)

{

output_fm[to][row][col] += weights[to][ti][i][j] * input_fm[ti][S * row + i][S * col + j];

}

}

}

}

}

}

在前饋計算角度,之前的論文【5】證明卷及操作會占據超過90%的總計算時間,所以本文我們關注加速卷積層。后面會考慮集成其他可選層,如下采樣層、最大池化層。

一個真實的CNN

圖2展示了一個真實CNN應用,摘自【9】。該CNN包括8層,前5層為卷積層,第6~8層為全連接人工神經網絡。該算法接收3通道224x224輸入圖像(從原始256x256三通道RGB圖像變換而來),輸出1000維向量表示1000個類別的可能性。

第一層輸入為3個224x224分辨率的特征圖,輸出96個55x55分辨率的特征圖,輸出分為兩個集,每個48組特征圖。表1記錄了該CNN的配置。

?

2.2 Roofline模型

計算和通信是系統吞吐優化的兩個基本限制。一個實現可能是計算受限的或訪存受限的。【15】開發了roofline性能模型來將系統性能同片外存儲帶寬、峰值計算性能相關聯。

公式(1)表示了特定硬件平臺的可達吞吐率,用GFLOPS作為評估指標。

一個應用實際GFLOPS不會高于這兩項中的最小值:第一項為所有可用計算資源提供的峰值計算能力(計算上限),第二項為給定計算-通信比時系統訪存帶寬可支持的最大浮點性能(IO帶寬上限)。計算-通信比,又稱每DRAM傳輸運算量,表示特定系統實現所需的DRAM訪問量。

圖3將roofline模型可視化,分別展示了計算上限和IO帶寬上限。算法2相比算法1有更高計算-通信比,或更好的數據重用.從圖中看到算法2充分利用所有硬件計算資源,性能優于算法1。

【3. 加速器設計探索】

本節首先提供了我們的加速器結構概覽,介紹了FPGA平臺上的幾個設計挑戰。為了克服這些挑戰,我們提出了相應的優化技術。

3.1 設計概覽

如圖4所示,一個CNN加速器設計包括:處理單元(PE),片上緩存,外部存儲器以及片內外互聯。PE是卷積的基本計算單元。用于處理的所有數據放在外部存儲器。由于片上資源限制,數據首先緩存到片上buffer,之后送入PE。這里使用雙緩沖將傳輸時間掩蓋于計算時間。片上互聯用于PE和片上緩沖的通信。

在FPGA平臺上有這樣幾個設計挑戰阻礙了高效的CNN加速器設計:首先,片上數據只有很小一部分,故循環分塊(loop tiling)是必要的,不合適的循環分塊可能降低數據重用和數據并行處理效率。

其次,PE和緩沖區組織及其互聯應仔細考慮,這樣能高效處理片上數據。第三,PE的數據處理吞吐應該匹配FPGA平臺的片外訪存帶寬。

本節我們從Code1開始優化,提供了連續步驟獲得最優處理效率。

使用了循環分塊的代碼如下:

注意到循環變量i和j并未分塊,因為CNN中卷積層kernel尺寸K太小(3~11)。

第二,我們討論了計算引擎優化并將計算性能與分塊系數建立聯系。

第三,我們使用數據重用技術減少外存訪問,建立了計算-訪存比和分塊系數的聯系;

第四,利用上述兩個變量,我們定義了設計空間,在FPGA平臺上找最優解;

第五,我們討論了怎樣為多層CNN應用選擇最好的加速器。

電子發燒友App

電子發燒友App

評論