摘要: 介紹了精密時鐘同步協議(PTP)的原理。本文精簡了該協議,設計并實現了一種低成本、高精度的時鐘同步系統方案。該方案中,本地時鐘單元、時鐘協議模塊、發送緩沖、接收緩沖以及系統打時標等功能都在FPGA中實現。經過測試,該方案能夠實現ns級同步精度。該方案成本低,并且易于擴展,非常適合局域網絡時鐘同步的應用領域。

在很多大型物理實驗和工業應用中,時鐘同步技術都扮演著舉足輕重的作用。比如在中國四川錦屏暗物質探測實驗中,需要為多個獨立探測裝置提供相應的時間信息,這些探測器包括中心探測器(HpGe)、液氬反符合探測器、實驗室外部宇宙線反符合探測器[1]。又比如在大亞灣中微子實驗中,需要為三個實驗廳的子探測器提供同步時鐘和時間戳,也需要為未來的長基線中微子振蕩實驗提供同步時鐘和時間戳[2]。

為此,本文基于可編程邏輯器件FPGA,設計了一套高精度、低成本、易于擴展的時間戳同步系統。

1 PTP協議簡介

PTP精密時鐘定時協議又稱為IEEE 1588協議。它的基本功能是利用基于時間戳的報文通信的方法,使得分布式網絡中的所有的時鐘都與特定的某個時鐘保持精確同步。IEEE 1588協議可以用軟件實現,也可以用專門的硬件實現。很顯然,用硬件實現能達到更高的精度。本文中的同步系統就是基于純硬件實現的。

IEEE 1588協議中定義了5種類型的傳輸報文[3]:同步報文(sync)、跟隨報文(follow_up)、延時請求報文(delay_req)、延時響應報文(delay_resp)和管理報文(management)。其中前4種報文主要用于時間戳交換,具體的時間戳交換的過程示意圖如圖1所示。

?

圖1 PTP協議同步過程示意圖

如圖1所示,時間戳同步過程包括主節點和從節點,主節點和從節點都利用晶振維持本地時鐘。同步的目的是使從節點的本地時鐘的時間戳與主節點本地時鐘的時間戳達到相對同步。未同步時,從節點相對主節點有一個時間偏差offset。同步的過程能夠計算出這個偏差。

主時鐘周期性地向從時鐘發送同步報文SYNC,這個報文中沒有任何有效數據,但是當SYNC發出時,主節點能夠記錄下來時間戳t1,當從節點接收到SYNC,從節點能夠記錄下來時間戳t2。為了讓從節點也知道t1,稍后主節點向從節點發送跟隨報文FOLLOW_UP,這個報文中包含了t1這個有效數據。

然后,為了計算主節點到從節點的延時,在從節點接收到FOLLOW_UP后一段時間,從節點向主節點發送一個DELAY_REQ報文。和SYNC類似,當DELAY_REQ離開時得到時間戳t3,當DELAY_REQ到達主節點時,主節點得到時間戳t4。一段時間后,主節點再向從節點發送DELAY_RESP報文,這個報文中包含了t4,從而從節點得到了4個時間戳t1~t4。

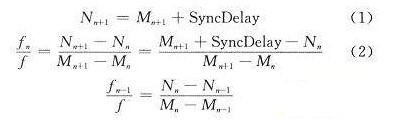

有了以上4個時間戳之后,假設主節點到從節點與從節點到主節點傳輸和網絡延時不變,可以得到傳輸延時和時鐘偏差的計算方法:

如果PTP主從鏈路對稱,即Dm2s=Ds2m=delay,則:

由以上分析方法可知,PTP主從節點鏈路對稱與否會影響offset的計算,從而會影響時間戳的同步精度。

另外,由于主節點和從節點需要用本地晶振維護本地時鐘。而隨著時間的積累,晶振存在頻率漂移,并且不同晶振的固有頻率也會有偏差,這兩個屬性都會影響時鐘同步的精度。

為了實現高精度時間同步,設計同步系統時應該同時考慮到主從節點鏈路的對稱性和晶振的特性。

2 電子學設計

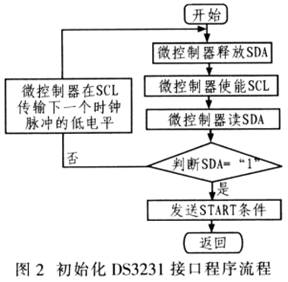

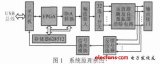

時鐘同步系統的整體結構設計如圖2所示。

?

圖2 時鐘同步系統的硬件結構圖

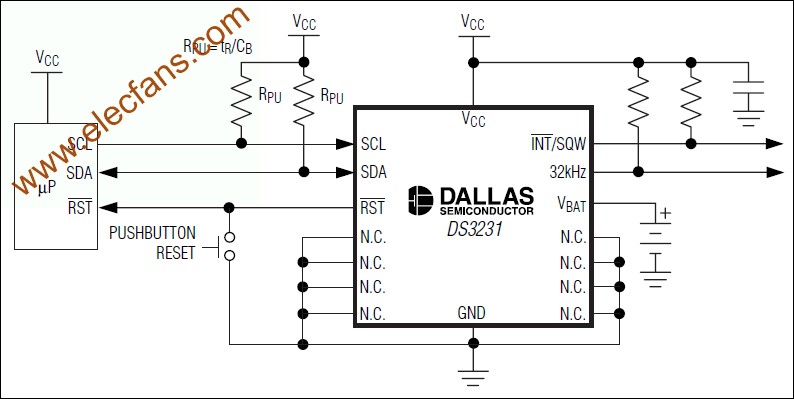

本方案中主節點和從節點使用同一塊硬件電路,在設計的時候,硬件電路板上設計了一個跳線器,可以選擇一塊硬件電路是主節點或者從節點。為了保證主從節點的鏈路對稱, PCB電路板時鐘收發路徑以及PTP報文收發路徑的長度都應該用蛇形線設計來保證長度一致。另外,為了消除晶振的頻率漂移以及頻率偏差帶來的影響,本方案中從節點不使用本地晶振,而是直接使用主節點傳輸來時鐘信號作為時間戳的時鐘,也就是說主節點和從節點使用了同源時鐘。

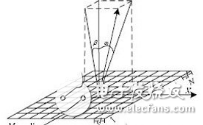

雖然主從節點使用的本地clock是同源的,但是由于clock的傳輸路徑的差異,主從節點的clock是有相位差異的。這個相位差如果不考慮在設計方案中的話,會嚴重影響整個時鐘系統能夠實現的同步精度。如圖3所示,如果系統中沒有考慮主從節點的本地clock的相位差,也就是圖中phase,那時鐘系統所能達到的同步精度最好也就是相位差的值。假設,主從節點的周期T為100 ns,主從節點的相位差為60 ns,那說明同步系統所能達到的最高精度為60 ns。

?

圖3 主從節點時鐘相位差測量的重要性示意圖

為了進一步提高時間戳同步的精度,必須設計相位測量模塊,消除主從時鐘相位差對時間戳的同步精度帶來的影響。所以,主節點中包括了相位鑒別芯片以及ADC芯片,用來精確測量主從節點時間戳的時鐘相位差。

有了這個相位差測量模塊,就真的可以消除主從節點時間戳的時鐘相位差帶來的影響嗎?答案是肯定的。圖4為主從節點時鐘傳播示意圖,AD8302即為本文中所用的相位鑒別芯片。

?

圖4 主從節點時鐘傳播示意圖

我們已經知道,為了使從節點與主節點的時間戳實現精確同步,最直接的方法就是算出盡量精確的offset值,也就是要得出盡量精確的t1~t4的值。

圖4中,Clk1為主節點晶振時鐘,Clk2為從節點從主節點接收到的時鐘,由于有一段長的傳播路徑,因而Clk2相對Clk1會有一個相位差。為了在主節點測量相位差,Clk3是從節點將Clk2直接發送到主節點而得到的時鐘,因而Clk3相對于Clk2又會有一個相位差。具體Clk1~Clk3的示意圖如圖5所示。

?

圖5 主從節點時鐘關系圖

對于時間戳t1而言,t1指的是SYNC包從主節點發出的時刻,觸發時鐘為Clk1,而時間戳時鐘是主節點的系統時鐘Clk1,因而t1是精確的。對于時間戳t2而言,t2指的是SYNC包到達從節點的時刻,觸發時鐘為Clk2,而時間戳時鐘是從節點的系統時鐘Clk2,因而t2也是精確的。對于時間戳t3而言,t3指的是DELAY_REQ包從從節點觸發出的時刻,觸發時鐘為Clk2,而時間戳時鐘為從節點的系統時鐘Clk2,因而t3也是精確的。對于時間戳t4而言,t4指的是DELAY_REQ包到達主節點時的時刻,觸發時鐘為Clk3,而時間戳時鐘為主節點的系統時鐘Clk1,因而t4不是精確的,是有偏差的。由圖5的時鐘關系圖可知,精確的t4p應該在t4之前:

?

可見,相位差測量模塊在整個時間戳同步方案中取到了舉足輕重的作用。

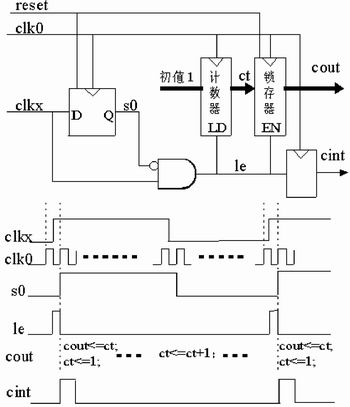

3 固件程序設計

3.1 主節點固件設計

主節點的固件結構框圖如圖6所示,A/D控制模塊和相位測量模塊是用來控制幅相鑒別芯片和ADC芯片。發送緩沖的作用是將主節點時鐘同步協議中的通信報文以曼徹斯特編碼方式發送出去,接收緩沖的作用是從接收路徑中解碼出相應的通信報文。本地時鐘模塊的作用就是維護一個本地時鐘。主節點時鐘同步協議的主要作用是控制報文的發送和接收。

?

圖6 主節點固件結構框圖

圖7為主節點時鐘同步協議模塊的狀態機轉換圖。

?

圖7 主節點同步協議模塊的狀態機轉換圖

idle狀態下,當檢測到pps信號的上升沿,則開始整個同步周期。首先,開始ADC的讀取操作,當等到AD_ready=’1’,則說明ADC的數據已經準備好,然后進行讀取保存即可。然后,進入到sync狀態,這個狀態下,主節點會向從節點發送SYNC同步包,之后模塊進入sync_wait狀態。等一段固定的時間之后,模塊進入follow狀態,在這個狀態下,主節點會向從節點發送FOLLOW_UP同步包。之后模塊進入after_follow_wait,等待一段固定的時間之后,模塊進入delay_req_pre,這個狀態下,主節點會通知從節點可以發DELAY_REQ包了。之后,模塊等待DELAY_REQ包,如果很長時間都沒有等到DELAY_REQ包,即等待超時,則模塊返回idle狀態;如果接收到了DELAY_REQ包,主節點就向從節點發送DELAY_RESP。最后,等一段時間后,模塊返回到idle狀態。

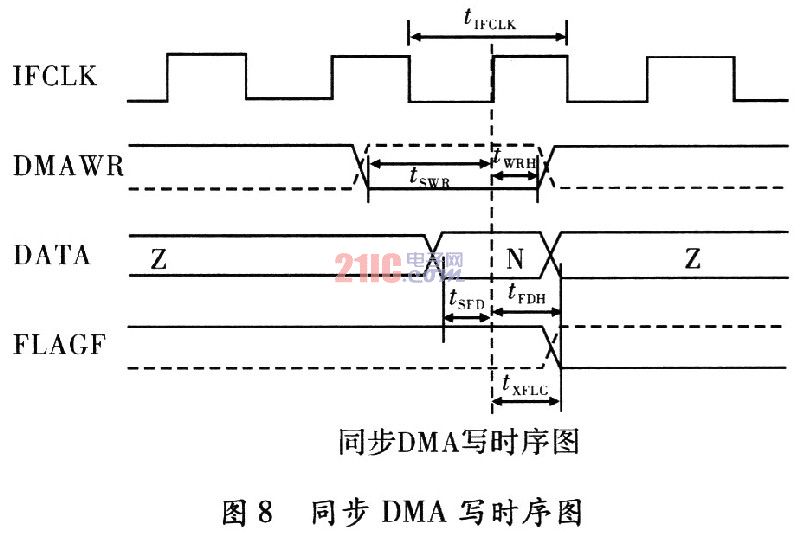

3.2 從節點固件設計

從節點固件的結構框圖如圖8所示,相位部分計算模塊用來計算出前文說到的phase值,offset計算模塊的作用是用t1~t4和phase值計算出精確的offset值。從節點時鐘同步協議的主要作用是控制報文的發送和接收和更新本地時鐘。

?

圖8 從節點固件結構框圖

圖9為從節點時鐘同步協議模塊的狀態機轉換圖。

?

圖9 從節點時鐘同步協議模塊的狀態機轉換圖

當處在idle狀態時,從節點監測接收到的數據流,直到監測到sync包后立即進入wait_follow狀態。在wait_follow狀態,從節點同樣監測接收的數據流,直到監測到follow_up包后,立即進入wait_pre狀態,如果在這個狀態很久都沒有接收到follow_up包,將等待超時返回到idle狀態。同樣,wait_pre狀態下,直到監測到delay_req_pre包后,跳入delay_req狀態;如果等待超時,則返回idle狀態。delay_req狀態下,從節點向主節點發送delay_req包后立即進入wait_delay_resp狀態。在wait_delay_resp狀態下,監測到delay_resp包后,從節點立即進入phase_cacul狀態;如果長時間沒有監測到delay_resp包,則返回idle狀態。在phase_cacul狀態下,開始相位差計算模塊后,立即進入wait_phase_result狀態。在wait_phase_result狀態下,等到相位測量結果準備好后,進入delay_cacul狀態;如果長時間,相位結果都沒有準備好,或者相位結果錯誤,則返回idle狀態。在delay_cacul狀態下,開啟offset計算模塊后,進入wait_result狀態。在wait_result狀態下,當檢測到偏移測量結果準備好信號后,進入offset_update狀態;否則返回到idle狀態。在offset_update狀態下,從節點時鐘同步協議向本地時鐘模塊發送偏移校正信號,從而更新從節點的本地時鐘,然后進入idle狀態。

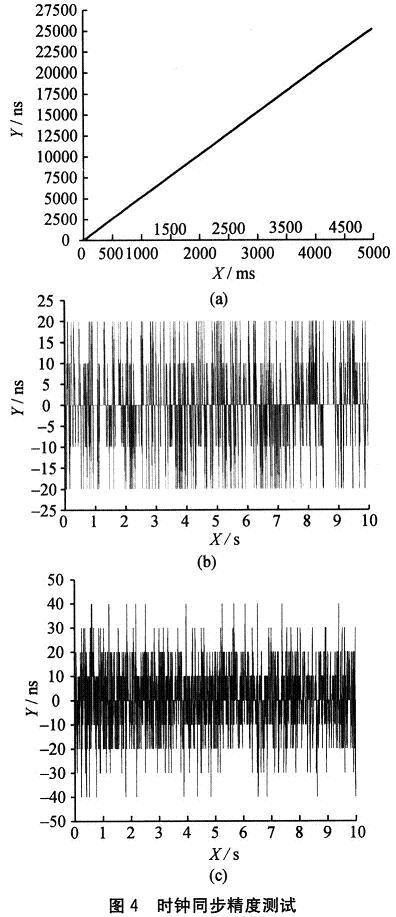

4 測試結果

實際測試環境包括一個主節點和一個從節點,之間用光纖連接。示波器用來觀察主節點和從節點輸出的pps信號。由于主從節點的時鐘相位不一致,示波器觀察到的就是這個相位差。pps上升沿到來時,主從節點時間戳通過串口模塊輸出給PC機。通過對比示波器測得的主從相位差以及pps上升沿主從時間戳的差值,就可以得出真實的時間戳同步精度。

本次測試使用了三種不同長度(3 m、6 m、5.15 m)的光纖,然后通過觀察在不同長度光纖下的實驗結果,從而可以判斷時鐘同步系統所能達到的精度。主從節點相位差直方圖以及相應的時間戳的差值直方圖略——編者注。

由這三種不同長度光纖所得出的結果來看,本文實現的同步時鐘系統的時間戳同步精度可達1 ns。

結語

本方案實現的時鐘同步系統,以IEEE 1588協議中基于時間戳的報文通信為基本原理,在純硬件電路(FPGA)中實現。通過在主節點添加了相位差測試模塊,消除了主從節點相位不同的影響,最后實現的時間戳同步精度高達1ns。

本文設計出來的時鐘同步系統所需成本低,同步精度非常高,非常適合應用在需要高精度時間戳的場合。

?

電子發燒友App

電子發燒友App

評論