摘 要:為了對障礙物距離精確測量,基于最新Zedboard FPGA(現場可編程邏輯陣列)開發板,采用軟硬件協同的設計 方法,設計了障礙物距離測量系統的軟硬件。系統為智能小車平臺提供了完整的距離測量服務,測距范圍能夠達到2cm~4.5m,精度可達0.2cm。該設計包含從底層硬件電路設計、可編程邏輯IP(IntellectualProperty)核設計、到Linux設備驅動的設計全部流程,對于在Zynq?7000FPGA上軟硬件從事開發的人員有一定的參考價值。

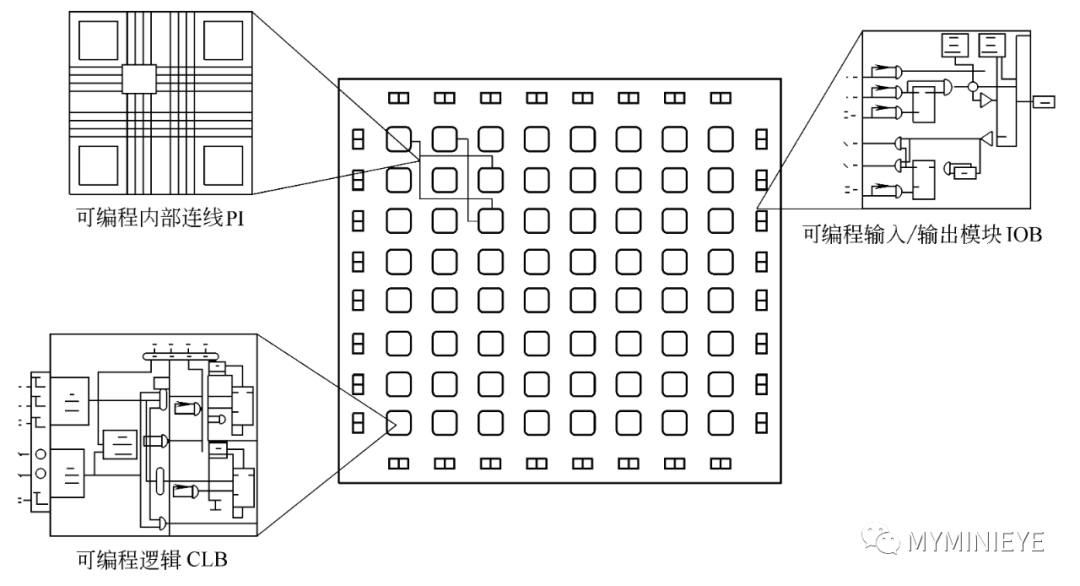

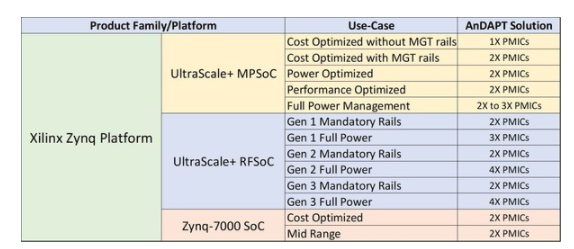

隨著集成電路的制造和應用技術的快速發展,嵌入式系統的性能也不斷提升,已經被廣泛應用于工業控制、航空航天、軍事以及消費電子等領域。在硅工藝的發展以及市場推動下,Xilinx公司推出了基于7系列FPGA的新一代全可編程(AllProgrammable)Zynq?7000系列產品。該系列產品,集成了嵌入式領域集大成者——雙核ARM CortexA9處理器和7系列28nm工藝FPGA芯片。Zedboard正是這樣一款基于Zynq?7000產品的實驗 開發板卡,提供了軟件和硬件設計的更多可能。本文基于目前FPGA業界最先進的Zedboard FPGA(現場可編程邏輯陣列)開發板,從底層硬件電路設計、可編程邏輯IP(IntellectualProperty)核設計、到Linux設備驅動的設計,實現了障礙物距離測量的軟硬件系統,并在智能小車平臺上,實現了距離測量服務。該方法對于在Zynq?7000FPGA上軟硬件的開發具有指導作用。

1、系統設計

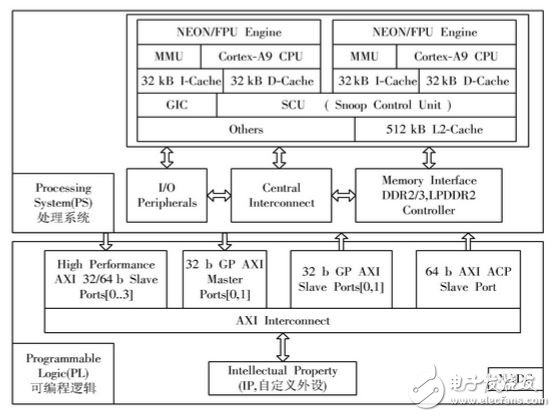

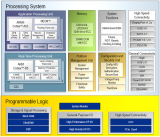

傳統上,FPGA中嵌入處理器內核,都是以FPGA為 主、處理器為輔,設計思路以可編程邏輯為主。然而新一代全可編程的Zynq?7000采取不同的思路,它是以處理器為主,FPGA為輔。FPGA變成了ARM處理器的一個協處理器[1]。圖1為Zynq?7000SoC芯片的結構圖。 簡單來說,Zynq由PS和PL兩部分組成:PS(Pro?cessingSystem,處理系統)相當于一片ARM芯片,而PL (ProgrammableLogic,可編程邏輯)相當于一片FPGA芯片。

圖1:Zynq結構圖

PS系統結構為:雙核A9處理器,其是整個平臺的控制中心,處理速度高達1GHz,可通過NEON擴展及單精度浮點單元進行增強,擁有32KB指令及數據L1 緩存,統一的512KBL2緩存和256KB片上存儲器;存儲接口,用以管理片內系統的存儲狀態,包含DDR3,DDR2和LPDDR2動態存儲控制器和兩個QSPI,NANDFLASH及NORFLASH控制器;通用外設,PS中的通用外設是ARM直接和外部設備通信的接口,含SPI,I2C, CAN,UART,GPIO,USB2.0等;其他組成部分。

PL部分結構為:低功耗可編程邏輯,包含28K~ 350K個邏輯單元,240K~2180K可擴展式BlockRAM和80~900個DSPSlice;XADC,為PL內置的12b模/數轉換器;通用/定制外設,PL中的外設是PL中的器件和 外部通信的接口。在ARM接口不夠用時,可以利用PL的外設接口。PS和PL之間的數據交互,則是通過AXI(AdvancedeXtensibleInterface)接口實現的。具體有:高性能AXI接口(HighPerformanceAXISlavePorts),共4個;通用AXI接口,包括兩個主設備接口和兩個從設備接口,共4個;加速一致性端口,是ARM多核架構下定義的一種接口。

根據Zynq結構特點,在應用系統結構設計時注意,使用由Zynq這樣一款功能強大的SoC芯片,與一般的ARM芯片不同,與常用的FPGA,更存在區別。它要求 硬件和軟件之間進行協同設計,共同實現既定的性能指標要求。在SoC設計中,IP(IntellectualProperty,知識產權)核重用技術是一個很重要的概念,它是軟硬件協同設計的關鍵,通過標準化IP核可以實現模塊復用,可以完成大規模的、復雜的SoC設計[3]。

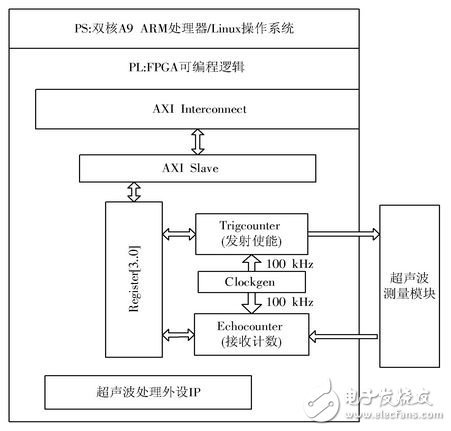

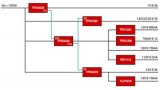

本文以一個超聲波測距系統為例,介紹如何在ZynqSoC上,定制IP、設計Linux設備驅動等,并完整的闡述了從硬件到軟件的設計流程。設計的系統結構如圖2所示。PS上,運行Linux操作系統,為LinaroUbuntu發行版。根據文獻[2]的指導操作,使用Xilinx公司的開發軟件完成配置,使PS可以運行操作系統。

圖2:系統結構圖

PL部分按照系統控制的需求進行定制。設計基于 XilinxAXI總線的超聲波處理外設IP核,與外部的超聲波發射和接收電路交互。在Linux操作系統下,這個IP核就成為了一個設備,這就需要編寫相應的設備驅動程序,實現超聲波測距功能的封裝。

2、 主要模塊設計

2.1 超聲波測距模塊

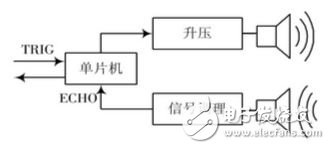

該模塊基本工作原理是:通過超聲波發射探頭,發射頻率為40kHz的超聲波信號;當超聲波信號遇到障礙物時,會發生反射;當超聲波接收探頭接收到40kHz頻率附近的聲波信號時,經過信號調理電路;再通過系統計算接收與發射之間的時間差計算障礙物距離。

圖3測距模塊

設計中共使用到了三個相同測距模塊,分別測量三個不同的方向上障礙物距離。測距模塊分為超聲波發射部分和接收部分,模塊的電路結構如圖4所示。具體是采用HC?SR04超聲波測距模塊,進行硬件設計[6]。該電路的對外接口為觸發(TRIG)控制端和回響(ECHO)信號接收端。通過I/O口TRIG觸發測距,提供了一個10ms以上的高電平觸發信號,該模塊將發出8個40kHz的方波用于探測,并自動檢測是否有回波信號。一旦檢測到有回波信號則通過I/O口ECHO輸出一個高電平回響信號,且回響信號的高電平時間tH(單位:ms)即高電平持續的時間與所測的距離S成正比。其對應關系為:

式中:S為測試距離;tH為高電平時間(單位:s);v為聲速340m/s。

發射部分:利用串口轉換芯片的升壓功能,采用MAX232將輸入JN1和JN2的3.3VTTL電平轉換,得到5V電平。它激勵超聲波發射探頭的信號壓差為10V, 發出40kHz的超聲波。如圖4所示。

圖4 發射電路

接收部分:對回波信號進行濾波、放大處理。接收電路圖如圖5所示。其中NET9為控制接收電路工作的使能端口,NET10為接收電路工作且接收到了回波信號時的響應信號。

圖5: 接收電路圖

2.2 IP核設計

使用Xilinx的設計工具XPS(XilinxPlatformStudio) 建立IP的流程,新建一個Ultrasonic(超聲波)IP核模塊。該IP核的模塊結構如圖2所示中的超聲波處理外設部分,其中Triggercounter,Clockgen和Echocounter使用VerilogHDL實現。根據超聲波測距模塊的測距時序要求,設計觸發和回響信號的邏輯,由Triggercounter和Echocounter實現。最終將測量到的數據放到AXI4定義的寄存器中,使處理器能從AXI總線上讀取數據。本IP核有4個寄存器(reg0~reg3),與AXI4總線相連,用戶可以通過這4個寄存器控制發射超聲波,獲取測量的距離。其中,reg0的功能是使能一次測距以及三個方向上測量完畢標志,圖6為reg0寄存器映射表;reg1~reg3為計數后計算得到的三個方向上超聲波測量到的距離數值。將設計的IP核添加到XPS工程中去,分配得到的地址空間為0x6E000000~0x6E00FFFF。

圖6:reg0寄存器映射表

2.3 Linux驅動設計

Linux設備驅動分為三類:字符設備、塊設備和網絡 設備。在這里需要編寫的是一個字符設備[5]。另外,編寫的設備將通過模塊化的方式加載到操作系統中,而不是靜態編譯到內核中。驅動程序在交叉編譯環境下,進 行模塊化編譯。得到以.ko為擴展名的驅動文件,使用 insmod和rmmod進行加載或者卸載,同時也可以通過lsmod查看是否已被加載。

建立一個ultrasonic_driver.c文件,使用交叉編譯環 境進行編譯,得到對應的可加載文件ultrasonic_driver.ko。在ultrasonic_driver.c中聲明設備名稱和模塊的物理地址,該物理地址對應于XPS中建立的嵌入式系統的地址。具體如下:

#defineDEVICE_NAME"ULTRASONIC_MOUDLE"#defineULTRASONIC_MOUDLE_PHY_ADDR0x6E000000

該設備驅動的主要函數有:設備初始化ultrason?ic_driver_module_init();三個方向上的距離測量函數,sys_ultrasonic_front_get(),sys_ultrasonic_right_get()和sys_ultrasonic_left_get();設備注銷ultrasonic_driv? er_module_exit()。

(1)設備初始化函數,完成注冊信息,當進行ins?mod操作時,操作系統會自動調用初始化函數,完成各 項信息的注冊。而設備注銷操作,與它相反,不做贅述。該初始化函數中,需要完成如下工作[4]:內核注冊設備驅動;創建ultrasonic_driver設備類;為ultrasonic_driver設備類創建一個ultrasonic_driver_device設備;為設備創建以下幾個文件:dev_attr_ultrasonic_trigger,dev_attr_ultra?sonic_front,dev_attr_ultrasonic_right,dev_attr_ultrason?ic_left,分別對應三個方向上的距離數值;將模塊的物理基地址映射到虛擬地址上;同時將其他幾個寄存器地址計算得到虛擬地址;打印調試信息,表明完成初始化工作。

(2)距離測量函數,以前向(front)測距為例,另外兩個方向(right,left)上類似。Linux中,sysfs是一種基于ram的文件系統,它提供了一種用于向用戶空間展現內核空間里的對象、屬性和鏈接。sysfs與kobject層次緊密相連,它將kobject層次關系表現出來,使得用戶空間 可以看見這些層次關系。可以通過CAT和ECHO接口命令來讀/寫sysfs。使用函數宏DEVICE_ATTR創建接口如下:

staticDEVICE_ATTR(ultrasonic_front,S_IRUSR|S_IWUSR,NULL,sys_ultrasonic_front_get);

DEVICE_ATTR宏聲明有4個參數,分別是名稱、權 限位、讀函數、寫函數。其中讀函數和寫函數是讀/寫功能函數的函數名。這樣對ultrasonic_front創建一個寫函 數sys_ultrasonic_front_get,其流程圖如圖7所示。

?

圖7:sys_ultrasonic_front_get流程圖

進入函數,首先會打印一條調試信息;然后向reg0(ultrasonic_trigger_addr)上寫入使能,使開始發射超聲波;循環檢測reg0的bit1,查看數據是否有效;如果數據有效,則讀取出reg1(ultrasonic_front_addr)上的數據值,并打印出來。完成一次讀取操作。 完成以上設備驅動設計后,使用配置好的交叉編譯環境,將該驅動代碼編譯為ultrasonic_driver.ko文件。將該文件放入啟動的SD卡中。

3系統測試

對XPS構建的系統,建立U?Boot引導,編譯配置內 核源碼,編譯設備樹,并制作根文件系統,制作ramdisk鏡像文件,得到所有的文件zImage,devicetreee.dtb,ram?disk8M.img.gz,BOOT.BIN。放入Zedboard板的SD卡中,同時也將ultrasonic_driver.ko文件放入SD卡,上電啟動,直至完成。

在連接到Zedboard串口的超級終端下,掛載SD,執行如下步驟:

mount/dev/mmcblk0p1/mnt //掛載SD卡

cd/mnt//進入SD卡目錄

insmod./ultrasonic_driver.ko//加載ultrasonic_driver.ko模塊

dmesg//查看加載打印信息lsmod//查看加載的模塊

cd/sys/class/ultrasonic_driver/ultrasonic_driver

//進入創建的設備目錄,sysfs下

catultrasonic_front//讀取一次前向超聲波測量距離

catultrasonic_right//讀取一次右邊超聲波測量距離

catultrasonic_left//讀取一次左邊超聲波測量距離

系統測試后可以在終端里看到打印的加載信息“ul?trasonicdriverinitialsuccessfully!”和讀取到的測量距離數值。調整超聲波探頭前方障礙物距離,還可以得到不同的距離值,最終,實現的距離測量能夠達到2cm~4.5m 的范圍,精度可達0.2cm。

4結語

本文基于FPGA業界最先進的芯片Zynq以及開發平臺Zedboard,融合軟硬件設計,從底層的各功能電路設計,VerilogHDL代碼編寫,VerilogIP核設計,到Linux設備驅動設計,完成了整個設計流程,在智能小車平臺上實現了在Linux系統中利用超聲波測距的功能,達到2cm~ 4.5m的測距范圍,精度達0.2cm,為上層應用提供了支撐服務。該系統設計對基于Zynq?7000FPGA上的開發的多個方面(例如,對ARM+FPGA應用設計的理解、軟硬件結合的設計方法;Xilinx下AXI4?lite總線的IP核設計;Linux字符設備驅動設計)有指導性意義。

參 考 文 獻

[1]XilinxInc.Zynq?7000allprogrammableSoCtechnicalreference manual,v1.6.1[DB/OL].[2013?04?17].http://www.xilinx.com/sup? port/documentation/user_guides/ug585?Zynq?7000?TRM.pdf.

[2]陸佳華,江舟,馬岷.嵌入式系統軟硬件協同設計實戰指南:基于XilinxZynq[M].北京:機械工業出版社,2013.

[3]李洪濤,顧陳,朱曉華.FPGA技術開發(高級篇)[M].北京:國防工業出版社,2013.

[4]章立生,韓承德.SoC芯片設計方法及標準化[J].計算機研究與 發展,2002,39(1):1?8.

[5]KROAH?HARTMANCR.Linux設備驅動程序[M].魏永明,耿 岳,鐘書毅,譯.3版.北京:中國電力出版社,2005.

[6]深圳市捷深科技有限公司.HC?SR04超聲波測距模塊說明書 [DB/OL].[2014?04?10].

電子發燒友App

電子發燒友App

評論