1.背景介紹

空間輻射環境中的高能帶電粒子入射到半導體器件的特定區域有可能會引起單粒子效應,從宏觀角度看,FPGA的配置存儲器中該單元存儲的信息由“1”變成了“0”,即出現了存儲狀態的翻轉。美國Los Alamos國家實驗室、Brigham Young大學和Xilinx公司對FPGA的單粒子效應進行了多次實驗,得出了:單粒子效應引起的FPGA故障多數是由配置存儲器發生單粒子翻轉引起的。

針對FPGA內部的單粒子效應故障,研究者們提出了相應的檢測與加固設計方法,如三模冗余(TMR)設計、兩模塊冗余(DMR)設計、時間三模冗余(TTMR)設計、狀態機狀態編碼加固設計、運算單元的結果校驗等多種方法。這些方法從邏輯設計方面提高了FPGA抗單粒子效應的能力。

?

本文作者在項目實踐中對于系統可靠性設計方面采用過三模冗余、糾錯編碼等加固措施。這些加固方法帶來了系統資源占用率的上升和運算速度的降低,但是其對于抗單粒子翻轉性能的提升程度卻難以通過簡單方法獲得,因此需要一種驗證方法對其加固效果做出客觀評估,需要一個測試系統來完成具有充足覆蓋率的自動化大規模測試。本文所描述的基于動態重構技術的FPGA電路容錯性能評估系統即在此需求下設計完成的。

2.動態重配置技術簡介

FPGA的“動態可重配置” ,是指在系統運行期間,隨時可以通過對FPGA的重新配置來改變其邏輯功能,而且并不影響系統的正常運行, FPGA邏輯功能的改變在時間上保持動態連續。由此可見, FPGA的動態可重配置不僅可以改變而且能夠動態地改變數字邏輯系統的功能,與靜態可重配置相比, FPGA的動態可重配置有著更廣闊的應用前景。

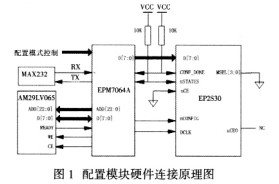

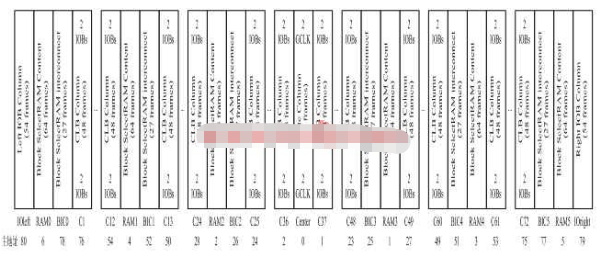

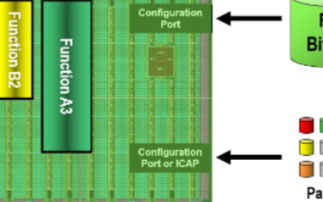

如圖2.1所示,有兩種途徑可以實現動態重配置:(1) 依靠JTAG、SlectMAP等外部配置端口進行配置,這種方式的重配置依靠FPGA外部芯片或者上位機系統;(2) 依靠內部端口(ICAP)完成對配置寄存器,由FPGA內部產生配置指令,完成對FPGA動態區域的重新配置。

2.1內部配置訪問端口

內部配置訪問端口(Internal Configuration Access Port, ICAP)是FPGA內部配置寄存器的訪問端口,為動態重構技術在片上可編程系統的應用提供了基本條件。在嵌入式的微處理器或其他用戶邏輯控制下,從PC或者片上存儲器中讀取配置數據寫入該ICAP接口即可完成芯片的動態重構。ICAP用于動態局部自重構,它是FPGA內部單元的入口,用戶可通過ICAP訪問配置寄存器。ICAP與SelectMAP工作方式相同,但不同于SelectMAP的雙向數據總線,ICAP提供專門的讀/寫總線,總線寬度可以通過設置參數ICAP_WIDTH來確定,有三種可選的數據寬度:8位、16位和32位。

?

?

2.2配置信息寫入與回讀

配置信息寫入的過程即是按照配置命令將數據寫入配置寄存器,寫入配置信息就是完成FPGA的完整配置或重配置。寫入過程是通過發送包數據到幀輸入寄存器(Frame Data Register Input, FDRI)來實現的,寫入過程包括寫命令字、寫數據。

配置信息回讀是通過配置端口將FPGA內部配置存儲器中的數據讀出的過程。回讀過程可以讀出CLB、IOB的寄存器、FPGA內部存儲器的當前狀態以及布線資源的配置情況等,而且可以通過對回讀數據的校驗來檢驗當前配置數據的正確性。本文設計的系統通過回讀將待測系統的配置信息讀入存儲器,在此配置信息基礎上注入錯誤后寫回到配置存儲器以實現故障模擬。

回讀過程是通過發送命令從幀輸出寄存器(Frame Data Register Output, FDRO)中讀取數據包來實現的。回讀過程分為寫操作命令、讀取數據和恢復現場三部分。每一幀的回讀數據內容都決定著與其相應的物理排列的FPGA功能模塊的功能邏輯.

3.基于動態重構技術的FPGA電路容錯性能評估系統的實現

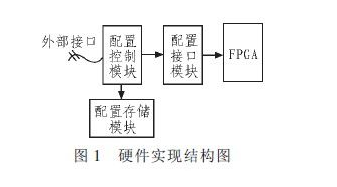

本系統結構如圖3.1所示,分為上位機控制模塊、Micro Blaze模塊、配置信息讀寫模塊、激勵產生與測試數據收集模塊。其中上位機模塊提供用戶交互界面,可對模擬粒子量、測試循環等參數進行配置,與測試平臺之間依靠TCP/IP協議通信。在動態重構技術支持下,測試平臺只需在一片FPGA內即可實現。為了與上位機實現TCP/IP通信,測試平臺內嵌了Micro Blaze處理器。Micro Blaze處理器模塊獲取上位機指令并翻譯成邏輯時序通過GPIO發送至平臺的邏輯部分。邏輯部分包含了配置信息讀寫、待測模塊激勵生成和數據收集等功能。下面將分別詳細介紹上位機控制程序、Micro Blaze模塊和邏輯部分的實現。

?

3.1上位機控制程序和Micro Blaze模塊

本系統的上位機控制程序基于MFC編寫,TCP/IP協議棧的實現則是繼承了MFC提供的異步Soket類CAsyncSocket。FPGA中嵌入了Micro Blaze處理器,利用IwIP協議棧實現和上位機的通信。通過兩者的相互配合可以對待測系統的配置文件大小、模擬粒子注入量、粒子注入量放大倍數、配置信息bit翻轉個數和測試循環次數等參數進行配置。并且可以將待測系統的測試數據進行收集,并發送給上位機。

參數配置完成后系統軟件即可開始測試循環,每次循環包含產生隨機bit翻轉位、待測系統運行和收取數據三個步驟。第一次循環時不產生隨機翻轉位而直接開始待測系統運行,收集此次的數據作為待測系統對激勵的正確響應,以后每次循環收集到的待測系統輸出數據與此數據對比得到系統是否正常工作。每次循環結束后,該次循環產生的隨機位置和系統工作狀態信息會被記錄寫入文件。循環次數達到參數設定值后系統生成測試報告。

3.2邏輯部分結構

本系統的邏輯部分完成待測模塊的配置、故障模擬注入、激勵產生與數據收集。結構框圖如圖3.2所示。待測模塊作為FPGA內的動態區,其首次配置由完整比特流完成,開始測試之后的重配置由ICAP讀寫控制模塊通過ICAP端口完成。本系統的待測模塊可由網表輸入,也可由HDL代碼或原理圖輸入。本文以RS編碼器為例,分別將經過局部三模冗余,分布式三模冗余和全局三模冗余加固的RS編碼器網表文件輸入動態區,對三種加固措施的可靠性進行測試。

?

激勵產生和數據收集模塊根據待測模塊變化需要做出相應調整,這兩個模塊協同工作完成待測模塊真實工作情況的模擬。數據收集模塊將待測模塊產生的數據送往Micro Blaze,然后通過TCP數據包發送到上位機進行分析。本文測試中用到的為255-243 RS編碼器,即輸入243字節,輸出243字節后帶12字節的RS糾錯碼。測試系統對RS編碼器的激勵為累加數且保持每次循環都一致,輸出的255字節編碼結果作為輸出采樣數據送到上位機軟件平臺做自動比對。

?

ICAP讀寫控制模塊即為配置信息讀寫模塊,其結構如圖3.3所示,通過產生ICAP讀寫控制時序和指令序列,該模塊在系統首次完整配置完成后通過Readback Frame模塊將待測模塊配置信息回讀至Block RAM。此回讀數據將作為以后錯誤注入時配置信息的基礎。在以后的注錯過程中,Write Frame模塊將配置信息讀出,根據Micro Blaze模塊提供的注錯位置,對配置信息加錯,并寫入到ICAP端口中。

主控模塊對系統測試的步驟進行控制和跟蹤,接收來自Micro Blaze模塊的指令脈沖。Micro Blaze模塊發出的指令脈沖是將TCP數據包中的指令譯碼得到的。Micro Blaze模塊還將上位機發出的隨機位置數據發送至ICAP讀寫模塊,由后者經位置譯碼后產生隨機bit翻轉寫入配置信息。Micro Blaze模塊中TCP/IP協議棧的建立則是基于開源代碼lwIP。

?

主控模塊狀態轉移如圖3.4所示。對FPGA的完整配置結束、復位釋放后,首先進行配置信息的回讀。此回讀操作是針對動態區,也就是待測模塊的。將待測模塊配置信息回讀后,數據將被存入片內存儲器Block RAM中。以上操作完成后即進入等待指令狀態,在此狀態下Micro Blaze處理器將接收來自上位機的TCP連接建立請求,當TCP連接建立后,即可接收來自上位機的TCP指令/數據包。上位機將產生的隨機數據打包成TCP數據包,FPGA接收到以后將動態區配置信息更改,達到設定的需要翻轉bit位后上位機將發送激勵產生指令,主控模塊收到后將激勵產生模塊使能打開,動態區開始工作,數據采集模塊開始對待測系統的輸出采樣,達到設定容量后這些采樣數據將被發回到上位機。FPGA模塊由此進入下一次指令等待狀態。

?

4.系統測試及結果分析

本文將RS編碼器的作為待測目標系統,對其進行可靠性評估,同時對該評估系統進行功能驗證。

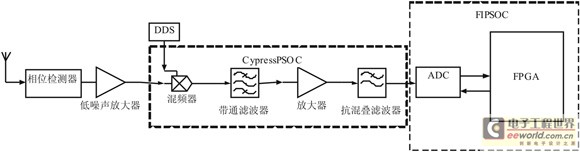

測試系統組成如圖4.1所示,包括運行軟件部分的上位機和實現硬件的XUP5VLX110T開發板,二者之間通過JTAG下載線、串口線和網線相連。JTAG下載線用于完整比特流的配置,串口線用于調試信息打印和Micro Blaze系統跟蹤,網線用于上位機和硬件平臺的通信。關于XUP5VLX110T開發板[上以太網硬件環境本文不做贅述,感興趣讀者可參見Xilinx公司的相關文檔。

?

4.1 系統資源占用情況

系統邏輯部分采用Verilog語言描述,在Xilinx大學計劃XUP5VLX110T開發板上得以實現。系統開發環境采用Xilinx公司的ISE14.3集成軟件開發環境。系統實現的資源占用情況如表4.1所示。

由上表可見,該系統本身占用資源少于40%,適合規模在資源占用率60%以下的待測系統進行可靠性測試。

4.2 系統測試數據

為了分析RS編碼器的可靠性,分別將RS編碼器、加入局部三模保護的RS編碼器、加入分布式三模保護的RS編碼器和加入全局三模保護的RS編碼器作為待測模塊,對各自的配置信息注入隨機的定量錯誤,收集編碼結果,并與正確的RS編碼器結果進行比較,給出可靠性報告。

測試系統對待測模塊進行三種類型的TMR加固保護,對包含無加固保護在內的四種目標系統分別執行了20000次錯誤注入實驗。三種TMR類型分別是局部三模冗余、分布式三模冗余和全局三模冗余。

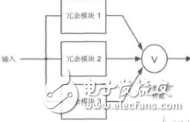

局部三模冗余(LTMR)是指將設計中的時序邏輯(包括觸發器、移位寄存器、塊RAM等)復制三份,并加入多數表決器來決定正確的輸出。如圖4.2所示。局部三模冗余中,三份觸發器共享輸入數據、控制信號和時鐘。

?

分布式三模冗余(DTMR)是指將設計中的時序邏輯、組合邏輯和表決器均復制三份,表決器位于時序邏輯之后,如圖4.3所示。但是,分布式三模冗余不對全局布線和I/O進行處理。

?

全局式三模冗余(GTMR)是指在分布式三模冗余的基礎上對時鐘布線以及全局寄存器進行三模處理,如圖4.4所示。

?

由于局部三模冗余僅對時序邏輯做三模處理,一旦組合邏輯的配置信息被打翻,僅靠觸發器等的復制無法保證電路功能的正確性。因此,較之于其余兩種三模冗余方法,局部三模冗余的保護力度略弱一些。其余兩種冗余措施組合邏輯和觸發器等均做了復制,那么無論三路電路中的任意一路中的組合邏輯出錯還是時序邏輯出錯,均可由表決器得到正確的結果,因此,分布式三模冗余和全局三模冗余的保護力度較大,全局三模冗余略勝一籌。

添加三模冗余加固依靠Mentor Graphics 公司的Precision(2011a,update2.76)工具,它是為現有可編程器件(CPLD和FPGA)以及下一代大規模可編程片上系統(FPSoC)設計的專用綜合工具。支持RTL級的邏輯綜合,可實現基于約束的優化,并可給出時序分析,同時還可實現布局布線。其自動添加三模冗余的功能被業界普遍采用。實驗采用Precision 套件的Hi-Re版本對RS編碼器分別進行局部三模保護、分布式三模保護以及全局三模保護。占用資源情況如表4.2所示。其中可用一列顯示當前設定的動態區中可用的資源情況。由資源占用情況可見,全局三模冗余的資源占用比例最大。

實驗中選取對上述四種待測模塊進行大量測試,針對每種待測模塊,設定循環次數為2000次,每次隨機注入N(N取1到10)比特翻轉信息,并對單次測試結果進行統計,并給出測試報告。表4.3為由測試報告中獲取的編碼故障率(編碼正確的次數/2000次)信息。

?

4.3 系統測試結果分析

通過分析表4.3可以得到以下結論:

(1) 與加入冗余保護的RS編碼器相比,未加冗余保護的RS編碼器可靠性較差,因此三模冗余可有效提高編碼器的可靠性;

(2) 分布式三模冗余與全局三模冗余的保護效果較好,全局三模冗余的可靠性略高一些,局部三模冗余的保護效果較差,這與三模冗余采用面積換取可靠性的原理相符;

(3) 每種保護措施下,隨著單次翻轉信息量的增加,正確率下降。

上述實驗結果與實際情況相符,充分說明了該平臺功能正確,且該平臺具有評估系統可靠性的能力,可應用于實際任務中。

電子發燒友App

電子發燒友App

評論