根據(jù)BPSK調(diào)制信號(hào)調(diào)制機(jī)理和平方倍頻法原理,在FPGA平臺(tái)上設(shè)計(jì)實(shí)現(xiàn)了BPSK調(diào)制信號(hào)載波頻率估計(jì)單元。

2014-09-01 11:26:40 2585

2585 簡(jiǎn)化采用BPSK(二進(jìn)制相移鍵控)和差分BPSK調(diào)制(也稱(chēng)為PRK,相位反轉(zhuǎn)鍵控或2PSK)的傳輸(transmit-only)解決方案設(shè)計(jì)。

2019-09-21 08:46:00 6031

6031

電平兩個(gè)邏輯量1和0,所以調(diào)制的過(guò)程可用鍵控的方法由基帶信號(hào)對(duì)載頻信號(hào)的振幅、頻率及相位進(jìn)行調(diào)制,最基本的方法有3種:正交幅度調(diào)制(QAM)、頻移鍵控(FSK)、相移鍵控(PSK).根據(jù)所處理的基帶信號(hào)

2020-07-23 17:21:34 769

769

在學(xué)習(xí)labview,想實(shí)現(xiàn)BPSK的仿真,不知道如何實(shí)現(xiàn),希望各位大神能指點(diǎn)一二,必有重謝。

2017-05-04 17:56:11

模擬信號(hào)而是數(shù)字信號(hào)。 在大多數(shù)情況下,數(shù)字調(diào)制是利用數(shù)字信號(hào)的離散值去鍵控載波。對(duì)載波的幅度、頻率或相位進(jìn)行鍵控,便可獲得ASK、FSK、PSK等。這三種數(shù)字調(diào)制方式在抗干擾噪聲能力和信號(hào)頻譜利用率

2008-10-21 11:48:21

基于MCU、定制ASIC和體積龐大的電線束來(lái)實(shí)現(xiàn)引擎及控制電子的系統(tǒng)方案已發(fā)展至接近其技術(shù)和應(yīng)用極限,汽車(chē)工業(yè)正面臨新的設(shè)計(jì)挑戰(zhàn),本文介紹FPGA在賽車(chē)引擎控制單元中的應(yīng)用,幫助設(shè)計(jì)人員緩解產(chǎn)品更快推出市場(chǎng)的壓力、減少元件數(shù)目、在單一硬件平臺(tái)上實(shí)施標(biāo)準(zhǔn)化以及滿(mǎn)足不斷升級(jí)的安全要求。

2019-10-17 08:34:30

可現(xiàn)在遇到一個(gè)問(wèn)題,系統(tǒng)的晶振是40M,可我需要一個(gè)160M的輸出信號(hào),怎么才能在FPGA內(nèi)部實(shí)現(xiàn)倍頻呢?我看了它的說(shuō)明書(shū),上面說(shuō)可以實(shí)現(xiàn)倍頻,有PLL功能可是卻沒(méi)有具體的說(shuō)明怎么實(shí)現(xiàn)倍頻,用什么方法實(shí)現(xiàn),能實(shí)現(xiàn)多少倍頻?用軟件實(shí)現(xiàn),還是硬件實(shí)現(xiàn)?不知道大俠們是怎么實(shí)現(xiàn)倍頻的,能否告知一二?

2013-12-04 22:31:39

請(qǐng)問(wèn),用fpga輸出方波信號(hào)作為調(diào)制信號(hào)時(shí),輸出高電平電壓一般為多少。一片FPGA板子最多可以同時(shí)輸出多少路調(diào)制信號(hào)?謝謝回復(fù)!

2017-05-03 15:00:05

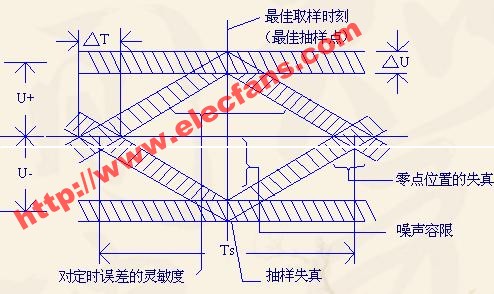

本文介紹了一種在DSP平臺(tái)下對(duì)多路交流信號(hào)采樣時(shí)采用的一種異步采樣方法。

2021-04-02 07:01:30

HMC874LC3C的CLK引腳可以輸入正弦波BPSK調(diào)制信號(hào)嗎?

2023-11-16 07:28:16

uclinux在Blackfin平臺(tái)下的移植設(shè)計(jì)

2013-06-03 20:52:16

∑-△調(diào)制頻率合成器及其實(shí)現(xiàn)∑-△調(diào)制器原理設(shè)計(jì)∑-△調(diào)制器的FPGA實(shí)現(xiàn)

2021-04-15 06:47:14

本文系統(tǒng)的介紹了ARM基于Linux平臺(tái)下的FPGA的驅(qū)動(dòng)開(kāi)發(fā)方法。

2021-05-07 06:04:20

率估計(jì)法(Kay法)比較具有代表性,它在高信噪比條件下可達(dá)到Cramer-Rao界(CRB),并且運(yùn)算量不大,適于硬件實(shí)現(xiàn)。本文以Kay頻率估計(jì)法為基礎(chǔ)構(gòu)建了一種適用于脈沖信號(hào)的載波頻率同步環(huán),并通過(guò)計(jì)算機(jī)仿真和FPGA實(shí)現(xiàn)來(lái)驗(yàn)證其有效性。

2023-09-20 08:28:04

在傳統(tǒng)的數(shù)字通信系統(tǒng)中,接收機(jī)的解調(diào)單元都是用模擬處理的方法和器件實(shí)現(xiàn)的。但是隨著高集成度芯片技術(shù)的發(fā)展,全數(shù)字調(diào)制解調(diào)方案不僅實(shí)現(xiàn)與調(diào)試方便,集成度和可靠性高,且成本低,體現(xiàn)了現(xiàn)代通信系統(tǒng)

2021-07-27 06:38:51

各位前輩們,對(duì)于BPSK調(diào)制信號(hào),什么類(lèi)型的功放比較合適呢,現(xiàn)在我用的是TDA7492這款D類(lèi)功放,但沒(méi)有輸出,誰(shuí)用過(guò)這類(lèi)功放嗎?請(qǐng)出來(lái)討論一下,謝謝了

2016-11-16 22:55:32

bpsk調(diào)制的詳細(xì)介紹

2013-04-12 09:59:49

。大規(guī)模可編程邏輯器件FPGA在處理速度和集成度等方面發(fā)展很快,用戶(hù)可自定義邏輯功能、可重復(fù)編程,同時(shí)FPGA還具有成本低、使用靈活方便等優(yōu)點(diǎn),在雷達(dá)信號(hào)處理硬件實(shí)現(xiàn)中得到廣泛的應(yīng)用。由于雷達(dá)信號(hào)處理

2015-02-05 15:34:43

基于至簡(jiǎn)設(shè)計(jì)法實(shí)現(xiàn)的PWM調(diào)制verilog

2017-09-27 09:53:33

明德?lián)P分享的調(diào)制PWM驅(qū)動(dòng)LED工程,利用脈沖寬度調(diào)制調(diào)制出幾個(gè)不同寬度的脈沖來(lái)驅(qū)動(dòng)LED燈,添加verilog文件即可使用。基于至簡(jiǎn)設(shè)計(jì)法實(shí)現(xiàn)的PWM調(diào)制verilog.rar (281.92 KB )

2019-01-18 06:35:18

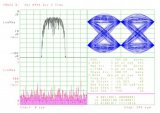

結(jié)合Labview平臺(tái)的圖形化特點(diǎn),高效地實(shí)現(xiàn)對(duì)PSK及QAM類(lèi)調(diào)制信號(hào)的解調(diào)分析。以BPSK、8PSK及16QAM、32QAM為代表的信號(hào),通過(guò)該軟件進(jìn)行處理所得的I/Q星座圖及EVM Rms

2019-04-12 09:40:08

與N5102A Baseband Studio數(shù)字信號(hào)接口模塊結(jié)合使用時(shí),E4438C ESG如何提供已校準(zhǔn)的數(shù)字IQ和數(shù)字中頻測(cè)試信號(hào),需要怎樣設(shè)置?如:如何產(chǎn)生BPSK調(diào)制信號(hào)?使用N5102A

2019-08-02 11:11:29

在LabVIEW平臺(tái)下實(shí)現(xiàn)算法加速,傳統(tǒng)的邊緣提取和粒子分析以及預(yù)處理算法都比較耗時(shí)間,采用FPGA來(lái)加速圖像處理的時(shí)間將會(huì)大大的縮減,比傳統(tǒng)的PC端的速度將會(huì)大大縮減!可以動(dòng)態(tài)監(jiān)測(cè)高速運(yùn)動(dòng)的物體!分享一個(gè)鏈接是視覺(jué)加速的案例http://www.mangotree.cn/event/32338/

2016-12-28 10:15:44

如何在LabVIEW平臺(tái)下設(shè)計(jì)應(yīng)變測(cè)量系統(tǒng)?LabVIEW在測(cè)試測(cè)量領(lǐng)域有什么優(yōu)勢(shì)?

2021-04-12 06:32:17

本文將介紹線路調(diào)制的FPGA實(shí)現(xiàn),包括:線路調(diào)制單元數(shù)字化實(shí)現(xiàn)的總體設(shè)計(jì),CIC和FIR濾波器的FPGA實(shí)現(xiàn)以及載波發(fā)生器單元的設(shè)計(jì)。

2021-04-29 06:41:28

本文設(shè)計(jì)了一個(gè)基于FPGA 的直接序列擴(kuò)頻系統(tǒng)的水聲通信調(diào)制/解調(diào)系統(tǒng),目的在于使水聲無(wú)線通信中具有更強(qiáng)的抗干擾性和保密性,系統(tǒng)中包含了信號(hào)的擴(kuò)頻及BPSK 調(diào)制以及相應(yīng)的解調(diào)模塊,并且在Modelsim 仿真軟件上驗(yàn)證成功。

2021-06-03 06:25:41

QPSK調(diào)制的基本原理QPSK調(diào)制電路的FPGA實(shí)現(xiàn)

2021-04-08 06:01:29

本文設(shè)計(jì)了一個(gè)基于FPGA 的直接序列擴(kuò)頻系統(tǒng)的水聲通信調(diào)制/解調(diào)系統(tǒng),目的在于使水聲無(wú)線通信中具有更強(qiáng)的抗干擾性和保密性,系統(tǒng)中包含了信號(hào)的擴(kuò)頻及BPSK 調(diào)制以及相應(yīng)的解調(diào)模塊,并且在Modelsim 仿真軟件上驗(yàn)證成功。

2021-05-24 06:41:18

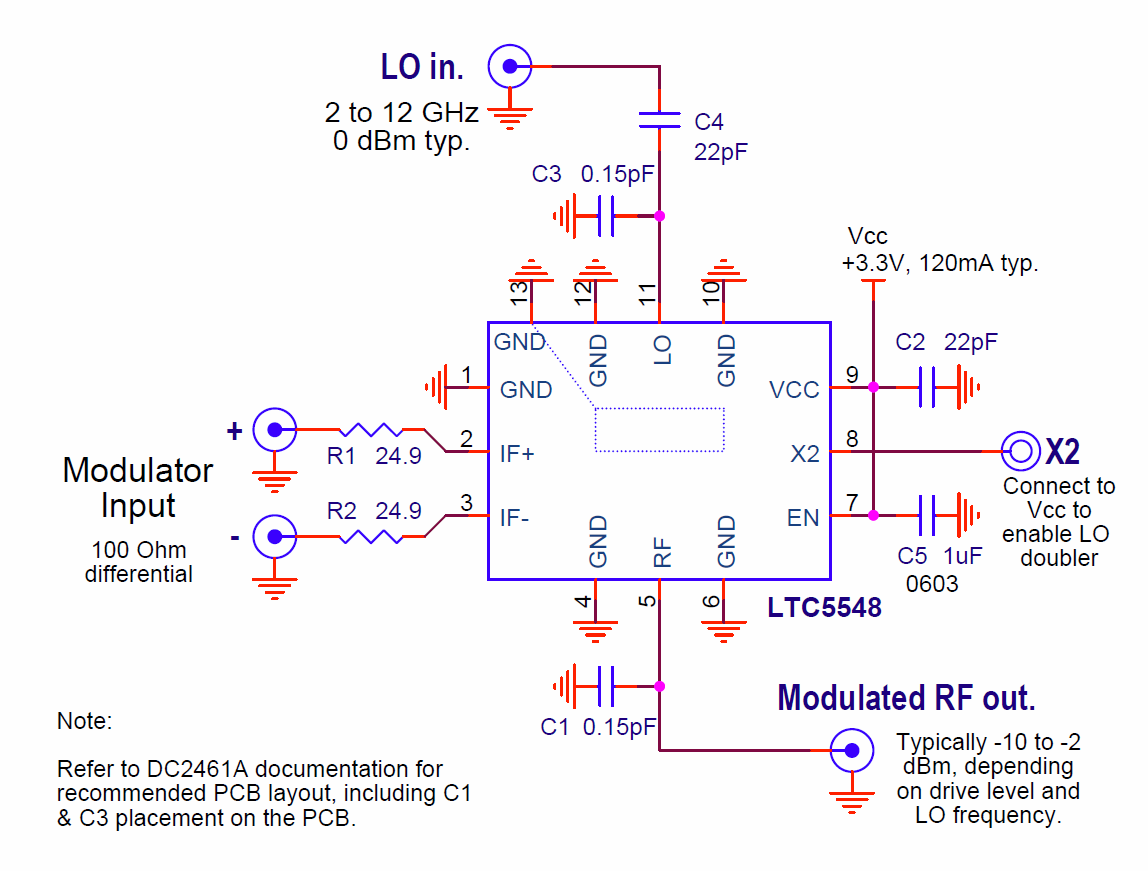

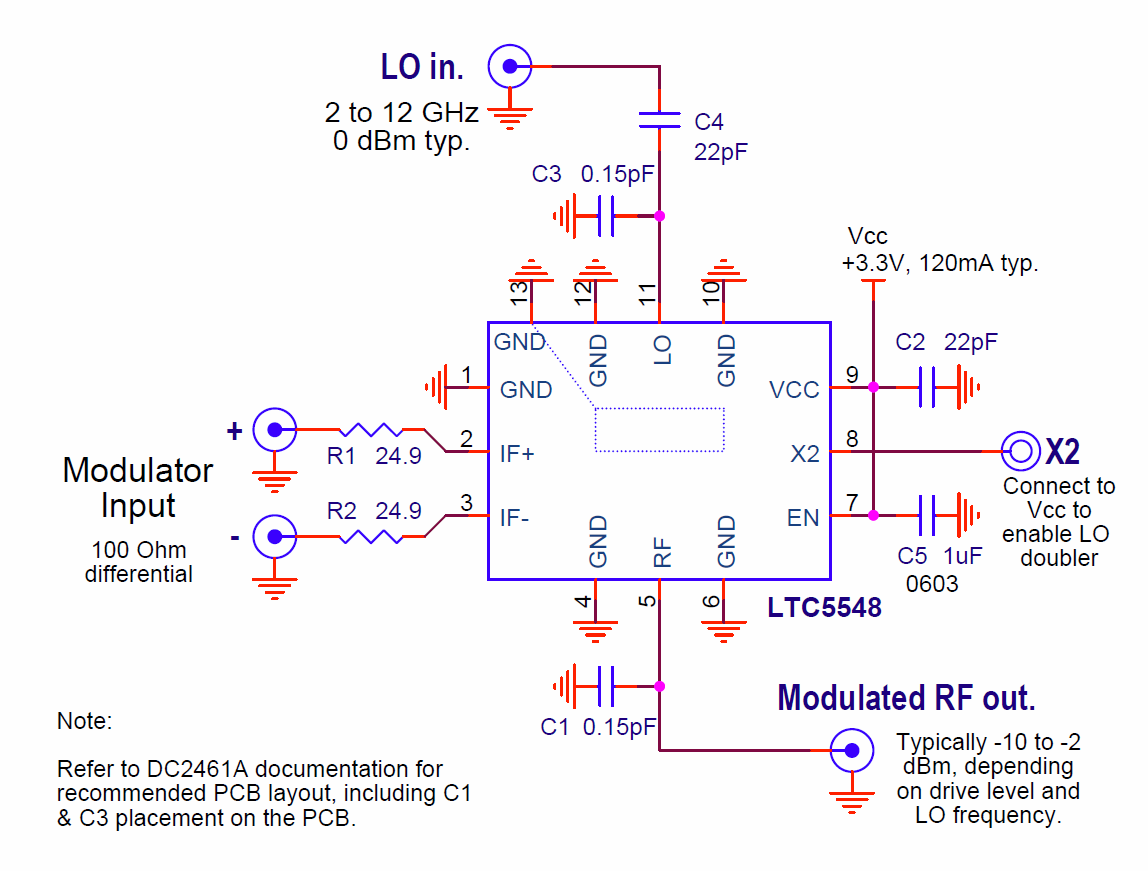

想要產(chǎn)生一個(gè)BPSK的調(diào)制信號(hào),載波900MHz,基帶用FPGA產(chǎn)生,建議用什么DDS芯片呢?有沒(méi)有好的推薦電路呢?

2018-11-09 09:15:35

Labview萌新求救:下圖是使用Labview設(shè)計(jì)好的窄帶FM調(diào)制模塊,請(qǐng)問(wèn)如何使用倍頻后再混頻的方法生成寬帶FM信號(hào)呢?(原理已懂,卡在了倍頻器的部分,不知怎么實(shí)現(xiàn)倍頻操作):

2019-04-13 22:16:04

最近在做個(gè)課題,需要用FPGA中的verilog語(yǔ)言實(shí)現(xiàn)BPSK調(diào)制,fpga不是很會(huì),望大神指導(dǎo)下,急求代碼啊!謝謝

2013-03-06 18:12:36

畢業(yè)設(shè)計(jì)作死自定了一個(gè)題目:基于FPGA的調(diào)制識(shí)別系統(tǒng)設(shè)計(jì)用fpga識(shí)別AM,Dpsk,CPFSK信號(hào)然后調(diào)用解調(diào)模塊解調(diào),目前寫(xiě)出了調(diào)制部分,識(shí)別部分網(wǎng)上論文都太籠統(tǒng),不太容易實(shí)現(xiàn),求助各位網(wǎng)友推薦一下類(lèi)似的處理辦法,壓上全部家當(dāng)

2018-04-25 18:12:44

求助FM調(diào)制器的FPGA實(shí)現(xiàn),對(duì)FPGA這些完全不了解,在網(wǎng)上看可以用DDS技術(shù)實(shí)現(xiàn)FM的數(shù)字調(diào)制,就在書(shū)上按照步驟先做了產(chǎn)生正弦波分頻模塊尋址模塊數(shù)據(jù)存儲(chǔ)模塊,但編譯不能通過(guò),也不知道該怎樣進(jìn)行頻率調(diào)制,請(qǐng)問(wèn)該怎樣實(shí)現(xiàn)頻率的調(diào)制,請(qǐng)問(wèn)有人寫(xiě)過(guò)頻率調(diào)制的verilog代碼嗎,急求,謝謝

2019-03-16 11:43:26

haas平臺(tái)下的開(kāi)發(fā)板。所使用的固件都是阿里云提供的?還是怎么樣?

2021-12-22 00:29:35

想要產(chǎn)生一個(gè)BPSK的調(diào)制信號(hào),載波900MHz,基帶用FPGA產(chǎn)生,建議用什么DDS芯片呢?

2018-11-13 09:19:42

能否在 Lab VIEW 平臺(tái)下編寫(xiě)改進(jìn)后的 EMD 算法,采集到信號(hào)后直接進(jìn)行分析?怎么進(jìn)行改進(jìn)?

2019-10-09 16:15:12

1. 為什么要使用FPGA實(shí)現(xiàn)在全控型電力電子開(kāi)關(guān)器件出現(xiàn)以后,為了改善交流電動(dòng)機(jī)變壓變頻調(diào)速系統(tǒng)的性能,科技工作者在20世紀(jì)80年代開(kāi)發(fā)出了應(yīng)用脈寬調(diào)制(PWM)技術(shù)的變壓變頻器,由于它的優(yōu)良

2022-01-20 09:34:26

【摘要】針對(duì)以往DOA估計(jì)算法中智能天線系統(tǒng)的陣列單元模型多采用全向振子的情況,分析了當(dāng)天線單元存在方向性時(shí)對(duì)MUSIC算法估計(jì)信號(hào)到達(dá)角的影響,并在進(jìn)行陣元互耦校正后

2009-03-14 15:12:51 18

18 GMSK(高斯最小移頻鍵控)信號(hào)優(yōu)良的頻譜特性在跳頻通信中有廣闊的應(yīng)用前景。本文分析了GMSK 調(diào)制器的設(shè)計(jì)理論,給出了一種全數(shù)字實(shí)現(xiàn)結(jié)構(gòu)并在FPGA 上加以實(shí)現(xiàn)。仿真結(jié)果表明,

2009-08-13 14:48:05 56

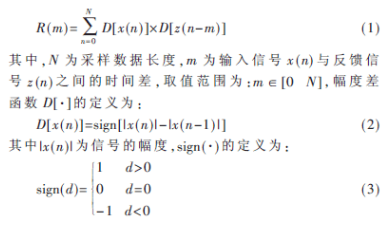

56 非合作水聲低載噪比直接序列擴(kuò)頻信號(hào)的載頻估計(jì)方法:在非合作條件下,該文針對(duì)水聲直接序列二相調(diào)制擴(kuò)頻信號(hào)的載頻估計(jì),提出了一種在載噪比較低和信號(hào)產(chǎn)生較大畸變情況下

2009-10-29 12:55:43 9

9 目前盲分離研究已有算法眾多,但有關(guān)數(shù)字信號(hào)或有限字符集的盲分離研究尚不多見(jiàn),而帶源個(gè)數(shù)估計(jì)的此類(lèi)盲分離算法更鮮有涉及。針對(duì)這類(lèi)問(wèn)題,該文提出了一種新穎的BPSK 數(shù)字

2009-11-13 14:38:10 20

20 雙基地多載頻FMCW 雷達(dá)采用稀布陣發(fā)射多載頻FMCW(Frequency Modulated Continuous Wave)信號(hào),陣列接收目標(biāo)回波。受速度和加速度的調(diào)制,機(jī)動(dòng)目標(biāo)回波多普勒頻譜展寬,導(dǎo)致雷達(dá)檢測(cè)性能下

2009-11-20 15:58:47 21

21 本文將介紹線路調(diào)制的FPGA 實(shí)現(xiàn),包括:線路調(diào)制單元數(shù)字化實(shí)現(xiàn)的總體設(shè)計(jì),CIC 和FIR 濾波器的FPGA 實(shí)現(xiàn)以及載波發(fā)生器單元的設(shè)計(jì)。

2009-11-30 14:08:33 18

18 提出了一種基于FPGA 實(shí)現(xiàn)QPSK 調(diào)制器的方法。以FPGA 實(shí)現(xiàn)DDS,通過(guò)對(duì)DDS 信號(hào)輸出相位的控制實(shí)現(xiàn)調(diào)相。仿真結(jié)果表明方案是可行的。

2009-12-18 11:57:08 66

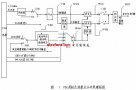

66 介紹一種全數(shù)字BPSK 解調(diào)器的設(shè)計(jì)及FPGA 實(shí)現(xiàn)。該解調(diào)器采用前向開(kāi)環(huán)的結(jié)構(gòu)實(shí)現(xiàn)載波同步,與傳統(tǒng)的閉環(huán)反饋結(jié)構(gòu)相比,該解調(diào)器具有同步速度快,載波頻差估計(jì)范圍大等優(yōu)點(diǎn),

2009-12-19 15:57:36 52

52 該文針對(duì)混合DS/FH_BPSK 信號(hào)的參數(shù)估計(jì)問(wèn)題,提出了一種結(jié)合譜增強(qiáng)與時(shí)頻分析的精確跳速估計(jì)方法。該方法首先利用非線性變換獲得攜帶跳速信息的參考信號(hào),并利用循環(huán)譜預(yù)估計(jì)

2010-02-08 16:02:43 11

11 正弦調(diào)制相位信號(hào)是微動(dòng)目標(biāo)雷達(dá)回波微多普勒信號(hào)的一般形式。該文利用正弦調(diào)制相位信號(hào)的循環(huán)平穩(wěn)特性推導(dǎo)了信號(hào)的循環(huán)譜,并由循環(huán)譜特征估計(jì)信號(hào)的參數(shù)。相對(duì)于傳統(tǒng)的

2010-02-09 11:24:27 16

16 介紹一種全數(shù)字BPSK解調(diào)器的設(shè)計(jì)及FPGA實(shí)現(xiàn)。該解調(diào)器采用前向開(kāi)環(huán)的結(jié)構(gòu)實(shí)現(xiàn)載波同步,與傳統(tǒng)的閉環(huán)反饋結(jié)構(gòu)相比,該解調(diào)器具有同步速度快,載波頻差估計(jì)范圍大等優(yōu)點(diǎn),尤其適合

2010-07-21 17:34:19 47

47 什么是BPSK?

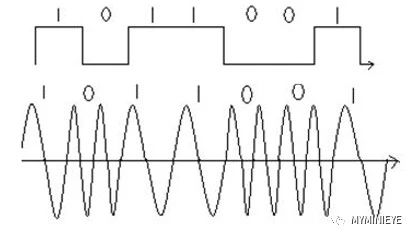

BPSK的英文名稱(chēng) : Binary Phase Shift Keying

BPSK的介紹:

2008-10-21 11:42:59 26673

26673

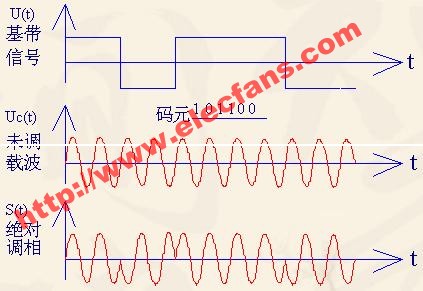

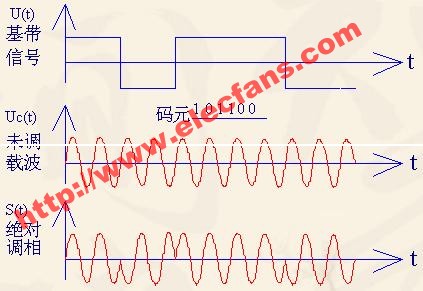

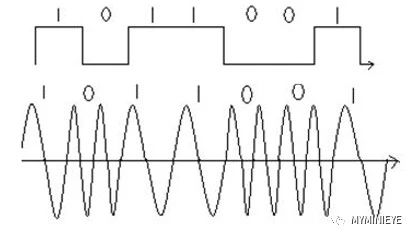

bpsk調(diào)制原理

與模擬通信系統(tǒng)相比,數(shù)字調(diào)制和解調(diào)同樣是通過(guò)某種方式,將基帶信號(hào)的頻譜由一個(gè)頻率位置搬移到另一個(gè)頻率位置上

2008-10-21 12:29:56 30384

30384

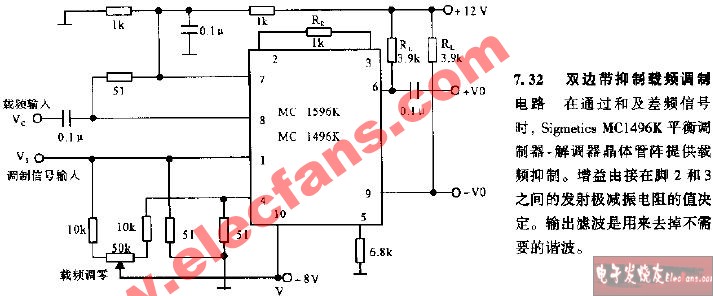

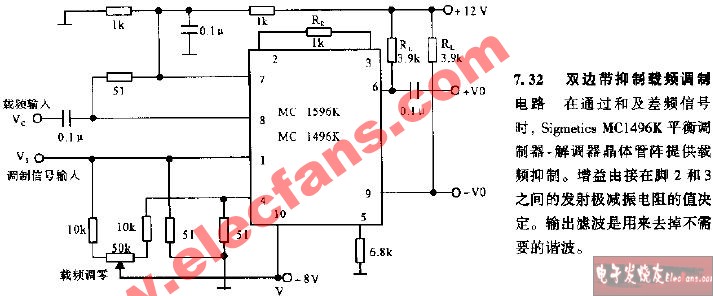

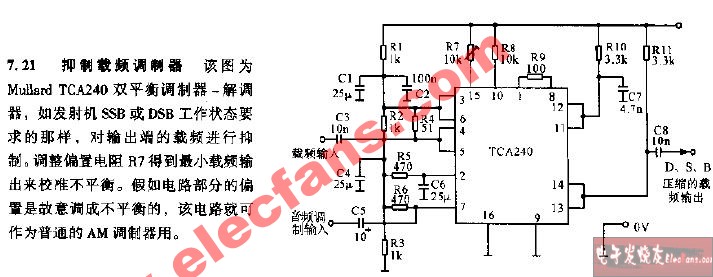

雙邊帶抑制載頻調(diào)制電路

2009-03-20 20:13:54 711

711

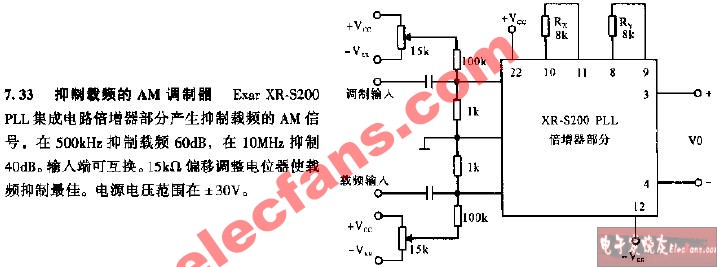

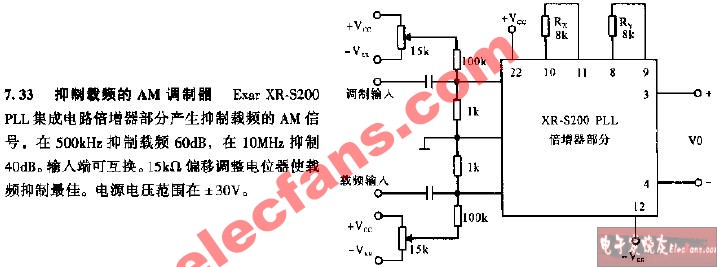

抑制載頻的AM調(diào)制器電路

2009-03-20 20:14:39 610

610

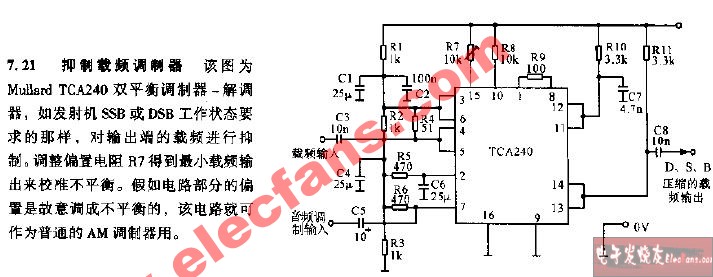

抑制載頻調(diào)制器電路

2009-03-20 20:15:26 386

386

6kV·A逆變器滯環(huán)調(diào)制與單極性SPWM倍頻調(diào)制的比較

分析了電流型滯環(huán)調(diào)制和單極性SPWM倍頻調(diào)制逆變器的原理,然后討論了兩種調(diào)制方式下輸出濾波器的設(shè)計(jì),并在此基

2009-10-29 17:31:29 1736

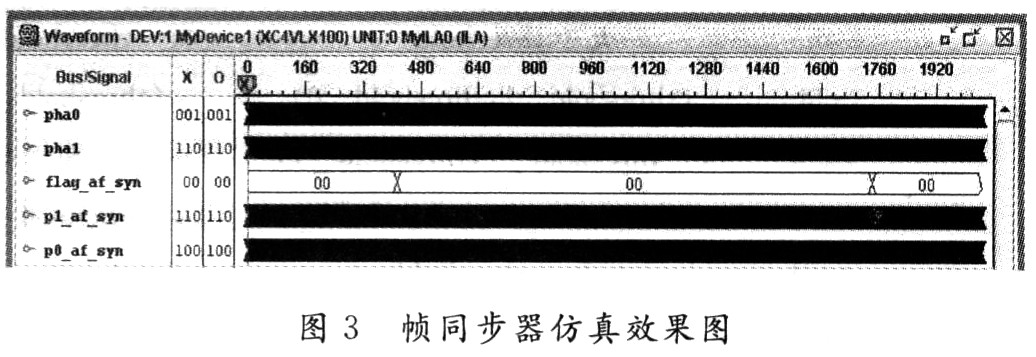

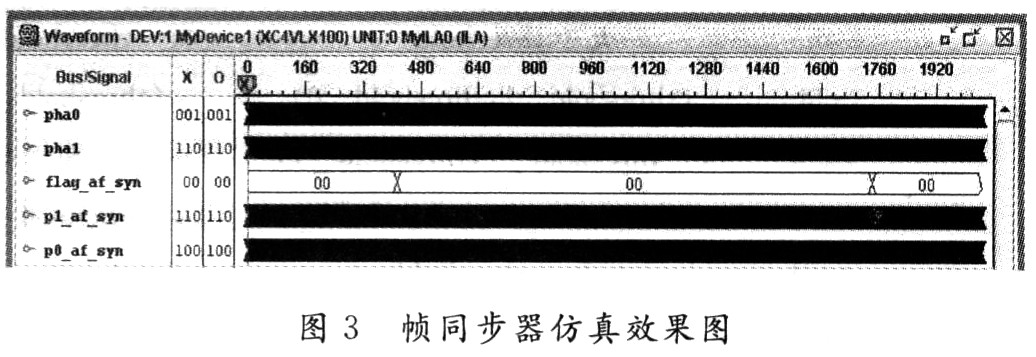

1736 一種高速幀同步和相位模糊估計(jì)的方法及其FPGA實(shí)現(xiàn)

摘要:提出僅依靠接收符號(hào)和本地同步碼快速確定MPSK調(diào)制符號(hào)的幀同步,并同時(shí)估計(jì)其相位模糊值的計(jì)算方法,給

2010-01-27 09:38:17 1278

1278

可獲得2倍頻率的平方電路(X2)

電路的功能

平方電路是進(jìn)行EO=X2運(yùn)

2010-05-08 16:30:23 1104

1104

二相BPSK (DPSK)調(diào)制解調(diào)技術(shù)有二相BPSK調(diào)制解調(diào)實(shí)驗(yàn),二相DPSK調(diào)制解調(diào)實(shí)驗(yàn),PSK解調(diào)載波提取實(shí)驗(yàn)

2011-03-15 22:41:43 15712

15712

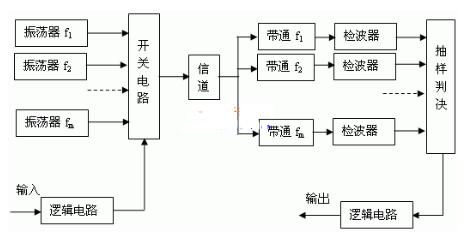

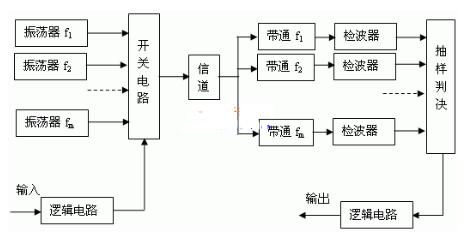

根據(jù)數(shù)字信號(hào)FSK調(diào)制和解調(diào)的工作原理,采用層次化、模塊化方法設(shè)計(jì)了一種基于FPGA 芯片的FSK調(diào)制解調(diào)器;用數(shù)字鍵控法實(shí)現(xiàn)了調(diào)制,用過(guò)零檢測(cè)法實(shí)現(xiàn)了全數(shù)字解調(diào)。同時(shí)結(jié)合系統(tǒng)

2011-08-26 15:25:48 114

114 針對(duì)MPSK信號(hào)載波頻率估計(jì)問(wèn)題,文中將譜線檢測(cè)理論與非線性變換思想相結(jié)合,提出了一種載波頻率快速估計(jì)算法。

2011-12-14 14:34:25 16

16 討論一種基于DSP系統(tǒng),利用FPGA設(shè)計(jì)接口通過(guò)DDS芯片產(chǎn)生MSK調(diào)制的方法,使用該方案的硬件電路簡(jiǎn)潔且易于實(shí)現(xiàn)調(diào)制器的小型化。

2012-02-09 15:14:46 11

11 基于FPGA的調(diào)制和解調(diào)的數(shù)字信號(hào)有多種,包括2ASK、2FSK、2PSK等,文中介紹了2FSK信號(hào)的調(diào)制與解調(diào),以及該信號(hào)的功率譜。最后提供驗(yàn)證結(jié)果,證明仿真結(jié)果符合要求。

2012-03-23 11:17:28 398

398 本文設(shè)計(jì)實(shí)現(xiàn)了一種新型的BPSK信號(hào)調(diào)制解調(diào)器,利用m序列的隨機(jī)性來(lái)產(chǎn)生輸入基帶信號(hào),詳細(xì)介紹了基于FPGA的BPSK信號(hào)調(diào)制解調(diào)器的設(shè)計(jì)方法,提供了VHDL源代碼在Quartus II環(huán)境下的仿真

2012-03-31 15:06:56 67

67 介紹了MSK信號(hào)的優(yōu)點(diǎn),并分析了其實(shí)現(xiàn)原理,提出一種MSK高性能數(shù)字調(diào)制器的FPGA實(shí)現(xiàn)方案;采用自頂向下的設(shè)計(jì)思想,將系統(tǒng)分成串/并變換器、差分編碼器、數(shù)控振蕩器、移相器、乘

2012-04-12 14:40:40 65

65 先利用信號(hào)的2階和4階循環(huán)累積量的特征,將MPSK信號(hào)分為BPSK和QPSK與8PSK以上兩大調(diào)制子類(lèi),再由信號(hào)循環(huán)頻率等于信號(hào)載頻處的2階和4階循環(huán)累積量,構(gòu)成BPSK和QPSK的分類(lèi)特征量,實(shí)現(xiàn)對(duì)BPSK和

2012-04-18 15:17:19 24

24 BPSK調(diào)制,介紹調(diào)制算法和數(shù)值計(jì)算,也可延伸至d_bpsk

2015-11-10 17:15:16 23

23 基于FPGA的三相SVPWM調(diào)制算法的實(shí)現(xiàn)。

2016-04-18 09:47:49 23

23 基于FPGA的全數(shù)字FQPSK調(diào)制器實(shí)現(xiàn)_楊峰

2017-03-19 11:38:26 2

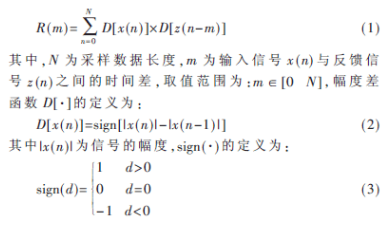

2 改進(jìn)的DSSS電磁波隨鉆測(cè)量信號(hào)載頻估計(jì)算法_蘇毅

2017-03-19 19:04:23 0

0 WinCE平臺(tái)下的CDMA信號(hào)測(cè)試系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

2017-10-25 09:45:10 4

4 數(shù)字調(diào)制信號(hào)又稱(chēng)為鍵控信號(hào), 其調(diào)制過(guò)程是用鍵控的方法由基帶信號(hào)對(duì)載頻信號(hào)的振幅、頻率及相位進(jìn)行調(diào)制。這種調(diào)制的最基本方法有三種: 振幅鍵控(ASK)、頻移鍵控(FSK)、相移鍵控(PSK), 同時(shí)

2017-10-30 16:45:00 4

4 要的參數(shù)之一,如果不能精確估計(jì)載波頻率,干擾信號(hào)就無(wú)法在頻域上對(duì)準(zhǔn)目標(biāo)信號(hào)。針對(duì)QPSK信號(hào)和16QAM信號(hào),主要有基于信號(hào)四次方功率譜和基于信號(hào)循環(huán)譜的載頻估計(jì)算法。基于四次方功率譜的載頻估計(jì)算法簡(jiǎn)單,計(jì)算量小,得

2017-11-09 15:25:55 25

25 本文設(shè)計(jì)并在FPGA芯片中實(shí)現(xiàn)了數(shù)字音頻廣播系統(tǒng)的信號(hào)調(diào)制系統(tǒng)。信號(hào)調(diào)制系統(tǒng)位于整個(gè)數(shù)字音頻廣播系統(tǒng)基帶信號(hào)處理鏈的末端,是基帶數(shù)字信號(hào)處理的核心系統(tǒng)。根據(jù)Eureka147標(biāo)準(zhǔn),信號(hào)調(diào)制系統(tǒng)需要

2017-11-22 15:25:01 3892

3892 二進(jìn)制相移鍵控(BPSK)也稱(chēng)為雙相調(diào)制,是一種簡(jiǎn)單的,流行的數(shù)字調(diào)制方案。 符號(hào)星座盡可能相距很遠(yuǎn),這對(duì)弱信號(hào)工作來(lái)說(shuō)是可取的。 BPSK因其相對(duì)簡(jiǎn)單的擴(kuò)頻能力而受歡迎。 因此,BPSK可以應(yīng)用于

2017-11-29 15:45:48 5396

5396

鑒于倍頻等長(zhǎng)信號(hào)具有重要研究?jī)r(jià)值,而其現(xiàn)有頻率估計(jì)方法存在嚴(yán)重不足,提出一種新型加權(quán)融合算法。首先,根據(jù)倍頻等長(zhǎng)信號(hào)間頻率的倍數(shù)生成倍頻修正矩陣,對(duì)倍頻等長(zhǎng)信號(hào)頻譜進(jìn)行同頻化處理,使之達(dá)到同頻等長(zhǎng)信號(hào)

2018-03-05 11:48:35 49

49 介紹一種全數(shù)字BPSK 解調(diào)器的設(shè)計(jì)及FPGA 實(shí)現(xiàn)。該解調(diào)器采用前向開(kāi)環(huán)的結(jié)構(gòu)實(shí)現(xiàn)載波同步,與傳統(tǒng)的閉環(huán)反饋結(jié)構(gòu)相比,該解調(diào)器具有同步速度快,載波頻差估計(jì)范圍大等優(yōu)點(diǎn),尤其適合用于突發(fā)數(shù)字通信系統(tǒng)

2018-12-13 17:56:49 14

14 基于FPGA芯片Stratix II EP2S60F672C4設(shè)計(jì)實(shí)現(xiàn)了數(shù)字基帶預(yù)失真系統(tǒng)中的環(huán)路延遲估計(jì)模塊。該模塊運(yùn)用了一種環(huán)路延遲估計(jì)新方法,易于FPGA實(shí)現(xiàn)。同時(shí),在信號(hào)失真的情況下也能給

2018-12-19 11:04:26 1477

1477

,利用波達(dá)方向矩陣法得到信號(hào)空間的原始基底,由此可進(jìn)一步同時(shí)獲得各子載波對(duì)應(yīng)用戶(hù)的波達(dá)方向(DOA)與載頻偏的閉式估計(jì).該方法支持任意子載波分配方案以及滿(mǎn)負(fù)載系統(tǒng),并且可根據(jù)當(dāng)前系統(tǒng)負(fù)載動(dòng)態(tài)調(diào)整估計(jì)復(fù)雜度.

2019-10-31 17:35:57 10

10 1、FSK信號(hào)的調(diào)制原理 數(shù)字頻率調(diào)制是利用載波的頻率傳輸信息的一種調(diào)制方式,F(xiàn)SK是在ASK之后出現(xiàn)的一種調(diào)制方式,抗衰落能力較強(qiáng),在一些衰落信道中應(yīng)用廣泛。 數(shù)字頻移鍵控(FSK)是用載波的頻率

2020-09-28 15:01:11 54015

54015

等相關(guān)技術(shù)的發(fā)展,較低碼率的BPSK在近距離無(wú)線產(chǎn)品中也得到了越來(lái)越廣泛的應(yīng)用。本文利用了MATLAB與FPGA實(shí)現(xiàn)了BPSK的信號(hào)調(diào)制。

2020-11-05 16:27:14 23

23 一種基于FPGA的MSK調(diào)制器設(shè)計(jì)與實(shí)現(xiàn)說(shuō)明。

2021-04-27 14:08:41 22

22 二進(jìn)制相移鍵控(BPSK),也稱(chēng)為雙相調(diào)制,是一種簡(jiǎn)單、流行的數(shù)字調(diào)制方案。符號(hào)星座盡可能遠(yuǎn),這對(duì)于弱信號(hào)工作是可取的。BPSK還因其相對(duì)簡(jiǎn)單的頻譜擴(kuò)展能力而廣受歡迎。因此,BPSK在弱信號(hào)通信、擴(kuò)頻、測(cè)距和雷達(dá)系統(tǒng)中都有應(yīng)用。

2023-01-04 14:39:02 1226

1226

一種基于FPGA 實(shí)現(xiàn)的800G信號(hào)處理平臺(tái)

2023-07-31 10:23:11 375

375

數(shù)字電路如何實(shí)現(xiàn)倍頻?? 數(shù)字電路是由數(shù)字電子器件以及邏輯門(mén)電路組成,可以用于處理數(shù)字信號(hào)或數(shù)字?jǐn)?shù)據(jù)。其中最基本的電子器件有晶體管、二極管等,而邏輯門(mén)電路包括了與門(mén)、或門(mén)、非門(mén)、異或門(mén)等。在數(shù)

2023-09-18 10:37:43 3084

3084 電子發(fā)燒友網(wǎng)站提供《基于FPGA的OFDM調(diào)制器設(shè)計(jì)與實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-26 09:25:59 0

0 如何具體實(shí)現(xiàn)輸出信號(hào)的分頻和倍頻? 在現(xiàn)代電子系統(tǒng)中,信號(hào)分頻和倍頻是非常常見(jiàn)的技術(shù)。它們可以幫助電子設(shè)備在處理信號(hào)時(shí)具有更高的精度和準(zhǔn)確性。下面我將詳細(xì)介紹如何實(shí)現(xiàn)輸出信號(hào)的分頻和倍頻。 一、分頻

2023-10-31 10:33:21 1270

1270

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論