為了實現激光-水聲淺海地形遙感探測中水聲信號的實時解調與處理,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結合

2013-10-29 10:10:02 2157

2157

隨著科技的飛速發展,集成化信息化信號采集處理系統在各個領域的應用越來越廣泛。這種系統能夠實現對各種信號的實時采集、處理和分析,為決策者提供準確、及時的信息,從而推動各行業的快速發展。本文將對集成化

2023-12-14 11:19:17 361

361 生產中的應用日益增加,不論是材料、工業自動化、遙感技術,還是產品質檢都需要對形狀進行檢測。因此,開發集圖像信號的采集與處理于一體、具有高集成度、高保密性的圖像處理系統將成為行業的發展趨勢。此外

2018-10-31 16:54:52

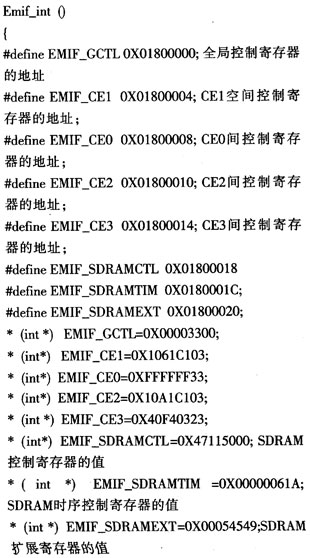

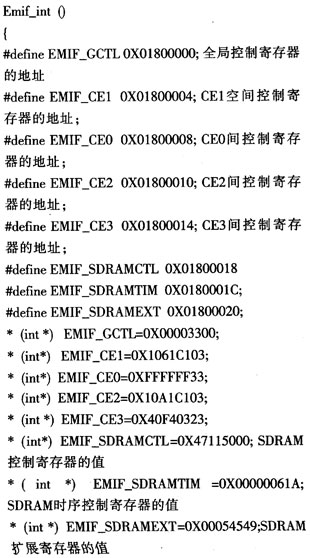

信號處理模塊各部分的功能及其穩定性,并設計測試程序,通過利用DSP讀取FPGA內部構建的異步FIFO中存儲的波形數據,驗證系統通信方案的可行性。

2015-11-06 09:55:43

核心控制單元并完成視頻信號的中值濾波工作;以DSP作為整個系統的核心處理單元對采集的視頻圖像信息進行JPEG壓縮;在視頻傳輸單元設計了以PDIUSBD12芯片為基礎的USB總線,負責視頻信號的傳輸。

2019-07-01 07:38:06

越來越力不從心。 以FPGA為代表的可編程邏輯器件以其工作穩定、速度快、靈活的可編程能力等特點,獲得了越來越廣泛應用。本文提出了一種基于FPGA的振動信號采集處理系統;該系統具有實時性高,糾錯能力強等

2019-07-01 06:11:15

單片FPGA圖像預處理系統的設計與實現采用單片FPGA設計與實現圖像處理系統的方法,并對系統硬件進行了分析和設計,對FPGA內電路模塊進行了VHDL建模,在FPGA開發平臺ISE4.1上實現了

2009-09-19 09:26:14

。 整個系統以FPGA作為核心控制單元并完成視頻信號的中值濾波工作;以DSP作為整個系統的核心處理單元對采集的視頻圖像信息進行JPEG壓縮;在視頻傳輸單元設計了以PDIUSBD12芯片為基礎的USB總線,負責視頻信號的傳輸。

2019-06-28 08:10:26

圖像數據處理的工作原理是什么?基于FPGA+DSP的圖像處理系統待如何去設計?

2021-06-02 06:54:28

。 整個系統以FPGA作為核心控制單元并完成視頻信號的中值濾波工作;以DSP作為整個系統的核心處理單元對采集的視頻圖像信息進行JPEG壓縮;在視頻傳輸單元設計了以PDIUSBD12芯片為基礎的USB總線,負責視頻信號的傳輸。

2019-06-19 06:12:05

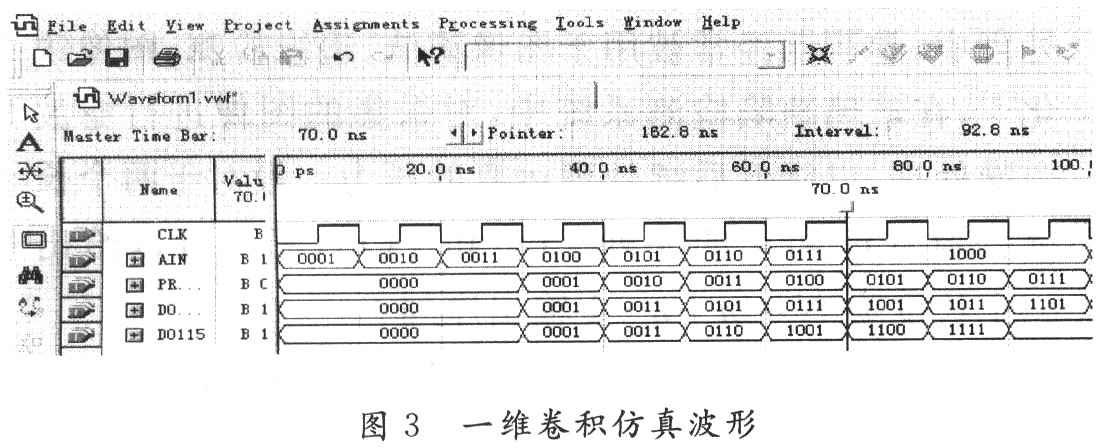

FIFO,最后由FPGA和PCI9656聯合將數據傳輸到CPCI總線,完成串行信號的處理。6 結語本文介紹了一種基于PFGA的多DSP并行處理系統的設計,重點對DSP并行結構設計進行了分析,并介紹了

2019-05-21 05:00:19

的信號量特別多時(特別是各種信號量、狀態量),僅僅靠用普通MCU的資源就往往難以完成任務。電子論壇所提出的一種基于FPGA的模擬量、數字量采集與處理系統,利用FPGA的I/O端口多,并且可以自由編程支配

2011-08-23 10:15:34

本帖最后由 lee_st 于 2017-10-31 08:26 編輯

基于FPGA的視頻圖像處理系統

2017-10-30 17:26:16

基于FPGA的視頻圖像處理系統

2015-05-27 20:34:49

基于FPGA的視頻圖像處理系統。

2015-05-23 12:18:23

基于fpga的實時視頻處理系統難點在哪,解決方案,誰能幫下忙

2014-04-08 19:03:45

基于DSP的圖像處理系統的應用研究摘要 本文介紹了一種基于FPGA+DSP結構的具有通用性、可擴充性的高速數字圖像處理系統硬件平臺。重點介紹了以高速數字信號處理器TMS320DM642

2012-12-19 11:05:08

基于LabVIEW的數據采集與信號處理系統設計

2013-04-26 17:29:19

各位燒友,,有沒有關于 基于labview語音信號處理系統的資料呢!!跪求啊!!!在此先謝過!676248796@qq.com

2012-10-20 09:39:36

數據采集處理系統的硬件設計數據采集處理系統的軟件設計

2021-05-27 06:05:33

如何在嵌入式視頻處理系統領域進行FPGA驗證?需要滿足什么條件?

2019-08-01 06:42:45

工作。光柵傳感技術的發展為檢波器的設計提供了有力的手段。其光柵信號處理技術仍局限于低速度的信號處理,雖然測量精度較高,但其動態特性難以滿足振動信號檢測等高速變化信號的處理要求,設計光柵地震檢波器的信號處理系統勢在必行,但具體該怎么做呢?

2019-08-08 08:21:56

嵌入式視頻處理系統領域的FPGA驗證,不看肯定后悔

2021-05-07 06:18:27

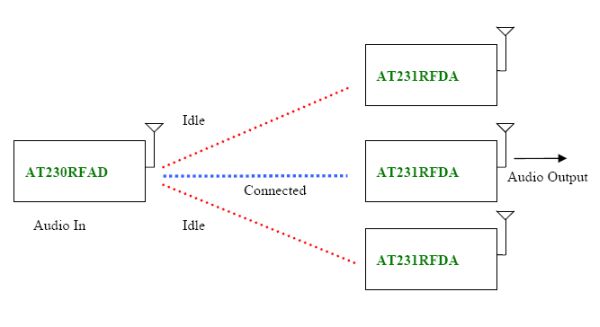

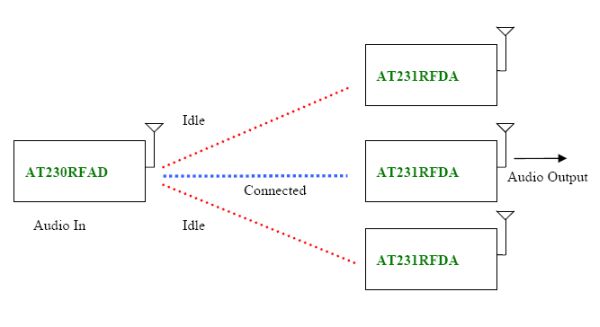

本文闡述了基于信號處理和嵌入式應用的音頻處理系統的設計和實現。

2021-06-08 07:07:19

本文設計了一套基于DSP的陣列聲波信號采集與處理系統,此系統將作為正在研制的陣列聲波測井儀中的一部分,應用于油田勘探中。

2021-05-31 06:26:35

有償求一份Xilinx的FPGA的圖像采集和處理系統的代碼,最好是你曾經做過的,別處下來的不能跑的不要。要能在開發板上跑動,我想做二次開發。聯系企鵝:39 6 5 8 1 2 7 2{:23:}

2014-04-14 15:20:03

數據采集與處理系統的硬件結構是由哪些構成的?數據采集與處理系統的軟件是怎樣設計的?

2021-04-22 06:16:51

怎樣去設計音頻信號采集與處理系統的硬件電路?怎樣去設計音頻信號采集與處理系統的軟件程序?

2021-06-08 06:51:40

為什么要設計激光多譜勒信號處理系統?激光多譜勒信號處理系統有哪些優點?怎樣去設計激光多譜勒信號處理系統?如何去驗證激光多譜勒信號處理系統?

2021-04-15 06:25:40

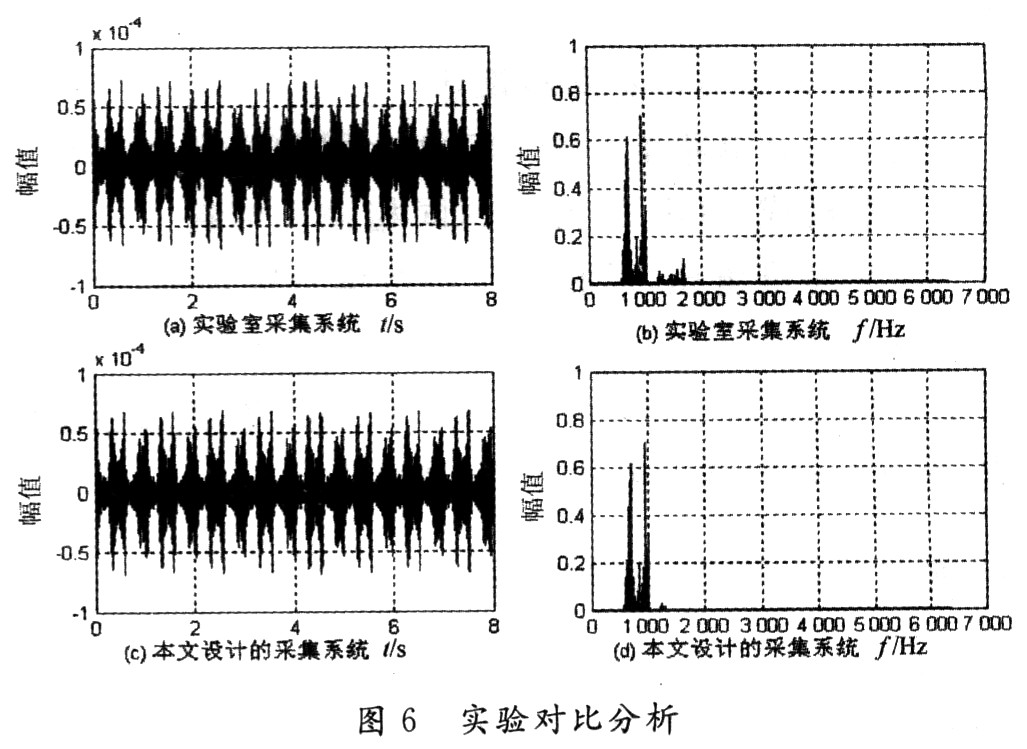

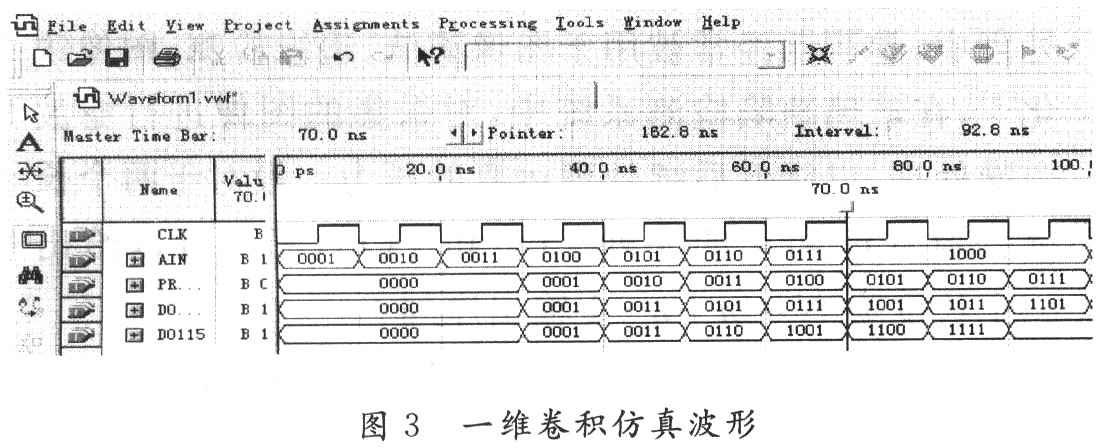

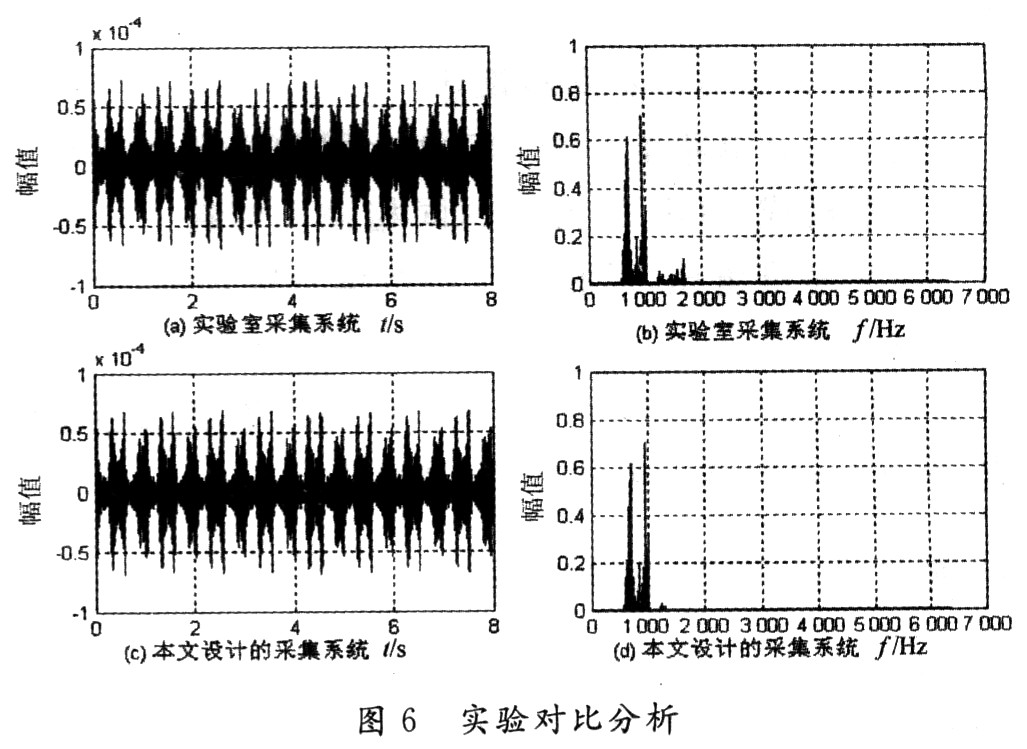

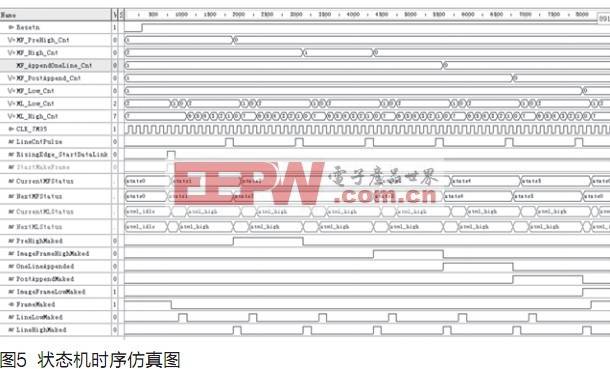

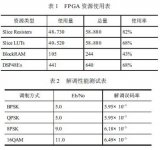

針對遙感系統的工作環境特點、待處理信號的頻譜特征以及系統信噪比等要求,綜合比較多種信號采集系統方案的優缺點,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案,該方案可以實現光

2019-06-24 07:16:30

根據電力監控系統的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統的設計方法。分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 設計了一種基于FPGA 和DSP 的光纖信號實時處理系統,介紹了系統的硬件組成和工作原理。該系統采用FPGA 實現數據的高速采集和邏輯控制,用DSP 實現傳感信號的全數字解調,分析了載

2009-06-19 11:17:43 24

24 本文論述了一種高精度振動信號處理系統的設計原理和方法。該系統完成振動信號的測試和數據均衡計算。配合控制控制模塊可實現振動臺的閉環控制。在本文的最后給出了該系統

2009-08-15 10:50:03 11

11 介紹了數字水準儀數據采集和處理系統的原理與設計,設計一種基于定點DSPTMS320VC5402 的信號采集與處理系統,該系統應用了美國德州儀器(TI)公司生產的8位半閃速結構模數

2009-12-19 16:33:06 6

6 本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數字信號處理系統進行了研究。該系統采用A/D轉換器對磁通門輸出信號進行采樣,采樣后的數據通過FPGA進行數據

2009-12-23 15:09:09 15

15 基于DSP和DSP/BIOS的實時雷達信號采集與處理系統:介紹了一種在實時操作系統DSP和DSP/BIOS 平臺下的雷達信號實時采集" 處理與傳輸系統的設計和實現! 利用Tms320c6416DSP強大的數據處理

2010-01-16 16:59:46 25

25 介紹了一種基于FPGA 的超高速數據采集與處理系統,給出了系統實現的方案,并詳細闡述了各硬件電路的具體構成。對系統軟件功能做了簡要介紹,并利用嵌入式邏輯分析儀對該超高

2010-01-20 16:03:27 58

58 本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數字信號處理系統進行了研究。該系統采用A/D轉換器對磁通門輸出信號進行采樣,采樣后的數據通過FPGA進行數據處理,再

2010-07-21 17:24:58 26

26 設計了一種基于LabVIEW的激光多譜勒信號采集與處理系統,分析系統硬件配置、接口電路、工作原理等,實現信號采集、處理等功能。實驗證明,該系統具有較好的精確性和可

2010-12-25 17:16:49 61

61 摘要:介紹了一種新型的基本計算機和數字示波器的陣列超聲場的信號采集和處理系統。系統利用Windows平臺,采用VC、VB和Matlab編程方法,采集信號并進行信號處理

2006-03-24 13:13:06 941

941

基于DSP的圖象采集與處理系統的設計

圖像處理系統的一個關鍵問題就是數據量龐大,數據處理相關性高,實時實現比較困難。即使采用高速單片機也無法

2009-04-22 20:01:19 820

820

摘要:提出一種基于FPGA技術的多路模擬量、數字量采集與處理系統的設計方案,分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案等。本設計

2009-06-20 15:05:11 1543

1543 微弱振動信號自適應采集系統設計

在許多交通運行機械的振動信號測量中,強噪聲和微弱振動信號混疊在正常振動信號中,給振動系統的微弱信號

2009-10-25 12:36:33 1801

1801

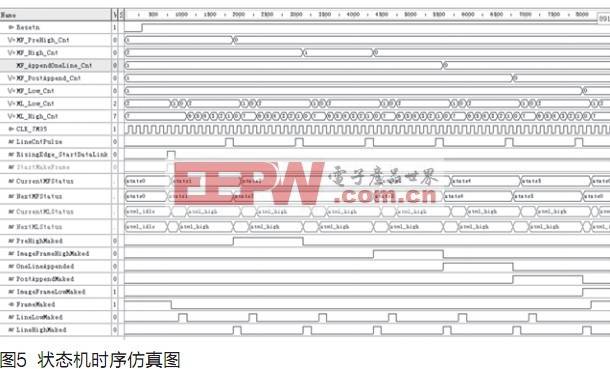

嵌入式視頻處理系統領域的FPGA驗證

隨著生活水準的不斷提升,越來越多的家庭開始在客廳配備5.1聲道或7.1聲道的家庭影院系統。

不過,對于

2009-11-03 09:53:32 646

646

基于FPGA玻璃缺陷圖像采集處理系統

引 言 玻璃缺陷檢測是玻璃生產過程中一個相當重要課題。玻璃缺陷(氣泡、結石、錫點等)妨礙了它在重大技術

2009-11-13 09:53:08 670

670

基于FPGA的遠程圖像采集系統設計

圖像信息的獲取和傳輸是圖像處理系統的重要組成部分,直接影響圖像處理系統的性能。圖像信息的采集包括對圖

2009-11-23 21:03:25 1177

1177

Harris公司的工程師們經常在緊迫的時限內交付基于FPGA的復雜信號處理系統。為了滿足客戶時常十分嚴格的要求以及自身的質量標準,工程師們會在綜合各個系統前徹底驗證HDL設計。 在過去,HDL驗證需要多步手工操作現在,Harris工程師們使用EDASimulatoLink實現

2011-03-15 15:36:21 13

13 介紹了一種用于數字化雙功能多普勒超聲成像儀中以單片FPGA 實現的實時、多任務、高速信號處理系統,該系統承擔著動態濾波、多普勒解調、包絡檢波、FFT 變換、數據壓縮、數據選通等

2011-09-14 15:18:43 143

143 在以DSP為核心的視頻處理系統中,視頻采集的方法通常可以分為兩大類:自動的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過FIFO或者雙口RAM向DSP傳送數據

2011-09-14 17:05:31 2302

2302

文中給出了一種信號處理系統的硬件實現方案。首先概述GPS自適應調零天線的系統結構,然后給出信號處理系統的硬件設計思路及其功能模塊的實現,最后通過實測數據驗證硬件模塊可以

2011-11-30 16:47:07 80

80 本文介紹了一種基于FPGA的網絡圖像處理系統設計和實現方法。系統主要包括圖像采集模塊、RAM控制模塊、JPEG編碼器3部分邏輯。在單片FPGA上實現圖像的采集、裁剪、緩存和JPEG編碼,構建

2012-02-08 14:41:59 1731

1731

為了實時獲取反映井下工況信息的鉆柱振動信號,文中設計了鉆柱振動信號采集系統。采用壓電式加速度傳感器實現三維振動信號的測量變送,針對井場復雜布線情況,選用nRF905射頻模

2012-04-20 10:29:44 29

29 采用聲卡代替商用數據采集卡,利用Visual C++軟件編程技術,設計了基于聲卡的雙通道實時信號采集處理系統,該系統能夠實現25 kHz范圍內雙路信號的實時采集、實時分析,所采集數據的

2013-02-21 16:19:32 59

59 基于FPGA的雷達信號處理系統設計的論文

2015-10-30 10:38:12 6

6 基于FPGA的視頻后處理系統--的技術論文

2015-10-30 10:38:26 0

0 基于FPGA的玻璃缺陷圖像采集預處理系統設計

2016-08-30 15:10:14 13

13 一種基于FPGA和PCI總線的天文圖像實時采集與處理系統的設計,感興趣的小伙伴們可以看一看。

2016-09-14 17:17:07 8

8 基于TMS320F2812的陀螺信號實時采集處理系統

2016-12-17 16:33:39 13

13 基于FPGA+DSP實時圖像采集處理系統設計

2017-01-03 11:41:35 9

9 語音采集、處理系統

2017-02-27 16:18:02 9

9 基于FPGA的視頻圖像處理系統設計_李蓮

2017-03-19 11:38:26 21

21 基于LabVIEW的信號采集處理系統_金愛娟

2017-03-18 09:38:39 27

27 基于雙DSP和雙FPGA的高速圖像處理系統設計_吳雷

2017-03-16 09:28:51 2

2 基于DSP_FPGA的LFMCW雷達測距信號處理系統設計_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA的通用傳感器信號處理系統設計_李輝

2017-03-19 19:07:17 3

3 基于FPGA和DSP的高速圖像處理系統

2017-10-19 13:43:31 19

19 基于DSP的數字信號采集處理系統設計

2017-10-19 15:10:22 25

25 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 針對機械設備運行中的振動監控,設計振動信號采集系統,提出了一種基于FPGA的振動信號采集系統的設計方案。重點闡述了系統硬件結構組成、信號調理電路和數據采集模塊的設計,同時對A/D采樣的控制邏輯進行了討論。經試驗驗證表明,該系統可達到采樣率10 K每秒、采集精度16位,能夠滿足實時性和精度要求。

2017-11-17 11:04:38 5991

5991

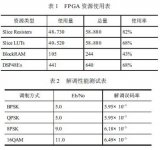

衛星通信是當前重要的通信手段之一。針對原有單路解調器的不足,本文提出利用軟件無線電思想,通過FPGA構建一種多路衛星信號處理系統。論述了數字下變頻(DDC)、解調、數據通路等關鍵點的設計思路。最終

2017-11-18 08:26:14 1949

1949

近年來,雷達在軍用和民用領域都獲得了巨大的發展。雷達信號處理系統是雷達的關鍵模塊,對雷達定位精度起著決定性作用。FPGA 以其眾多的優點,在雷達信號處理系統中被廣泛使用。本文探究FPGA 在雷達信號

2017-11-22 07:25:02 4251

4251

警,但模/數存在誤報警的問題。對振動信號進行模式識別是一種降低誤報警率的方法。國內各研究單位對光纖傳感器的振動模式識別也開展了一些研究,但都是基于PC端的離線處理,滿足不了系統實時性和小型化的要求。本文設計的基于FPGA和DSP的光纖微振動傳感器數據采集和實時處理系統滿足系統對實時性和小型化的要求

2018-07-17 08:07:00 2101

2101

當CCD產生的視頻信號為模擬信號對,對其直接傳輸、存儲和處理比較困難,須要將模擬視頻信號轉換為數字視頻信號,以便對其進行處理,并進行高效可靠的傳輸和存儲。當前,數字圖像采集和處理系統不僅要面臨

2018-07-16 09:42:00 2633

2633

本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統的設計與實現,DSP-BF561作為主處理器,負責整個算法的調度和數據流的控制,完成圖像數據的采集與顯示及核心算法的實現,FPGA作為DSP的協處理器,依托其高度的并行處理能力,完成圖像預處理中大量的累乘加運算。實驗證明系統達到了實時性要求。

2017-12-25 10:39:47 4504

4504

FPGA+DSP的數字硬件系統正好結合了兩者的優點,兼顧了速度和靈活性。本文以導引頭信號處理系統為例說明FPGA+DSP系統中FPGA的關鍵技術。

2019-01-08 08:36:00 2449

2449

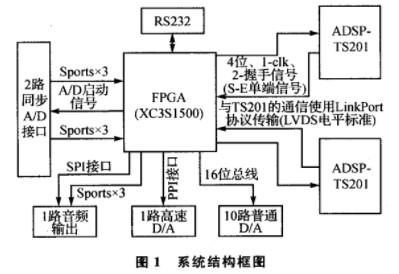

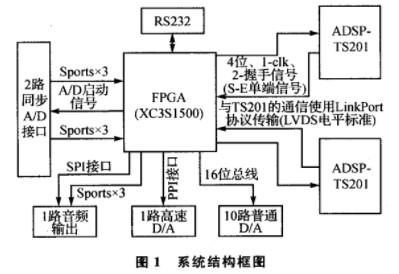

本系統以FPGA作為高性能實時信號處理系統的數據采集和控制中心,2片DSP為數據處理中心,主要包括4個功能模塊——數據采集模塊、FPGA數據控制模塊、DSP處理模塊和通信模塊,系統結構框圖如圖1所示。

2019-04-23 08:29:00 3426

3426

本文提出了一種實現信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統的系統設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現了信號的采集與存儲。

2018-11-02 15:46:01 10

10 本文檔的主要內容詳細介紹的是FPGA視頻教程之使用FPGA進行嵌入式信號處理系統設計視頻資料免費下載包括了:1、FPGA的最新發展現狀和設計流程;,2、基于FPGA的嵌入式系統技術,3、基于FPGA

2019-03-29 16:53:50 15

15 設計了一套高速線陣CCD信號采集系統,采用FPGA+DSP的數字處理方案,能滿足光信號的實時識別和處理,可用于研究靜態和動態小粒子的光散射彩虹特性。

2019-11-21 17:32:39 24

24 提出了一種基于FPGA和PCI總線的天文圖像實時采集與處理系統設計;其包括硬件結構、FPGA數據獲取和傳輸邏輯。該系統能夠在FPGA中實現對最高峰值是660 MB/s,均值為200 MB/s,幀速率

2021-02-04 16:46:00 16

16 基于FPGA的嵌入式信號處理系統設計方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號處理系統設計方案

2021-06-02 11:04:33 0

0 基于FPGA+DSP彈載SAR信號處理系統設計

2021-12-27 18:58:51 21

21 《心電信號采集及小波分析處理系統設計》pdf

2022-02-09 16:47:57 18

18 ZL-620A一體信息化信號采集處理系統采用一體化設計原則,同時集成了可移動實驗平臺、醫學信號采集系統、呼吸系統、測溫系統、照明系統以及同步演示系統。幫助科研工作者獲取更客觀、的實驗數據,是研究人員

2022-05-17 17:17:15 727

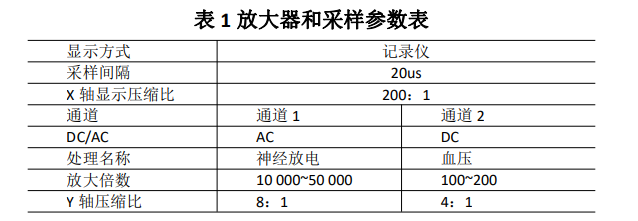

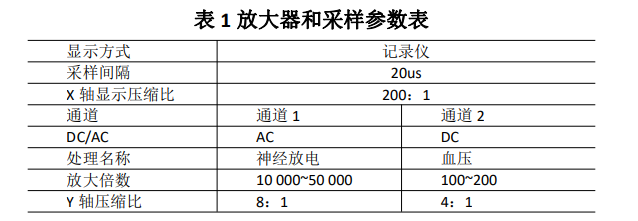

727 ? ?近年來隨著科學技術的迅猛發展與信號實時采集處理技術日趨 完善,生物信號采集處理系統在生理學科實驗室得到普及和應用,僅 靠一臺處理器就可以對多個生物信號放大、記錄、信號輸出和刺激輸 出的功能

2022-05-23 17:33:01 476

476

ZL-620 醫學信號采集處理系統是一種多單片機控制、專為生命學 科設計的生物信號記錄和數據處理系統,取代了傳統的多道生理記錄 儀、示波器、X-Y 記錄儀和刺激器等儀器,能對生物肌體

2022-05-24 15:32:34 618

618 隨著 FPGA 數字信號處理系統復雜度不斷提高,FPGA 信號處理系統的功能驗證已經成為影響產品上市時間和成本的關鍵[1]。盡管在驗證領域已經發展出多種自動測試方法,但是針對信號處理算法進行驗證

2022-11-04 16:24:47 1475

1475 FPGA在視頻處理方面可能很有用處,但在驗證基于FPGA的視頻系統時,則需要仔細關注您所用的方法。

2023-10-27 17:34:39 158

158 電子發燒友網站提供《基于PC104的實時信號采集處理系統設計.pdf》資料免費下載

2023-10-10 09:37:54 1

1

正在加载...

電子發燒友App

電子發燒友App

評論