引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。

2022-07-22 09:46:39 682

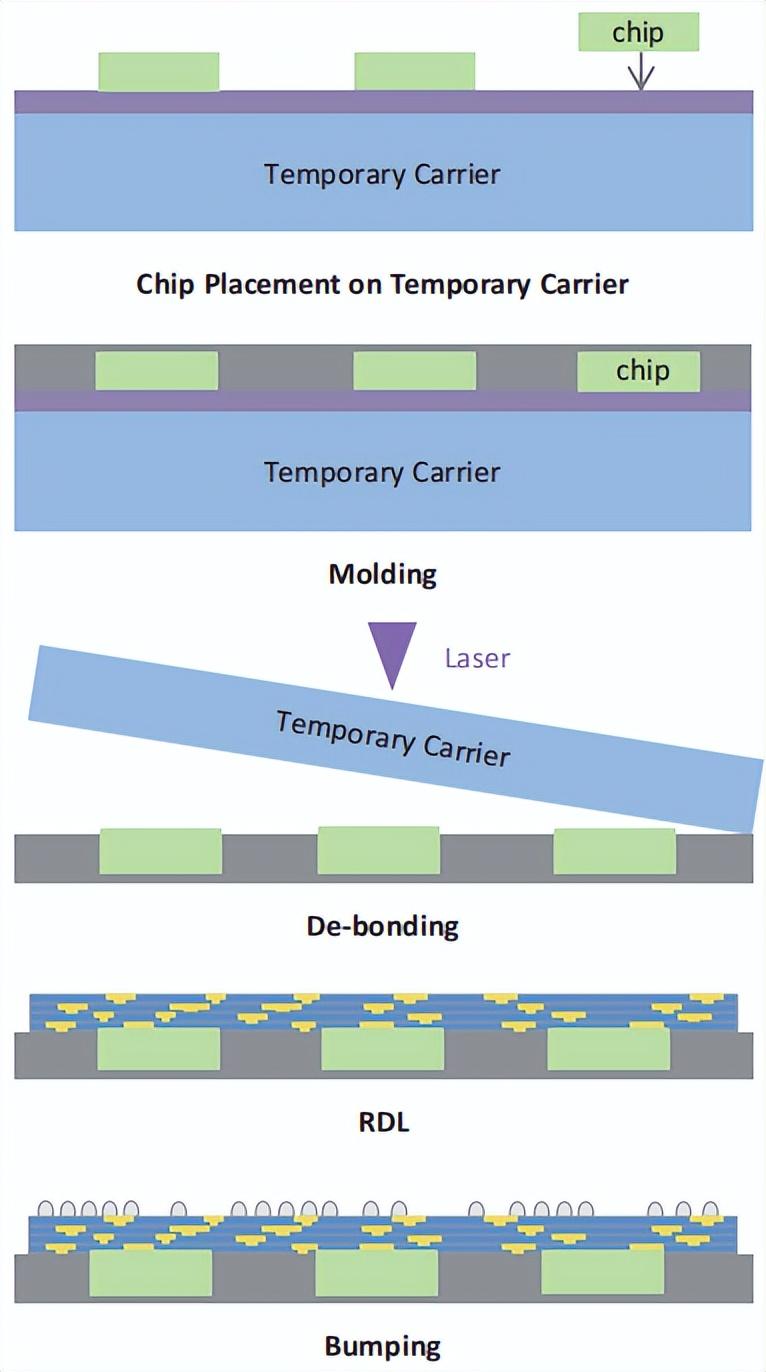

682 ),通過RDL替代了傳統封裝下基板傳輸信號的作用,使得扇出型封裝可以不需要基板而且芯片成品的高度會更低,所以扇出型封裝的發明初衷其實是降低成本,而且由于扇出型封裝在封裝面積上沒有扇入那么多限制,整個封裝設計也會變得更加靈活和“自由”。因此扇出封裝最先在一些小面積、低性能的領域被推廣開來。

2023-11-27 16:02:01 2459

2459

14.2節提到的問題①,即設計中有很大的扇出,對于如何獲知該扇出信號有多種途徑。常見的途徑是通過FPGAEditor(Xilinx)或者Fitter里Resource Section

2024-03-20 17:33:34 491

491

本文的目的是了解為什么Deca的扇出技術最近被高通用于其PMIC扇入WLP die的保護層。嚴格的說,這仍舊是一個扇入die與側壁鈍化所做的扇出封裝。因此,本文的第一部分將描述扇入式WLP市場以及

2019-07-05 14:21:31 7031

7031 會有比較詳細的結構圖,因為是新人對于找資料解決問題,還是比較弱,往往無從下手)2. 想對FPGA的IO,設計成可配置的形式,可以當普通IO口使用,有輸入輸出,也可以配置成復用模式,可配置成復用功能,復用輸入功能好像會遇到扇入的問題,大家有沒有比較好的思路。

2015-10-31 20:13:49

本人菜鳥,求FPGA入門級資料,謝謝{:1:}

2014-01-16 23:56:48

幾個不錯的資料哦,給大家共享下《FPGA系統設計的主要思路和方法初探》.pdf (766.25 KB )FPGA驗證簡介.pdf (255.69 KB )FPGA經驗總結(精華).doc (1.03

2019-05-27 02:11:57

FPGA畢竟不是ASIC,對時序收斂的要求更加嚴格,本文主要介紹本人在工程中學習到的各種時序約束技巧。 首先強烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒有之一。它提倡

2020-12-23 17:42:10

我想在fpga上做一個報文解析的功能,就是將一串01數據發送給FPGA,然后fpga對數據進行報文解析,然后再將解析后的數據發送給電腦,想問各位大神解析模塊應該怎么寫?有沒有相關的資料可以參考的???急求???

2017-11-13 16:04:16

fpga初學資料,剛開始看感覺不錯,分享一下

2013-12-03 19:14:55

fpga教程之華為verilog教程下載ModelSim SE 十分鐘入門教程下載Mico32入門上手資料說明書完全下載Altera和Xilinx Modelsim仿真庫 FPGA 管腳分配需要考慮的因素

2010-06-21 14:59:01

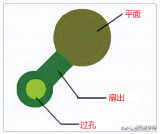

學習allegro 16.5 進行時,扇出使用的過孔問題請教,麻煩大家給答疑一下。謝謝了,祝大家勞動節快樂。看了于博士的視頻,4層的板子,對BGA器件進行了扇出操作。1:為什么信號引腳和電源引腳扇出

2015-04-30 23:50:16

,我現在講我的自動扇出步驟給大家說一下,在BGA上面點擊右鍵,選擇component atcions 然后選擇fanout component,這是會彈出一個對話框,你要是不想要BGA的外邊焊盤扇出

2015-01-07 16:07:17

Altium Designer 9,BGA扇出的時候,外面一圈焊盤出去的線不符合規則設置,我是對ROOM里的線寬設置的是6mil,外面的線是10mil,扇出時BGA外面一圈的焊盤引出的線是10mil,不知道是怎么回事?想刪掉重新扇出,不知道怎么刪,難不成要手動一個一個刪?求高手幫忙!

2015-01-07 15:56:28

AD15做扇出時,選擇如圖,但是做出來的扇出是有很多沒有扇出,多是GND,和一些POWER,在規則設置上,我把把有我Clearance都取消了,請大神賜教,感謝

2015-01-16 10:44:37

如上圖所示,進行BGA fanout操作后,只有一小部分焊盤fanout成功,為何其他的焊盤沒有任何反應?

2016-03-16 10:59:00

`BGA扇出報錯`

2017-03-30 10:46:38

、選擇BGA Fanout 的層:Setup/Layers Setup,BGA一般放在TOP Component 層,Plane Typet 選No Plane ,Routing 選 Any,然后“OK

2012-11-02 16:01:14

設置了BGA扇出之后,卻連線不了,這是咋回事撒?求助各位~~

2012-11-21 10:20:41

IPTV DDR孔扇出,下邊這和VIA孔怎么顯示NO FEFALT

2019-09-30 05:36:43

原點座標,Setup/origin.二、選擇BGA Fanout 的層:Setup/Layers Setup,BGA一般放在TOP Component 層,Plane Typet 選No Plane

2019-06-10 10:05:00

PADS中 BGA Fanout扇出 教程

2013-09-14 21:31:46

PCB 布線是先扇出還是先擺器件? 先擺器件 有的靠的太近 扇出會出現錯誤

2016-01-25 23:18:18

示意圖第一步,點擊執行菜單命令 Route-Create Fanout,進行扇出,如圖 5-123 所示;圖 5-123執行自動扇出示意圖第二步,執行自動扇出的命令之后呢,還需要對參數進行設置,如圖

2020-04-21 08:00:00

概述:MAX3845是TMDS? 2至4扇出開關和電纜驅動器,用于高達1.65Gbps的DVI?或HDMI?信號的多顯示器分配。輸入輸出均為TMDS標準信號,符合DVI和HDMI標準。因為TMDS為

2021-05-17 07:06:20

嗨,我正在使用vivado 2013.4并且在實現后從觸發器的Q引腳到180個負載(RAMB36E1上的ENBWREN引腳)獲得高扇出網絡。它符合時間,但是,我希望網絡能夠得到緩沖。1.有沒有

2018-10-18 14:28:10

`altium designer PCB工具進行BGA Fanout時,為了確保能夠正常扇出,需要進行如下設置:1.規則設置快捷鍵D+R,設置如下幾項:1)clearence間距設置2)width

2015-10-29 12:34:17

接口視頻教程時序圖贊閱讀解析練習講解命令書籍資料:《勇敢的芯伴你玩轉Altera FPGA》電子版 下載 (FPGA初學者首選)書籍:FPGA開發全攻略電子版(超清,上下冊全)玩轉FPGA,這些資料不要

2019-05-17 18:19:21

案例進行實戰演練,讓學員理論與實際結合,徹底掌握BGA扇出的方法。直播大綱1、BGA的概念解析以及設置2、布線規則添加與規則管理器介紹3、區域規則介紹與添加4、各類BGA芯片扇孔與出線實戰演示5、你

2021-03-30 22:03:56

我在fanout 時遇到一個問題,有一些有網絡的引腳它沒有給我扇出,是怎么回事,能幫我解答一下嗎,謝謝

2019-09-06 05:35:11

為啥自動扇出了還報錯啦,求解

2019-09-09 03:12:20

求助0.5mm焊盤,間距0.8mm的BGA封裝怎么設置自動扇出45度;我規則設置線寬4mil,間距也是4mil,可是自動扇出45度的方向失敗,而且有些焊盤扇出不了,如下面第一張圖;;;手動扇出是沒有問題的,下面第二張圖@Kivy @Pcbbar 謝謝!!

2019-09-19 01:08:11

我在時序改進向導中讀到,手動復制源可以減少扇出。任何人都可以解釋復制源的含義嗎?還有一個選項來設置最大扇出,我在合成屬性對話框中默認為100000,而我在某處讀到默認最大扇出為100.我不明白

2018-10-10 11:50:47

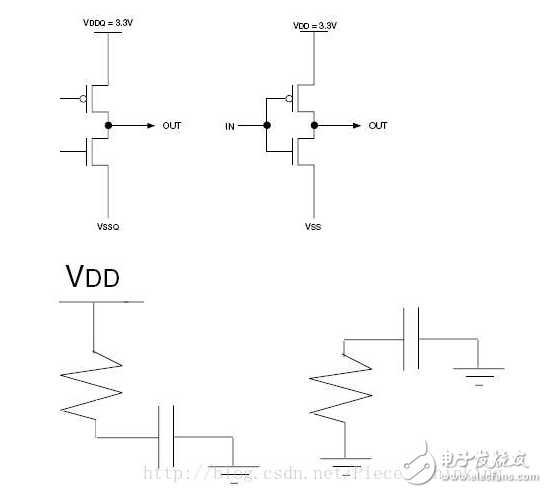

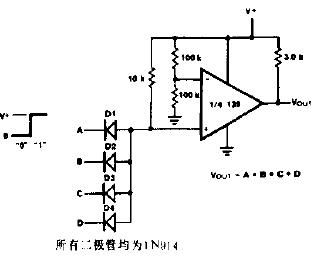

今天我們要介紹的概念是fanin,扇入。是指單個邏輯門的輸入的數量;如下圖為一個fanin為3 的與門;需要注意的是,在STA中,我們不允許出現多個輸出單元同時驅動一個輸入pin的情況,...

2021-07-29 06:34:09

`勇敢的芯伴你玩轉Altera FPGA連載13:實驗平臺復位電路解析特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD FPGA的時鐘

2017-10-23 20:37:22

BGA扇出??點擊工具欄的創造fanout:??????注意走線的設置應如下圖所示,將bubble模式關掉。??????在點擊fanout命令后,按照下圖所示設定fanout的設置:選擇合適的過孔

2021-12-31 06:54:47

在HDL中改變電氣連接(改變IC器件pin的net),在原有fanout過板子基礎上,再次倒板子。某些IC器件的fanout消失了,某些器件的IC器件的fanout沒有消失,但是fanout出來的孔

2015-11-09 15:23:42

基于DSP與PC機的PCI總線高速數據傳輸資料解析,不看肯定后悔

2021-06-03 06:47:49

你好什么是FPGA IO引腳的扇出....我正在使用LVTTL 3.3信號電平...我想將FPGA連接到比較器的鎖存信號....我有32個比較器需要從FPGA給出鎖存信號....問候,維諾德

2020-06-02 14:22:53

只是將TDI信號扇出到所有FPGA,而不是一次扇出1。是否有示例圖表顯示如何完成此操作?我該如何處理TDO?我可以期望所有這些設備同時進行編程會出現什么樣的功率峰值?謝謝,唐

2020-05-14 07:01:03

中,一個時鐘源要驅動多個器件,因此可使用時鐘緩沖器(通常稱為扇出緩沖器)來復制信號源,提供更高的激勵電平。圖 1. 使用扇出緩沖器創建大量單輸入頻率副本LMK00304 扇出緩沖器就是一個很好的例子

2022-11-21 07:25:28

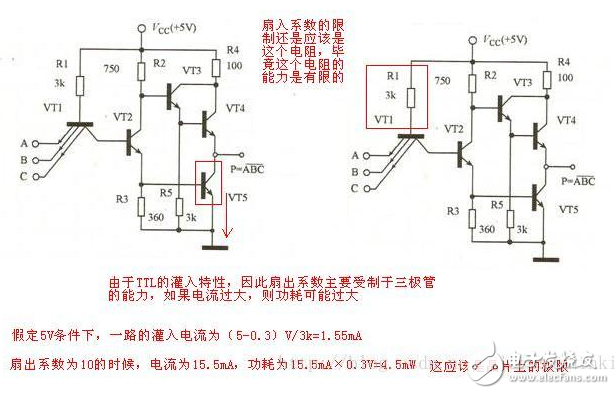

在上拉和下拉電阻中是不是有對應的拉電流和灌電流?拉電流和灌電流是什么意思?扇出系數是指什么?

2021-04-07 06:46:24

嗨,所有,在正常的I/O引腳,我們考慮扇出計算時,我們有更多的設備連接到單一邏輯輸出。在I2C除了總線電容的情況下,我們是否需要考慮扇出?我發現高輸出電流和低輸出電流,低電平輸入電流這些參數需要考慮嗎?謝謝

2019-10-09 13:12:37

求大神分享一下PADS中BGA Fanout扇出教程

2021-04-25 07:37:39

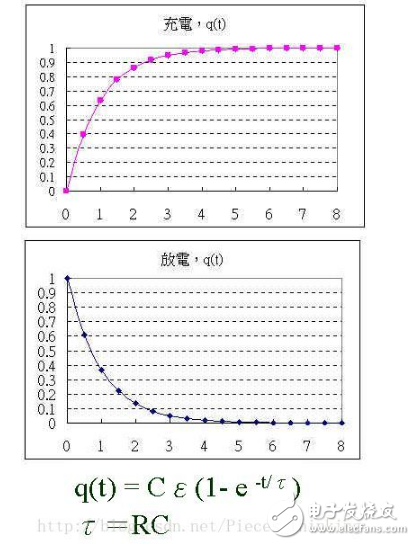

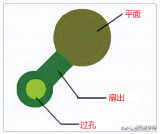

在我們常規設計中對濾波電容fanout時,要從pin拉出一小段粗引出線,然后通過過孔和電源平面連接,接地端也是同樣。fanout過孔的基本原則就是讓這一環路面積最小,進而使總的寄生電感最小。濾波電容的常見fanout方式如下圖所示,濾波電容靠近電源pin放置。

2019-07-31 08:36:05

用FPGA做的MCU內核的匯編指令集完全解析,FPGA使用VHDL編寫MCU內核,使用PHP編寫匯編器,使用vc studio編寫FLASH下載器,全套資料在 www.creuu.com 免費下載

2020-03-04 18:53:52

遇到過很多次了,各種不同的FPGA均遇到過這種問題。改動一個完全跟邏輯沒有關系的地方就不能正常工作,但將某些信號扇出到輸出管腳上之后又能正常工作了。請問這種現象是什么原因產生的?有沒有什么比較好的解決方法?

2014-08-01 16:11:56

AD9513可否用于數字信號的fanout driver(帶有編碼、不需要分頻)?

2018-08-20 07:20:03

請問一下fanin是什么意思?

2021-10-29 07:14:15

請問下誰知道DDR扇出為什么只扇出電源和地的部分,其他都沒有扇出來?

2016-11-28 13:04:19

轉載一篇講述高扇出的解決辦法的博文。鏈接:http://blog.163.com/fabulous_wyg/blog/static/174050785201322643839347/

2014-04-29 21:41:20

FPGA設計中,經常會出現由于設計不合理產生的布線問題,較為突出的一點就是門控時鐘和多扇出問題。門控時鐘指的是不用FPGA內部的全局時鐘資源BUFG來控制觸發器的時鐘沿輸入端而是采用組合邏輯和其它

2012-01-12 10:40:20

在我的設計中,我有幾個高負荷信號,現在我認為我的定義和Xiinx對高扇出的定義是完全不同的。如果我看到一個控制信號,當使用12.5ns周期時扇出為300,凈延遲為7.5ns。我開始擔心了。當時間報告

2018-11-01 16:13:02

布線前期準備和扇出... 795.1 前期準備................. 795.1.1 布局優化............ 795.1.2 自動布線密度評估............... 795.1.3 關鍵信號手工布線.............. 815.2 扇出(FANOUT) ...

2008-08-05 14:36:19 0

0

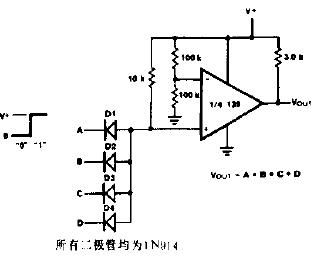

高扇入與門電路圖

2009-04-02 09:20:04 518

518

扇出系數,扇出系數是什么意思

扇出系數No:扇出系數No是指與非門輸出端連接同類門的最多個數。它反映了與非門的帶負載能力 。

2010-03-08 11:06:20 8029

8029 扇入系數系數,扇入系數是什么意思

扇入系數NI: 門電路允許的輸入端的數目,稱為該門電路的扇入系數。一般NI≤5,最多不超過8。實

2010-03-08 11:07:40 2052

2052 一、建立原點座標:(用PADS 2005 打開沒有layout BGA文件)1.鼠標右鍵,點選"Select Traces/Pins",再點BGA的左上角的一

2010-06-24 17:49:42 7505

7505 DDR3內存已經被廣泛地使用,專業的PCB設計工程師會不可避免地會使用它來設計電路板。本文為您提出了一些關于DDR3信號正確扇出和走線的建議,這些建議同樣也適用于高密度、緊湊型的電路板設計。

2018-06-16 07:17:00 8959

8959

本文檔的主要內容詳細介紹的是FPGA基礎及7系列FPGA基本原理的基礎資料說明

2019-04-28 08:00:00 15

15 找到目標后,可以利用max_fanout來限定其扇出值,讓工具在實現過程中復制驅動端寄存器來優化。如果高扇出網絡并不是由同步邏輯來驅動,則可能需要修改代碼。

2019-07-25 11:45:52 2402

2402

在設計集成電路時,扇出是指門輸入的數量a邏輯門輸出可以連接到。雖然狗骨扇出是一種經得起考驗的方法,但值得考慮針對特定應用的墊內扇出方法的優點,以及檢查在制定扇出策略時應采取的各種考慮因素。

2019-07-25 09:58:04 3831

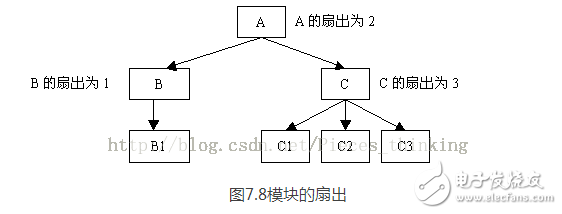

3831 Fanout,即扇出,指模塊直接調用的下級模塊的個數,如果這個數值過大的話,在FPGA直接表現為net delay較大,不利于時序收斂。因此,在寫代碼時應盡量避免高扇出的情況。但是,在某些特殊情況下,受到整體結構設計的需要或者無法修改代碼的限制,則需要通過其它優化手段解決高扇出帶來的問題。

2019-10-13 14:55:00 3506

3506

在allegro軟件中應該如何對BGA器件進行自動扇出呢? 答:在進行PCB布線之前,都需要先做扇出工作,方便內層布線。對于電阻電容后者是小的IC類器件,可以直接進行手動扇出,但是對BGA類的器件

2020-10-14 10:28:43 6992

6992

在先進封裝技術中,晶圓級封裝能夠提供最小、最薄的形狀因子以及合理的可靠性,越來越受市場歡迎。晶圓級扇出和WLCSP/扇入仍然是兩個強大的晶圓級封裝家族。不同于晶圓級扇出,WLCSP工藝流程簡單,封裝

2021-01-08 11:27:46 8883

8883

ARM與FPGA的接口實現的解析(應廣單片機)-該文檔為ARM與FPGA的接口實現的解析詳述資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-22 09:47:55 14

14 EDID詳細解析資料匯總

2021-09-23 15:30:17 22

22 1.扇出太多引起的時序問題。 信號驅動非常大,扇出很大,需要增加驅動能力,如果單純考慮驅動能力可以嘗試增加buffer來解決驅動能力,但在插入buffer的同時增加了route的延時,容易出現

2021-10-25 16:30:06 7702

7702 今天我們要介紹的概念是fanin,扇入。是指單個邏輯門的輸入的數量;如下圖為一個fanin為3 的與門;需要注意的是,在STA中,我們不允許出現多個輸出單元同時驅動一個輸入pin的情況,也就

2021-11-26 10:27:35 4824

4824

今天要介紹的時序分析概念是fanout。中文名是扇出。指的是指定pin或者port的輸出端口數。 合理的選擇fanout的數目對設計來說是非常重要的,fanout過大與過小都會對設計帶來不利因素

2021-11-26 10:31:41 11753

11753

BGA扇出??點擊工具欄的創造fanout:??????注意走線的設置應如下圖所示,將bubble模式關掉。??????在點擊fanout命令后,按照下圖所示設定fanout的設置:選擇合適的過孔

2022-01-11 12:08:40 4

4 測量扇出緩沖器中的附加抖動

2022-11-04 09:52:08 0

0 1 到 4 扇出緩沖器-74AVC1T1004

2023-02-16 21:16:26 0

0 1 到 4 扇出緩沖器-74AVC9112

2023-02-21 19:33:20 0

0 1 到 4 扇出緩沖器-74AVC1T1022

2023-03-03 19:53:47 0

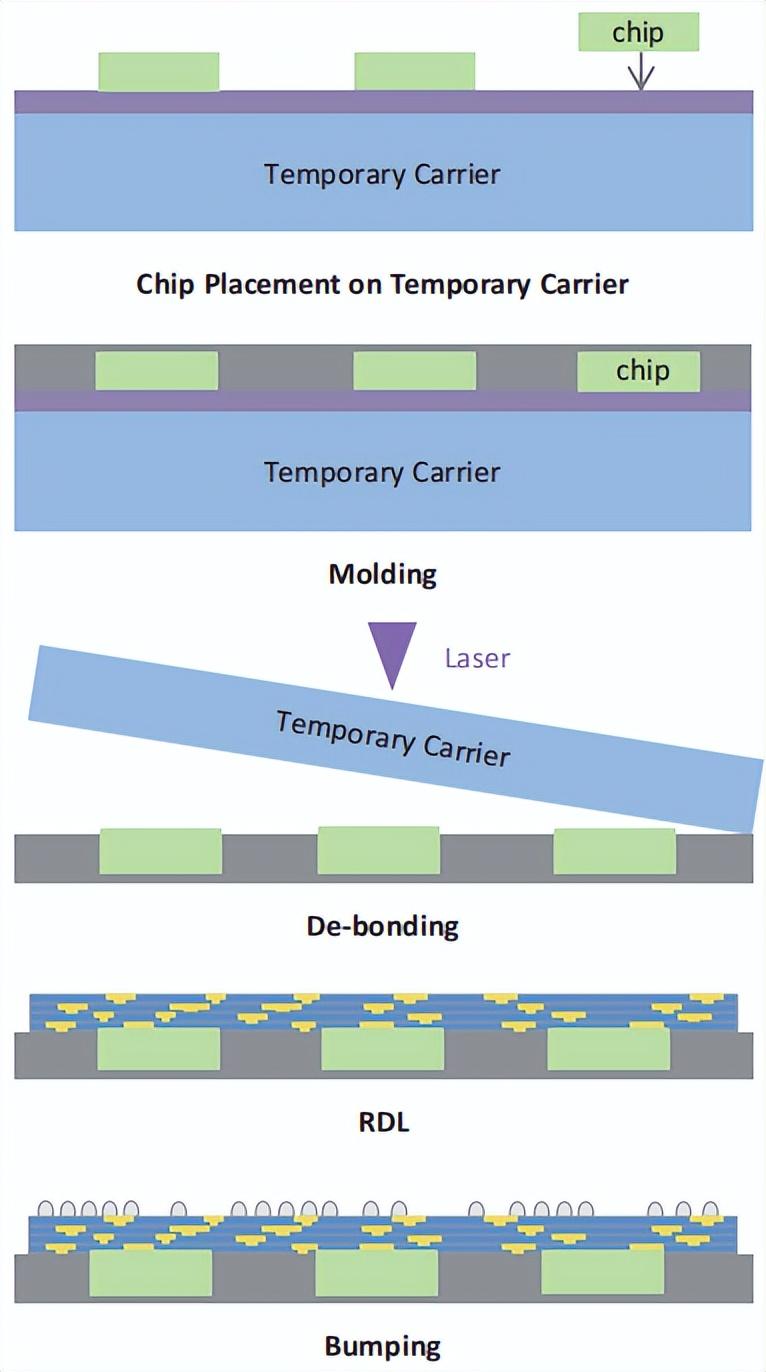

0 來源;《半導體芯科技》雜志 作者:黃泰源、羅長誠、鐘興進,廣東鴻浩半導體設備有限公司 摘要 扇出晶圓級封裝廣泛應用于手機、車載等電子產品上。制造過程中需要使用到暫時性基板,而移除暫時性基板最適

2023-04-28 17:44:43 972

972

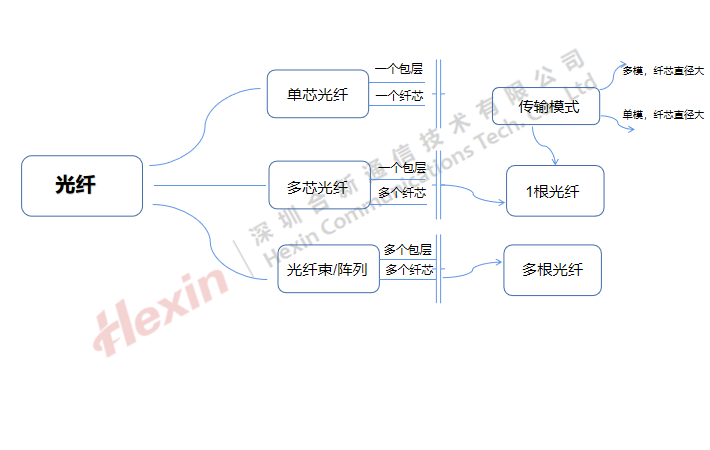

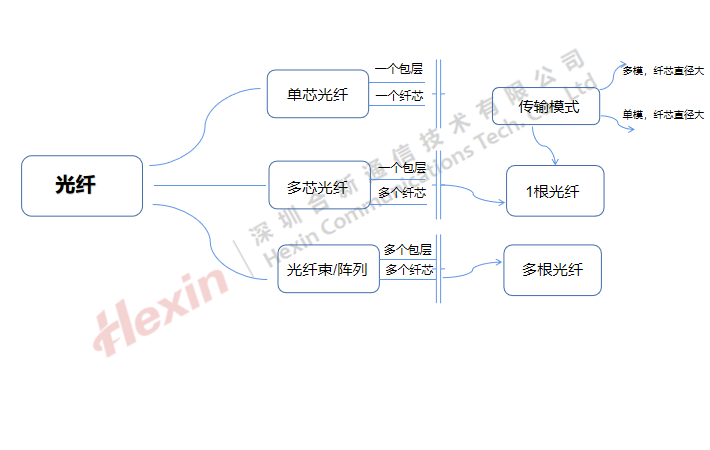

。而多光纖束可以做成各種形狀,省空間,傳輸容量又夠大。但多芯光纖有兩個困難是影響到實際運用的:一.串擾,二.扇入扇出扇入扇出,就咱們單芯光纖與多芯光纖怎么對接,一般

2021-12-27 14:09:15 1408

1408

在 PCB 布局設計中,特別是BGA(球柵陣列),PCB扇出、焊盤和過孔尤為重要。扇出是從器件焊盤到相鄰過孔的走線。

2023-07-18 12:38:12 1769

1769

、中文資料、英文資料,HMC940: 13 Gbps, 1:4 Fanout Buffer w/ Programmable Output Voltage Data Sheet真值表,HMC940: 13

2023-10-13 18:33:07

扇出型晶圓級封裝技術的優勢在于能夠利用高密度布線制造工藝,形成功率損耗更低、功能性更強的芯片封裝結構,讓系統級封裝(System in a Package, SiP)和3D芯片封裝更愿意采用扇出型晶圓級封裝工藝。

2023-10-25 15:16:14 314

314

電子發燒友App

電子發燒友App

評論