先給大家簡單快速地介紹一下 Vivado 集成設計環境,即 IDE。當打開 Vivado 工程后,會有一個工程概要,向您介紹工程的設置、警告和錯誤信息以及工程的一般狀態。

2012-04-25 09:00:43 6408

6408 作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3153

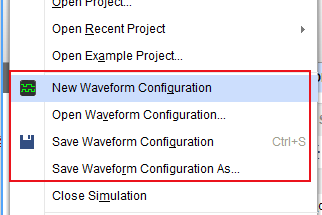

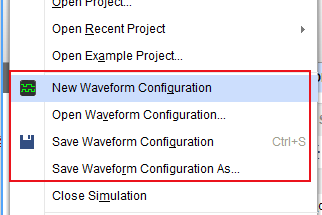

3153 配置顯示為untitled。打開仿真后,File菜單中有與波形配置相關的指令: ? ? 這些控制功能依次是: New Waveform Configuration:創建一個新的波形配置,Vivado

2021-01-03 09:22:00 7311

7311

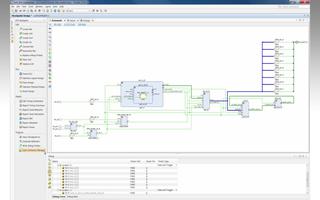

仿真功能概述 仿真FPGA開發中常用的功能,通過給設計注入激勵和觀察輸出結果,驗證設計的功能性。Vivado設計套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 4723

4723

在Vitis完成這個過程的底層,實際調用的是Vivado。Vitis會指定默認的Vivado策略來執行綜合和實現的步驟。當默認的Vivado策略無法達到預期的時序要求時,我們需要在Vivado中分

2022-08-02 08:03:38 1016

1016

Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-14 09:09:56 1526

1526 雙擊桌面圖標打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

/ 134第5章 IP的管理 / 1355.1 定制IP / 1355.1.1 在Vivado工程中定制IP / 1355.1.2 在Manage IP中定制IP / 1395.2 IP的兩種生成文件形式

2020-10-21 18:24:48

我在兩臺64位Windows機器上安裝了2013.1,并且兩者都崩潰了。 Vivado 2013.1窗口在崩潰之前會短暫出現。如果我從命令行運行,我會看到:****** Vivado v2013.1

2018-11-27 14:30:08

License(由VLM加載.xml文件),并在VLM中顯示。我在論壇中嘗試了很多解決方案: - 我重新安裝了Vivado三次, - 我用禁用防病毒軟件(Avast)運行模擬,我檢查了它的“病毒庫

2018-12-12 10:52:39

功能'Synthesis'和/或設備'xc7a35t'的有效許可證。請運行Vivado許可證管理器以獲取有關確定系統許可的功能和設備的幫助。解決方案:在Vivado License Manager中檢查

2018-12-26 11:30:48

你好,我們今天剛剛收到一個ZC706開發套件(帶有Zynq XC7Z045),我們非常驚訝,因為在歡迎信中寫道:“隨著Vivado 2015.4的發布,該產品已被凍結。它將不會在后來的Vivado軟件中運行”這應該是什么意思?我們正在使用最新的Vivado版本2016.1!謝謝,Cerilet

2019-10-10 08:24:14

你好,在Vivado 2016.4中運行Synthesis功能時,我收到了有效的許可證錯誤[Common 17-345]。請參閱附件和幫助。謝謝,Gursimar合成日志file.txt 2 KB

2019-01-04 11:22:27

嗨伙計,我在Vivado面臨一個問題。我已經生成了三模式以太網MAC(TEMAC)的示例設計,作為Artix7 FPGA板的給定指令。在此之后,我測試了Tx和Rx用于TEMAC。我可以成功傳輸數據

2020-07-23 08:23:46

嗨,在我的Vivado實現tcl腳本中,以下行導致錯誤:設置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

Vivado實現線程卡在“編寫放置器數據庫”上。該路由成功完成并且Vivado許可證被釋放,然后它將編寫占位符數據庫并且永??遠不會完成,只是在那里永久旋轉。在Windows任務管理器中殺死線程后

2018-10-30 11:15:39

特性比較對 Vivado 和它的前一代設計套件,ISE 做一個組件功能上的平行比較和總結是很有用的。其目的是讓那些具有在 ISE 下工作經驗 (但是不具有 Vivado 下經驗)的人能夠更快的適應

2021-01-08 17:07:20

TakeVideos:快速使用的視頻連接口,關聯到DocNav,并篩選出Vivado使用的一些教學視頻;Release NotesGuide:在DocNav中打開Vivado release Notes

2019-07-18 15:40:33

TakeVideos:快速使用的視頻連接口,關聯到DocNav,并篩選出Vivado使用的一些教學視頻;Release NotesGuide:在DocNav中打開Vivado release Notes

2023-09-06 17:55:44

大家好,我想知道Vivado生成的HDL代碼是否在Vivado自帶的許可證之上有任何特殊的許可。考慮為AXI奴隸生成的代碼,有什么阻止我在設置中使用它大學課程的論文?如果代碼剛剛生成并從設計訴訟中

2018-12-20 11:23:27

嗨,我在Vivado 16.2中重新創建了一個在Vivado 15.2中完美運行的固件。當我嘗試在IPI中驗證設計時,它會給出錯誤和嚴重警告。這個版本的Vivado的參數propragation有

2020-08-06 07:55:13

:[Common 17-345]找不到功能'Synthesis'和/或設備'xc7a35t'的有效許可證。請運行Vivado許可證管理器以獲取有關確定哪些功能和設備已獲得系統許可的幫助。解決方案:在

2018-12-14 11:32:37

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的時鐘方案是zynq PS FCLK_CLK0-->時鐘向導IP輸入(Primitive PLL)的輸入。合成

2018-11-05 11:40:53

請問各位大神,vivado中點擊綜合或者實現時,出現的number of jobs 代表什么意思?

2018-03-09 22:18:19

想到要寫這一系列關于工具和方法學的小文章是在半年多前,那時候Vivado?已經推出兩年,陸續也接觸了不少客戶和他們的設計。我所在的部門叫做“Tools & Methodology

2023-09-20 06:31:14

嗨,在Vivado 2015.4和ISE 14.7中實現的相同設計之間的資源利用率是否會有任何差異?考慮到這樣的事實,IP在Artix-7 FPGA中重新生成FIFO(版本9.3到13.1)時鐘向導

2019-04-24 09:12:08

大家好,感謝您的關注。 (這是我在論壇上的第一個主題?)我已經了解到Quartus II具有Logic Lock功能,這對于組中的設計人員來說非常方便,并且還具有時序優化功能。我對vivado并不

2020-05-20 14:32:56

大家好,我正在嘗試在Ubuntu 13.10上安裝Vivado 2013.2我按照描述的步驟進行操作(sudo apt-get install openjdk-7-jre,sudo mv /opt

2018-12-10 10:29:37

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

你好:我沒有通過ZC702評估套件和Vivado 2013.2中的PMOD1上的SPI外設通過EMIO獲得預期的行為。我已閱讀AR#47511我必須在MHS文件中更改或添加一些代碼行,但我在項目目錄中找不到MHS文件。 Vivado不使用MHS文件嗎?我怎么解決這個問題?

2019-11-08 12:12:06

嗨,我正在尋找有關如何使用Xilinx Vivado創建Hard宏的示例。了解如何在設計中修復路由并在閱讀pdf(下面)時,提到可以根據要求提供示例,這將非常有幫助。我是否可以收到一些此實施的示例

2018-11-12 14:42:01

在我們的設計中,Vivado實現結果因運行而異。我們想要從“最佳”實現中鎖定兩個模塊的放置信息。然后將其保存以備將來運行。我們知道這可能與pblock和分層設計有關。但是,分層設計文檔并不十分

2018-10-18 14:36:14

嗨,我有一個關于Vivado 2017.4實驗版的問題。在發行說明中,它被描述為“注意:Lab Edition安裝程序可以在32位或64位計算機上運行。”我在32位機器上下載了2017.4實驗室

2019-01-07 10:31:57

嗨,當我在Linux系統上安裝Vivado 2017.2時,由于與Vivado安裝無關的原因,系統在安裝過程中崩潰了。這給我留下了一個帶有“半安裝”vivado的系統,一些文件到位,但很多都丟失了

2018-12-25 11:10:25

你好ISE的合成與實現,最終資源利用分析報告正常。現在在Vivado中,在實現邏輯優化(opt_design)的第一步(實現)中投入了大量資源來優化模塊(建議邏輯單元不加載),但是當ISE實現沒有被

2018-10-24 15:23:00

你好,我從Digilent購買了一塊ZYBO板,并兌換了Vivado Design Suite附帶的優惠券。今天我試圖實例化一個VIO核心,我的許可證出錯了。如何訪問Vivado Analyzer

2018-12-14 11:35:26

大家好,我已經安裝了Vivado 2016.3。在安裝過程中,我檢查了Spartan 7包。但是當我啟動Vivado時,目錄中沒有Spartan 7設備。 Vivado目前是否普遍支持Spartan 7?或者我是否通過安裝工具犯了一些錯誤?最好的祝福,埃米爾

2020-08-11 07:25:38

您好,我正在為Vivado 2015.3課程做一個項目。該項目是邊界掃描測試。我編寫了所有VHDL代碼并嘗試實現。但是,實施還沒有發生。我一直得到錯誤:[Synth 8-4169]使用條款中的錯誤

2019-04-15 12:38:48

你好,有沒有辦法在Vivado 2016.1中關閉特定的DRC違規或警告?其次是AR#63997的方向,我試過:set_property嚴重性警告[get_drc_checks RTSTAT-2

2018-10-26 15:03:13

我的目標是實現一個給定的C算法是一個FPGA。所以,我最近得到了一個Zedboard,目標是實現該算法是PL部分(理想情況下PS中的頂級內容)。我在FPGA領域和編寫VHDL / Verilog方面

2020-03-24 08:37:03

你好我正在嘗試在vivado HLS中創建一個IP,然后在vivado中使用它每次我運行Export RTL我收到了這個警告警告:[Common 17-204]您的XILINX環境變量未定義。您將

2020-04-03 08:48:23

讓我知道vivado在zed fpga中創建coe文件,是否可以在project / srcs目錄中找到它

2020-04-15 10:04:17

Vivado不斷在vivado項目目錄中創建new.jou和.log備份文件。如何禁用這些文件的創建和/或備份?以上來自于谷歌翻譯以下為原文Vivado is constantly creating

2018-12-21 11:07:52

單擊“開始”菜單中的“Vivado 2016.1”按鈕后:然后我點擊修復,然后:但事情并沒有好轉,因為Vivado沒有按照應有的方式發布,相反,幾秒鐘之后,這就出現了:經過多次嘗試但只得到了相同

2018-12-21 11:02:24

文件中匹配目標的時候,在可行的情況下更傾向于使用正則表達式。本文就介紹一下我常使用的正則表達式和一些在Vivado中應用的特殊之處,同時也有個別自己尚未解決的問題。

2021-01-26 07:03:16

今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

上一篇《Tcl 在 Vivado 中的應用》介紹了 Tcl 的基本語法以及如何利 用 Tcl

2023-06-28 19:34:58

《Vivado使用誤區與進階》電子書匯集了賽靈思專家團隊在客戶支持時所碰見的諸多實際案例,以及相對應的解決方案;還有多年總結下來的設計技巧與代碼參數詳解。是您學習和掌握Vivado開發套件的一本不可多得的實戰指導資料。

2016-08-03 19:37:24 84

84 可能會讓您無所適從,您真的了解和掌握了這款工具?還有全新的系統設計方法學?您真的體會到了Vivado設計套件的強大與高效嗎? 《Vivado設計誤區與進階》匯集了賽靈思專家團隊在多年的客戶支持工作中所積累的經驗和方案,每個小文章都力圖選取

2017-02-09 04:32:12 197

197 在linux系統上實現vivado調用VCS仿真教程 作用:vivado調用VCS仿真可以加快工程的仿真和調試,提高效率。 前期準備:確認安裝vivado軟件和VCS軟件 VCS軟件最好安裝

2018-07-05 03:30:00 10733

10733

此篇文章里,我們將通過使用InTime來檢驗Vivado 2017.1和Vivado2016.4之間的性能對比。 概要:分別進行了3個Vivado 2017.1對Vivado2016.4的性能測試

2018-07-04 11:23:00 9674

9674

無論此刻你是一個需要安裝Xilinx Vivado工具鏈的入門菜鳥,還是已有license過期的Vivado老鐵,今兒咱就借著這篇文章,把學習「Vivado如何獲取License」這檔子事兒給說通透咯~ 手把手教程,分三部分講述。

2018-07-03 09:54:00 58889

58889

vivado設計套件資料

2017-10-31 09:49:03 43

43 其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。 基本的FPGA設計實現流程 FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。

2017-11-18 01:48:01 3295

3295

Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握

2017-11-18 03:52:01 4675

4675

1 Vivado HLS簡介 2創建一個Vivado-HLS工程 2.1打開Vivado HLS GUI 2.2創建新工程 在 Welcome Page, 選擇Create New Project

2017-12-04 10:07:17 0

0 在實際工程中,如何利用好這一工具仍值得考究。本文將介紹使用Vivado HLS時的幾個誤區。

2018-01-10 14:33:02 19813

19813

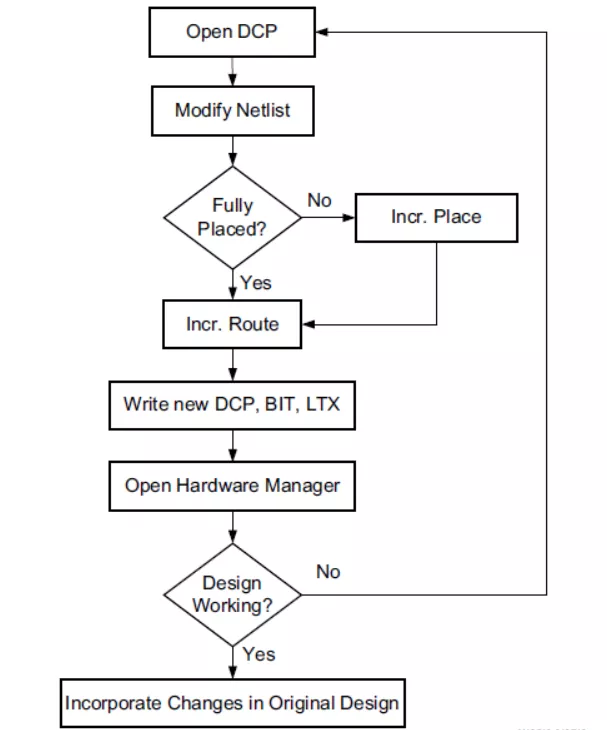

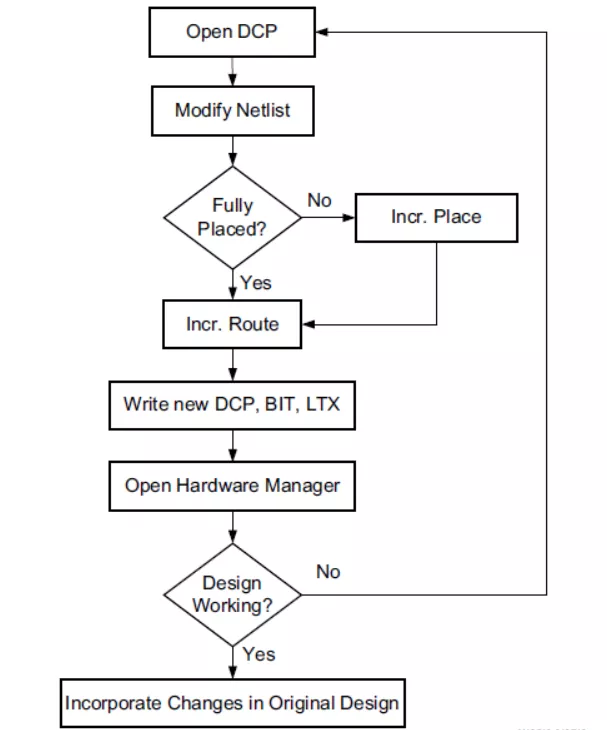

了解如何在Vivado中執行工程變更單(ECO)。

本視頻將向您介紹ECO的常見用例,我們推薦的完成ECO的流程,優勢和局限性,并將演示功能設計的ECO。

2018-11-21 06:40:00 4647

4647

本視頻重點向您介紹了Vivado設計套件2017.3版本中的增強功能,包括操作系統和器件支持,高級增強功能,加速集成,實施和驗證的各種升級和改進。歡迎收看本視頻,了解更多有關

Vivado設計套件的新功能。

2018-11-21 06:15:00 3374

3374

了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量編譯流程。

2018-11-20 06:55:00 2340

2340 了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量編譯流程。

2018-11-20 06:56:00 2512

2512 該視頻介紹了2017.1 Vivado設計套件中的新外觀。

它討論了變更的動機,介紹了一些亮點,并演示了一些功能。

2018-11-20 06:27:00 2355

2355 了解Vivado Design Suite 2016中的新功能。

我們將回顧新的UltraFast方法檢查,HDL模塊參考流程和用于IPI設計的SmartConnect IP,語言模板增強,Xilinx參數化宏(XPM),GUI改進

2018-11-20 06:22:00 2247

2247 2015年Club Vivado開發者大會的預覽。

2018-11-20 11:51:25 992

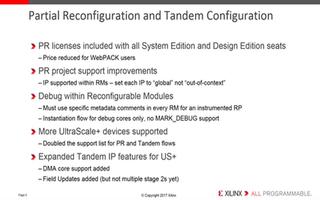

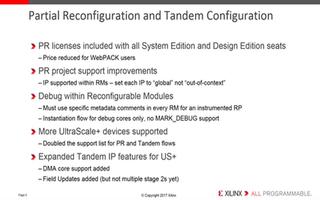

992 此視頻重點介紹了新的Vivado Design Suite 2017.1版本的增強功能,包括操作系統和設備支持,新外觀,部分重新配置廣泛可用性等等......

2018-11-30 06:20:00 2537

2537

了解如何使用Vivado的創建和封裝IP功能創建可添加自定義邏輯的AXI外設,以創建自定義IP。

2018-11-29 06:48:00 6801

6801

了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量編譯流程。

2018-11-29 06:32:00 3340

3340 了解使用Vivado 2016.1中引入的ECO流程進行調試的好處,以及在ECO布局中替換ILA調試探針所需的步驟。

2018-11-29 06:01:00 3316

3316

了解Vivado設計套件中的一些廣泛的設計分析功能,旨在識別可能影響性能的設計中的問題區域。

2018-11-27 07:10:00 4613

4613 了解新Vivado Lab Edition的功能和優點,并熟悉其安裝和典型使用流程。

2018-11-30 06:40:00 17064

17064 了解如何使用Vivado設計套件的電路板感知功能快速配置和實施針對Xilinx評估板的設計。

2018-11-26 06:03:00 3062

3062 物理優化是Vivado實現流程中更快時序收斂的重要組成部分。

了解如何在Vivado中應用此功能以交換運行時以獲得更好的設計性能。

2018-11-23 06:06:00 3728

3728 了解如何使用2014.1中引入的新激活許可為Vivado工具生成許可證。

另外,了解Vivado 2014.1中的許可更改如何影響您,以及如何在激活客戶端中使用新的Vivado License Manager

2018-11-22 07:10:00 2614

2614 了解如何使用Vivado在設備啟動時及其周??圍進行調試。

你也會學習

使用Vivado 2014.1中引入的Trigger at Startup功能來配置和預先安裝a

調試核心并觸發設備啟動時或周圍的事件......

2018-11-22 07:05:00 4084

4084 了解Vivado實現中2015.3中的新增量編譯功能,包括更好地處理物理優化和自動增量編譯流程。

2018-11-30 19:24:00 4251

4251 在Vivado Design Suite中,Vivado綜合能夠合成多種類型的屬性。在大多數情況下,這些屬性具有相同的語法和相同的行為。

2019-05-02 10:13:00 3750

3750 中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-06 06:12:00 3450

3450

關于Vivado Dashboard的功能可閱讀這篇文章(Vivado 2018.3這個Gadget你用了嗎)Vivado 2019.1的Dashboard功能進一步增強。

2019-06-12 14:49:24 7677

7677

核的使用。 ? ? BRAM是FPGA定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的內部,是FPGA實現各種存儲功能的主要部分,是真正的雙讀/寫端口的同步的RAM

2020-12-29 15:59:39 9496

9496 帶大家一起體驗一下Vivado 的ECO流程,以vivado自帶的Example Design為例, 直接用TCL命令修改網表,在正常的寄存器路徑之間加一級LUT。 1. 打開Vivado 界面 2. 打開

2020-10-26 09:45:23 3366

3366

這里帶大家一起體驗一下Vivado 的ECO流程,以vivado自帶的Example Design為例, 直接用TCL命令修改網表,在正常的寄存器路徑之間加一級LUT。

2020-11-29 11:04:53 3879

3879

我們都知道FPGA的實現過程分為2步:分析綜合與布局布線后就可以產生目標文件,這兩個步驟中間有個非常重要的文件,那就是-網表。 下圖是Vivado中網表列表示例: ? ? ? ? ? Vivado

2021-05-14 10:46:53 3783

3783

本篇文章來自賽靈思高級工具產品應用工程師 Hong Han. 本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado. 對于Vivado實現階段策略的指定

2021-08-13 14:35:56 3900

3900 Vivado License Manager在使用Vivado License Manager時,如果通過如下圖所示方式指定license的路徑時,要保證路徑僅包含ASCII字符而沒有中文字

2021-09-12 15:15:19 5055

5055 【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 26

26 在《vivado使用誤區與進階》中,提到了一種叫 UltraFAST 的設計方法。

2022-03-30 11:53:26 3017

3017 Vivado可以導出腳本,保存創建工程的相關命令和配置,并可以在需要的時候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠遠小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級到Vivado 2020.2為例,討論如何升級Vivado工程腳本。

2022-08-02 10:10:17 1542

1542 ECO 指的是 Engineering Change Order ,即工程變更指令。目的是為了在設計的后期,快速靈活地做小范圍修改,從而盡可能的保持已經驗證的功能和時序。ECO 是從 IC 設計領域繼承而來,Vivado上 的 ECO 便相當于 ISE 上的 FPGA Editor。

2022-08-02 09:18:04 2945

2945

Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-19 16:20:51 1309

1309 Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 958

958 對 FPGA 設計的實現過程必須以滿足 XDC 中的約束為目標進行。那我們如何驗證實現后的設計有沒有滿足時序要求?又如何在開始布局布線前判斷某些約束有沒有成功設置?或是驗證約束的優先級?這些都要用到 Vivado 中的靜態時序分析工具。

2023-05-04 11:20:31 2368

2368

今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 674

674

關于 Tcl 在 Vivado中的應用文章從 Tcl 的基本語法和在 Vivado 中的 應用展開,繼上篇《用 Tcl 定制 Vivado 設計實現流程》介紹了如何擴展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

vivado開發軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學者進行仿真實驗。

2023-07-18 09:06:59 2137

2137

電子發燒友網站提供《Vivado Design Suite教程:動態功能交換.pdf》資料免費下載

2023-09-14 15:13:43 0

0 電子發燒友網站提供《Vivado設計套件用戶:使用Vivado IDE的指南.pdf》資料免費下載

2023-09-13 15:25:36 3

3 定制的RAM資源,有著較大的存儲空間,且在日常的工程中使用較為頻繁。BRAM以陣列的方式排布于FPGA的內部,是FPGA實現各種存儲功能的主要部分,是真正的雙讀/寫端口的同步的RAM。 本片

2023-12-05 15:05:02 317

317

正在加载...

電子發燒友App

電子發燒友App

評論