摘 要: 隨著FPGA的廣泛應(yīng)用, 其實現(xiàn)的功能也越來越多, FPGA 的動態(tài)重構(gòu)設(shè)計就顯得愈發(fā)重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、時序要求的基礎(chǔ)上, 設(shè)計了基于CPLD 的FPGA 快速動態(tài)重構(gòu)方案, 實現(xiàn)了同一硬件平臺下多個FPGA 設(shè)計版本的在線動態(tài)配置和功能重構(gòu), 該技術(shù)已在工程中成功應(yīng)用。

1 引 言

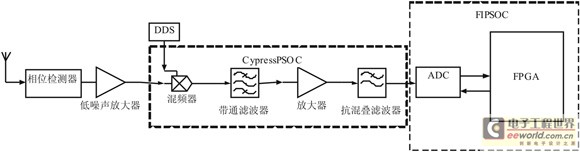

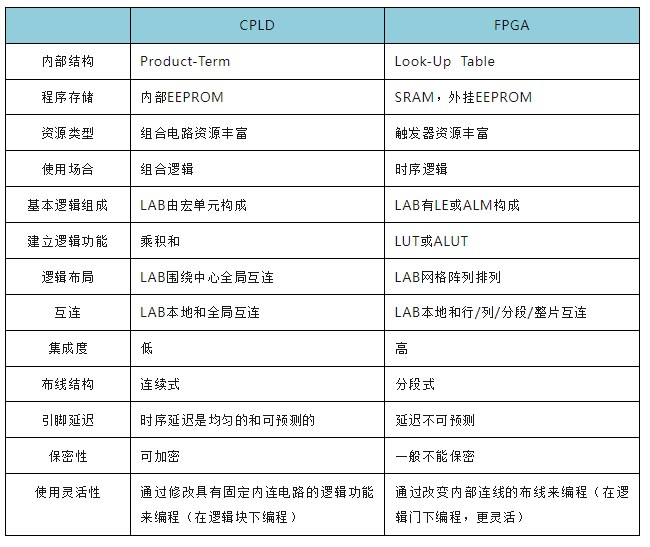

軟件無線電( SDR )的設(shè)計思想已成為現(xiàn)今通信的熱點, 它以通用、標(biāo)準(zhǔn)、模塊化的硬件處理平臺為依托, 通過軟件編程來實現(xiàn)無線電臺的各種功能。硬件處理平臺設(shè)計為通信系統(tǒng)的關(guān)鍵之一,通用性是其首要考慮的問題, 因為只有具有通用性,才能用軟件實現(xiàn)多種功能。由于FPGA ( Field Programmable Gate Array)的現(xiàn)場可編程特性, 故目前硬件處理平臺的設(shè)計基本上都采用了FPGA + CPU 的架構(gòu), FPGA主要用來完成并行和高速處理的功能。

隨著微電子技術(shù)的發(fā)展, FPGA 可提供的資源日益強(qiáng)大, 達(dá)到上千萬門級, 其承擔(dān)的功能越來越多, 同時, 電子設(shè)備對成本、功耗和體積的要求也越來越高, 矛盾就不可避免地產(chǎn)生。通過實時地動態(tài)重新配置FPGA 來加載不同的功能軟件, 實現(xiàn)功能切換, 是解決此問題的較好方法, 可實現(xiàn)幾者之間的均衡。目前, 實現(xiàn)FPGA 動態(tài)重新配置比較通用的方法有兩種: 一是通過DSP或其它CPU 讀取存儲器中的比特( bit)文件對FPGA 進(jìn)行串行加載或并行加載, 其缺點是加載速率一般很低, 不能實現(xiàn)狀態(tài)高速切換; 二是使用Xilinx 公司的專用配置芯片XCFxxP系列, 但由于其存儲容量有限, 對于功能復(fù)雜的系統(tǒng), FPGA 的軟件版本多, 需要多片專用配置芯片, 不適用于印制板尺寸很小、布局緊張的場合。

針對上述問題, 本文提出了基于CPLD的FPGA快速動態(tài)加載方案, 實現(xiàn)了FPGA 的功能重構(gòu), 克服了上述兩種方式的缺點。

2 Vertex II Pro的配置流程

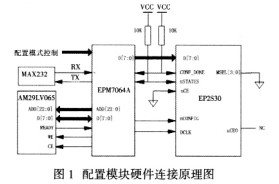

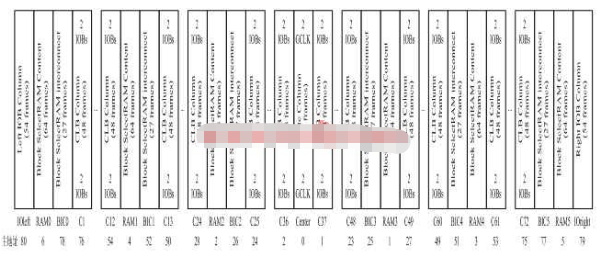

Xilinx 公司的FPGA 配置存儲器是易失性的 , 每次上電時都要將存儲在外部存儲器中的位流文件加載到FPGA中才能正常工作。其配置過程主要有4個階段: 清除配置存儲器、初始化、加載配置數(shù)據(jù)、器件啟動 , 其流程如圖1所示。

配置存儲器清除階段, IN IT _B 和DONE 管腳變低。當(dāng)配置存儲器清除完畢后, IN IT _B 管腳變高。如果通過拉低PROG _B 管腳來清除配置存儲器, 則PROG _B 的低脈沖時間至少大于300 ns, 無最大值。上電時序如圖2所示。

2. 2 初始化

在初始化階段, FPGA 首先釋放對IN IT_B 的控制權(quán)。此時, 如果外部將IN IT _B 拉低, FPGA 將延遲配置進(jìn)程, IN IT _B上升沿采樣配置方式管腳M0、M1、M2, 根據(jù)不同的配置方式, 開始配置進(jìn)程。在此期間, 不需要暫停時間或等待周期, 但I(xiàn)N IT _B 變高后, 也不會立即開始配置, 需要FPGA 從位流文件中收到同步字后, 其配置邏輯才開始處理數(shù)據(jù)。

2. 3 加載配置數(shù)據(jù)

內(nèi)部配置存儲器被分成叫做“幀”的塊, 真正寫進(jìn)配置存儲器的位流部分叫做"數(shù)據(jù)幀", "幀"的大小和數(shù)量隨器件而變。一旦配置進(jìn)程開始, FPGA接收數(shù)據(jù)幀, 最后一個數(shù)據(jù)幀接收完后進(jìn)行CRC 校驗。當(dāng)CRC校驗出錯, FPGA 將IN IT _B 管腳置低,指示CRC 出錯, 同時FPGA 放棄配置進(jìn)程, 不啟動工作, 直至PROG _B變低來重新復(fù)位配置邏輯; CRC校驗正確, 最后一個數(shù)據(jù)幀下載后, 將給全局復(fù)位信號( GSR)一個脈沖, 它將在進(jìn)入啟動之前復(fù)位器件內(nèi)的全部寄存器。

2. 4 器件啟動

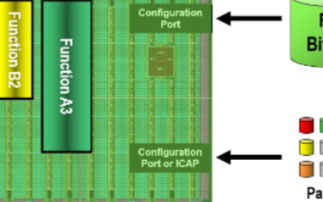

啟動是配置的最后一個階段, 是從配置狀態(tài)到工作狀態(tài)的一個轉(zhuǎn)換過程, 如圖3所示。啟動次序是0~ 7的一個8段序列狀態(tài)機(jī), 可以用軟件改變次序, 該階段完成以下任務(wù): 釋放DONE 管腳; 撤消GTS, 激活所有的I/O; 使能GWE, 允許所有的RAM和觸發(fā)器改變狀態(tài); 使能EOS, 啟動結(jié)束標(biāo)志總是設(shè)在第7段, 其為內(nèi)部標(biāo)志, 用戶無法介入。

3 CPLD動態(tài)配置FPGA的方法

Vertex II Pro 系列有4 種配置模式: 主串行模式、主并行模式、從串行模式和從并行模式。其中主從指的是配置時鐘的方向, 主模式配置時鐘由FPGA內(nèi)部振蕩器產(chǎn)生, 從模式則由外部提供配置時鐘; 串行是指配置數(shù)據(jù)逐位傳輸, 并行是指配置數(shù)據(jù)以字節(jié)傳輸。為了便于有效地控制配置流程和快速加載, 這里選擇從并行模式。

FPGA 最后生成的執(zhí)行文件有二進(jìn)制和ASC II文本形式兩種。為了便于燒寫進(jìn)FLASH, 方案選擇生成ASC II文本形式的位流文件, 它是用ASCII碼0或1表示生成的設(shè)計文件中的0或1信息。

整個步驟如下:

( 1)將多個設(shè)計文件版本按照分配好的地址燒寫入FLASH;

( 2) CPLD 內(nèi)部的控制邏輯首先將FPGA 的PROG_B管腳拉低必要的時間, 清除FPGA 中配置存儲器的內(nèi)容, 同時在PROG _B 變高后繼續(xù)拉低FPGA 的IN IT _B 一段必要的時間然后置高, 采樣配置方式管腳M0、M1、M2;

( 3)接著CPLD 中的地址產(chǎn)生器輸出當(dāng)前版本的起始地址, 對FLASH 進(jìn)行讀操作, 從FLASH 中讀取的數(shù)據(jù)在配置時鐘的作用下輸給FPGA 的數(shù)據(jù)配置管腳, 然后FLASH 的文件地址加1, 這樣依次將數(shù)據(jù)輸給FPGA, 直至配置過程結(jié)束;

( 4)配置數(shù)據(jù)輸完后, 如果CRC 校驗正確, FPGA則進(jìn)入啟動階段, FPGA 的DONE 信號變高, 結(jié)束CPLD 內(nèi)部的配置程序, FPGA 進(jìn)入工作狀態(tài);

( 5)如果CRC 校驗不正確, FPGA 拉低IN IT_B,放棄配置, 這時CPLD會檢測到IN IT_B 信號的下降沿, 復(fù)位配置程序, 并將FPGA的PROG_B 管腳再次拉低, 重新開始配置。

配置過程中, 最大頻率主要由FLASH的讀取時間和數(shù)據(jù)輸入的建立時間決定。FLASH 的讀取時間一般遠(yuǎn)遠(yuǎn)大于數(shù)據(jù)輸入的建立時間, 因此它是造成配置速率不能提高的瓶頸, 從而也決定了最大配置頻率。目前FLASH 的隨機(jī)讀取時間通常為70~90 ns, 因此FPGA 的最大配置頻率在10MHz左右。

4 應(yīng) 用

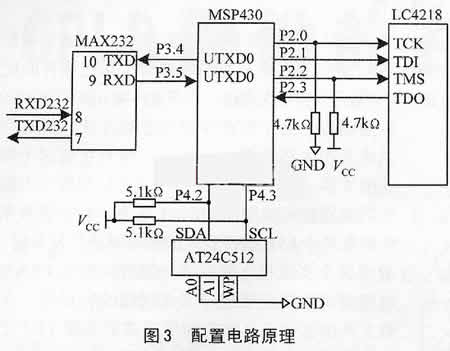

在工程中, 利用大容量FLASH 芯片和CPLD成功實現(xiàn)了對300萬門FPGA XC2VP30 的動態(tài)加載,其實現(xiàn)方法是將FPGA 的加載模式設(shè)為從并模式,加載版本設(shè)為4個, 利用DSP事先將4個軟件版本燒寫進(jìn)FLASH。

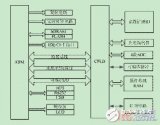

設(shè)計采用一片CPLD來控制XC2VP30的配置邏輯和版本管理。當(dāng)DSP收到外部送來的模式切換命令后確定加載版本, 然后送給CPLD版本切換信號和所需的版本信息。這時CPLD 啟動配置邏輯程序?qū)PGA進(jìn)行加載。加載過程中, 如果CRC 校驗出錯, IN IT_B變低, CPLD檢測到INIT_B下降沿后重新加載FPGA。如果連續(xù)檢測到5個INIT_B 下降沿, CPLD放棄加載, 上報錯誤信息。其工作原理如圖4所示。

在本應(yīng)用中, FPGA 的加載時鐘選擇的是10MHz, 而XC2VP30 的配置位流文件大小為11589984 bit, 完成一次加載的時間大約需要145ms。測試表明, 本加載方法穩(wěn)定可靠, 性能良好。

5 小 結(jié)

本文設(shè)計的基于CPLD的FPGA 快速動態(tài)重構(gòu)方法, 加載速度明顯快于DSP或其它CPU 上秒的加載速度。由于FLASH 具有容量大封裝小的特點, 使這種配置方法在小型化硬件平臺設(shè)計中占有優(yōu)勢,而且以后隨著FLASH 讀取時間的縮短和FPGA 配置數(shù)據(jù)位數(shù)的擴(kuò)展, 加載時間會大大地縮短, 更能滿足設(shè)計要求。同時, 這種方法不依賴國外專用配置芯片, 提高了硬件設(shè)計靈活性。

電子發(fā)燒友App

電子發(fā)燒友App

評論