在 Flow Navigator 中點擊設置, 然后選擇Synthesis,或者 selectFlow Settings Synthesis Settings。 如圖1所示: 1、綜合約束 在設置

2020-11-23 14:16:36 4238

4238

、Verilog 2005、VHDL 2008、混合語言中的可綜合子集,以及XDC設計約束文件(基于工業標準的SDC文件),此外還支持RTL屬性來控制綜合細節。 綜合設置選項 在Flow Navigator中點

2020-12-29 14:07:42 5432

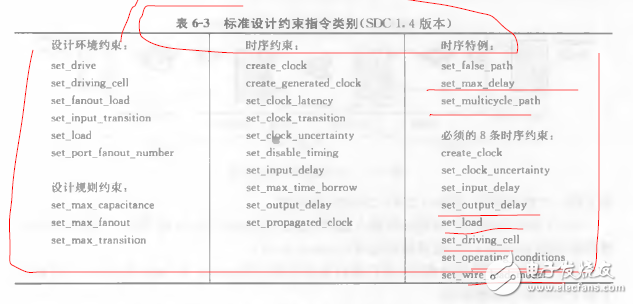

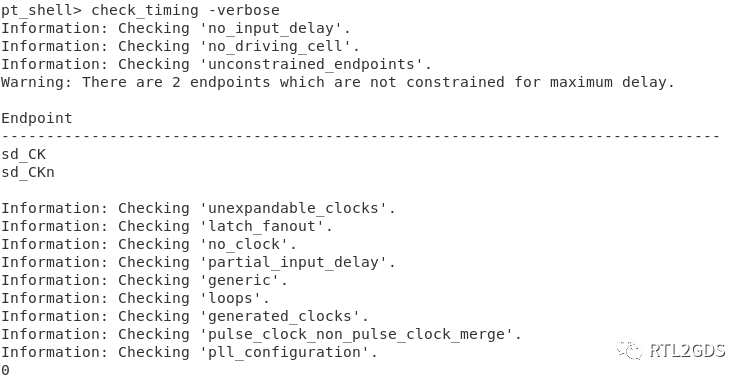

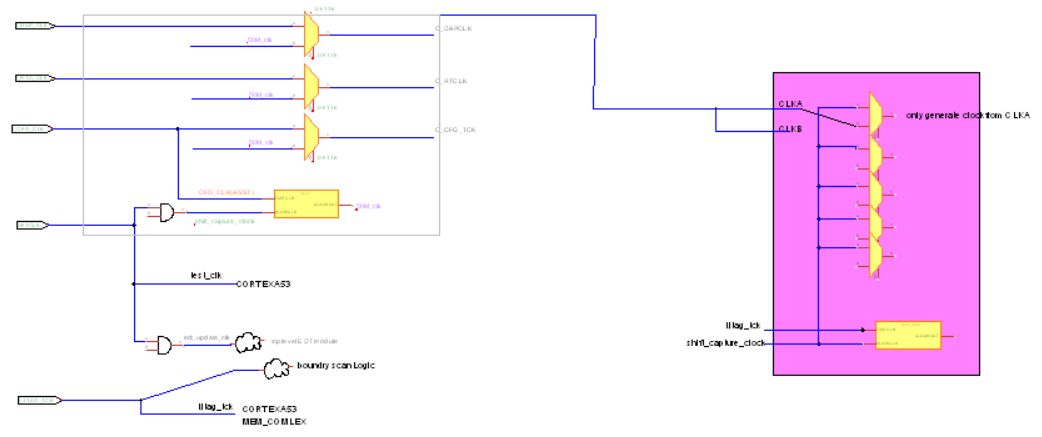

5432 時序約束的目的就是告訴工具當前的時序狀態,以讓工具盡量優化時序并給出詳細的分析報告。一般在行為仿真后、綜合前即創建基本的時序約束。Vivado使用SDC基礎上的XDC腳本以文本形式約束。以下討論如何進行最基本時序約束相關腳本。

2022-03-11 14:39:10 8731

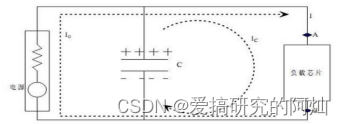

8731 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 使用SDC命令create_clock創建時鐘,時鐘周期20,占空比50%的時鐘信號;

2022-11-08 09:12:02 5409

5409 SystemVerilog引入了interface,這里我們從可綜合的RTL代碼的角度聊聊interface。

2023-10-12 09:06:45 752

752

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數據和時鐘傳輸路徑是由相應的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

你好: 現在我使用xilinx FPGA進行設計。遇到問題。我不知道FPGA設計是否符合時序要求。我在設計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應該被禁止。我

2019-03-18 13:37:27

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

FPGA的reset信號需要加什么SDC約束呢?

2023-04-23 11:38:24

文件,再交給上述工具進行處理或分析。(4)仿真器支持幾乎所有的Verilog HDL語法,而不僅僅是常用的RTL的描述,應當利用這一點使測試程序盡可能簡潔、清楚,篇幅長的要盡量采用task來描述。3.2

2020-05-15 07:00:00

1. 適用范圍 本文檔理論適用于Actel FPGA并且采用Libero軟件進行靜態時序分析(寄存器到寄存器)。2. 應用背景 靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計

2012-01-11 11:43:06

FPGA高級時序綜合教程The UCF FileUCF =用戶約束文件( User Constraints File )可以用文本編輯器和XilinxConstraints Editor (GUI

2012-08-11 11:28:50

今天在做FPGA工程時,在分析綜合時出現警告Warning: 1 hierarchies have connectivity warnings - see the Connectivity

2016-06-24 19:38:36

綜合布線系統憑借尖端的技術與智能化設計,具有無與倫比的優越性。那么誰知道綜合布線系統中的屏蔽技術具體有哪些解決方案嗎?

2019-08-06 06:28:23

有沒有人遇到在DC綜合后分析建立時間時序,關鍵路徑時序違例是因為起始點是在時鐘的下降沿開始驅動的,但是設計中都是時鐘上升沿觸發的。在線等待各位大牛解惑!很急 求大神幫忙!

2015-01-04 15:17:16

級(RTL)的描述轉化為門級描述。隨著以行為設計為主要標志的新一代系統設計理論的不斷成熟,能夠將系統行為級描述轉化為RTL描述的高層次綜合技術不斷涌現。 作為現代集成電路設計的重點與熱點,FPGA

2008-06-26 16:16:11

RTL視圖。 【Write Timing Constraints】:寫時序約束。該參數僅對FPGA有效,用來設置是否將HDL源代碼中用于控制綜合的時序約束傳給NGC網表文件,該文件用于布局和布線

2012-02-24 10:44:57

對于一個rtl設計,ISE place & route 之后會生成sdf文件,那么,如果在綜合之前對 rtl設計,添加一定的約束,所生成sdf文件是否有變化?sdf文件和在綜合前的約束文件有關系么?

2015-02-09 15:19:27

信息:運行Quartus素分析與綜合信息:版本15.1.0建185 10 / 21 / 2015 SJ標準版信息:處理開始:1月13日2017 20:55:38信息:命令:quartus_map

2019-02-12 02:42:44

文件(XDC文件),它包含用于時序分析的“create_clock”和“set_input_jitter”約束。在ISE 14.7和Spartan-3 FPGA中,我可以使用稱為“時鐘向導”的IP來

2019-08-02 09:54:40

學習。個人學習的時候可以根據實際情況選擇最高至Vivado2019.1。(從Vivado2019.2開始,PS開發使用Vitis,沒有SDK了)第1章 FPGA技術分析 / 11.1 FPGA內部結構

2020-10-21 18:24:48

的設計方法: 加比較完善的約束條件,然后通過 RTL仿真,時序分析,后仿真來解決問題,盡量避免在 FPGA 電路板上來調試。Altera最先意識到這一點,它采用了 Synopsys 的SDC 格式

2012-03-05 15:02:22

轉自:VIVADO時序分析練習時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習VIVADO軟件時序分析的筆記,小編這里

2018-08-22 11:45:54

Design Compiler時一個約束驅動(constraint-driven)的綜合工具,它的結果與設計者施加的約束條件密切相關。

2021-07-29 07:56:56

為什么quartus綜合沒有報錯而modelsim rtl仿真就報錯了

2015-09-24 11:02:16

當你寫HDL代碼的目的,是需要得到FPGA的實際電路功能,也即得到FPGA的網表,用于下載到FPGA器件中,實現這個電路。此時,這段代碼是用于綜合目的的。用于綜合目的的代碼,在Quartus工具中

2018-02-26 15:32:30

綜合是將我們的設計轉化為FPGA可以讀懂的配置文件的第一個步驟。本文努力從0基礎開始向大家說明綜合的基本知識和高級技巧。話說所有的功能都有它應用的環境。在了解某個按鈕選項有某個功能的時候,我們更應該

2018-08-08 10:31:27

的設計計劃,例如完整的和精確的時序約束和時鐘規范?節約時間的設計技術,例如為更好的性能結果,整合設計的各個部分而編寫嚴謹的RTL代碼,提出最高性能挑戰,當你之后調整設計時減少迭代運行時間?綜合和擺放以及路由

2021-05-18 15:55:00

、串口通信等的交互和控制。圖 2 FPGA程序設計結構層次圖綜合頂層模塊得到如下如3所示的RTL原理圖,圖中5個紅框對應上述五大模塊。圖 3 系統頂層綜合RTL原理圖2.3 子模塊設計2.3.1 數據

2018-08-07 10:08:19

作者:張海亮ITS(智能交通)是將先進的傳感器技術、通訊技術、數據處理技術、網絡技術、自動控制技術、信息發布技術等有機地運用于整個交通運輸管理體系而建立起的一種實時的、準確的、高效的交通運輸綜合管理

2019-07-12 06:23:27

隨著設計復雜性增加,傳統的綜合方法面臨越來越大的挑戰。為此,Synplicity公司開發了同時適用于FPGA或 ASIC設計的多點綜合技術,它集成了“自上而下”與“自下而上”綜合方法的優勢,能提供高結果質量和高生產率,同時削減存儲器需求和運行時間。

2019-10-17 06:29:53

,不同的寄存器在時鐘脈沖的激勵下相互配合完成特定的功能,所以要保證不同的寄存器在同一時刻的時鐘脈沖激勵下協同工作,就需要進行時序分析,通過分析得結果對FPGA進行約束,以保證不同寄存器間的時序要求

2017-02-26 09:42:48

大規模FPGA設計中的多點綜合技術

2012-08-17 10:27:46

物理綜合技術是數字電路設計工程師必須要掌握的一項技能,是RTL到物理實現的起點,而物理綜合是一個很復雜的過程,環境、工藝庫設定、時序約束編寫、綜合時序問題分析等等均需要綜合時具有專門的知識和技能,一

2021-06-23 06:59:32

如何使用基于圖形的物理綜合加快FPGA設計時序收斂?

2021-05-06 09:19:08

本文轉載IC_learner - 博客園數字IC之路-SDC篇(一):基本的時序路徑約束_u012675910的博客-CSDN博客_sdc約束 RTL代碼描述了電路的時序邏輯和組合邏輯,即RTL代碼

2022-03-01 06:48:09

怎么借助物理綜合提高FPGA設計效能?

2021-05-07 06:21:18

大家好,至于綜合和實現流程中的“編輯時序約束”(見下文),它們是否應該與相同的文件相關?我可以保留文件,這些文件將在綜合過程中考慮,在實施過程中不予考慮,反之亦然?實際上我在合成流的“編輯時序約束

2018-10-29 11:50:01

綜合性集團,數據量大、分析需求多不說,底下還有多個子公司,數據情況可比一般企業復雜多了。那么,有沒有專做綜合集團數據分析的解決方案?能夠及時滿足總公司、各子公司乃至各部門的數據分析需求,能讓每個

2021-11-02 10:13:58

您好我有一個關于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進行綜合嗎?謝謝

2020-04-13 09:12:32

手工綜合RTL級代碼的理論依據和實用方法時序邏輯綜合的實現方法

2021-04-08 06:06:35

汽車動力與驅動系統綜合分析技術:使用原創資料較多就不一一列舉,望海涵。我原創也不少咯。MAC和PHY可能是集成在CPU中可能獨立,下圖介紹典型的MAC集成,PHY獨立。兩者搭配實現網卡功能

2021-07-22 08:34:36

飛機的油液監測是利用油液分析技術對飛機使用的潤滑油和液壓油進行綜合分析,以獲得飛機發動機的潤滑和磨損情況以及液壓系統的使用情況,進行油液分析可以有效地監測飛機的發動機、起落架、襟副翼和尾翼等關鍵部件的使用情況,檢查并預測飛機的故障,保證飛行的安全。

2019-08-15 06:31:13

明顯,但會影響其它路徑的延遲。因此也要憑借經驗,不斷改變所設的約束值,最終使所有路徑的延遲都能滿足設計要求。3.3對層次間邊界的處理方法硬件描述語言描述的RTL級電路通常是多層次模塊,對其進行綜合后

2013-05-16 20:02:50

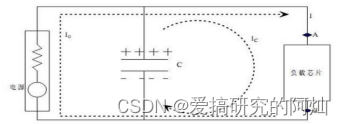

物聯網綜合分析儀(十合一功能版) 物聯網綜合分析儀IOTA-6GMC 物聯網綜合分析儀IOTA-6GMC實現了在單臺設備內,集成了開發設計物聯網和無線傳感網需要的工具和儀器,包括:教學用窄帶,RF

2019-09-29 14:42:52

電網絡分析與綜合

2012-09-14 16:32:07

思路分析寫出基本結構繪圖板綜合項目

2020-11-06 07:42:12

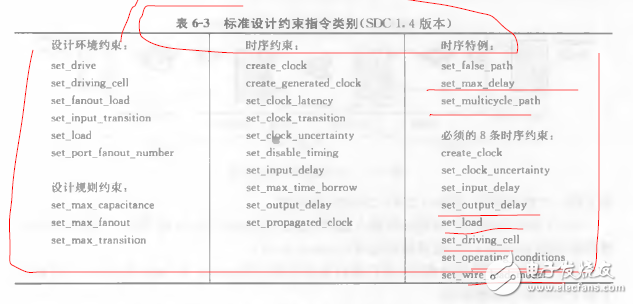

時序約束文件SDC支持哪些約束?

2023-08-11 09:27:15

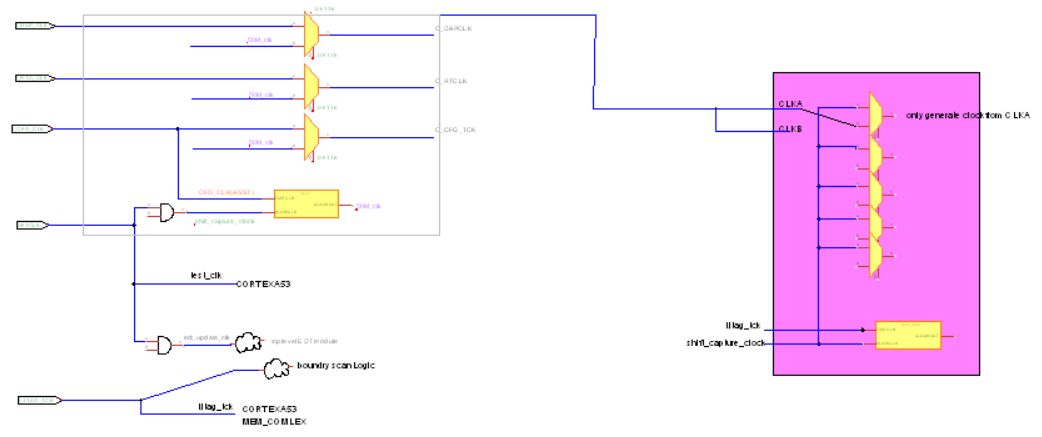

1、跨時鐘域信號的約束寫法 問題一:沒有對設計進行全面的約束導致綜合結果異常,比如沒有設置異步時鐘分組,綜合器對異步時鐘路徑進行靜態時序分析導致誤報時序違例。 約束文件包括三類,建議用戶應該將

2022-11-15 14:47:59

高層次綜合技術原理淺析

2021-02-01 06:04:00

下圖揭示了高層次綜合工作的基本流程,以及它于傳統的RTL綜合流程的對比。接下來將對行為描述,行為綜合,分析與優化三個主要子流程詳細描述。 1、行為描述 當我們把HLS技術的起點立為一種

2021-01-06 17:52:14

一、多參數農藥殘留綜合分析儀簡介:多參數農藥殘留綜合分析儀深芬儀器廠家生產的CSY-N2402AD多參數農藥殘留綜合分析儀包括酶抑制率農藥殘留檢測(24通道)、雙通道膠體金法法農藥殘留檢測

2022-05-16 14:41:35

如何保證RTL設計與綜合后網表的一致性文章簡介:在超大規模數字集成電路的設計中,我們使用邏輯綜合工具來完成從RTL設計到門級網表的轉化。我們希望它綜合出的門級網表

2009-01-23 23:10:52 19

19 針對決策支持系統中對數據綜合分析的需求,提出了一種從數據倉庫的多個主題中抽取數據,生成綜合分析報表的方法,使用戶方便地對多個主題的數據進行對比和分析。論述了報

2009-09-24 11:03:41 7

7 摘要:綜合(Synthesis)的主要功能是在FPGA設計過程中對設計輸入進行分析和優化。隨著FPGA技術的進步,綜合技術也在不斷發展,不斷使用新技術的綜合工具軟件得到重視和使用,Pre

2010-06-07 10:42:50 16

16 ASIC和FPGA設計中的多點綜合技術

盡管在技術發展的每一個時刻做出精確的預言是困難的,但ASIC和FPGA所集成的門數仍象數年前INTEL的Gordon Monre預言的那樣平均每18個月增加一倍.

2010-06-19 10:05:09 11

11 面向ASIC和FPGA設計的多點綜合技術

隨著設計復雜性增加,傳統的綜合方法面臨越來越大的挑戰。為此,Synplicity公司開發了同時適用于FPGA或 ASIC設計的多點綜合技術,它

2009-12-26 14:34:33 563

563 本文介紹了在大規模FPGA設計中可以提高綜合效率和效果的多點綜合技術,本文適合大規模FPGA的設計者和Synplify pro的用戶閱讀。

2012-01-17 10:36:37 38

38 簡單的分析綜合處理器

2017-09-22 14:24:20 5

5 對一種單圖像向導濾波器的高性能FPGA設計結構進行了分析,發現其中的均值濾波器存在設計缺陷,據此提出了一種向導濾波器的整數FPGA設計結構。通過改變均值濾波器的數據累加順序,減少了存儲資源

2017-11-22 15:43:12 12

12 介紹FPGA約束原理,理解約束的目的為設計服務,是為了保證設計滿足時序要求,指導FPGA工具進行綜合和實現,約束是Vivado等工具努力實現的目標。所以首先要設計合理,才可能滿足約束,約束反過來檢查

2018-06-25 09:14:00 6374

6374 該培訓視頻涵蓋了SDAccel RTL內核向導,并詳細介紹了打包RTL設計,構建FPGA設計和生成Amazon FPGA映像(AFI)所涉及的步驟。

2018-11-21 06:30:00 2105

2105 了解時序約束向導如何用于“完全”約束您的設計。

該向導遵循UltraFast設計方法,定義您的時鐘,時鐘交互,最后是您的輸入和輸出約束。

2018-11-29 06:47:00 2702

2702

了解如何將Altera的SDC約束轉換為Xilinx XDC約束,以及需要更改或修改哪些約束以使Altera的約束適用于Vivado設計軟件。

2018-11-27 07:17:00 4611

4611 STA貫穿設計過程的各個階段,從RTL邏輯綜合到布局、時鐘樹綜合、布線和反標,直到tape_out。每一次分析的目的都是為了檢查當前設計的結果是否滿足設計的約束條件。

2019-11-02 10:59:02 3622

3622

約束條件可以使綜合布線工具調整映射和布局布線過程,使設計達到時序要求。例如用OFFSET_IN_BEFORE約束可以告訴綜合布線工具輸入信號在時鐘之前什么時候準備好,綜合布線工具就可以根據這個約束調整與IPAD相連的Logic Circuitry的綜合實現過程,使結果滿足FFS的建立時間要求。 附加時序

2021-10-11 10:23:09 4861

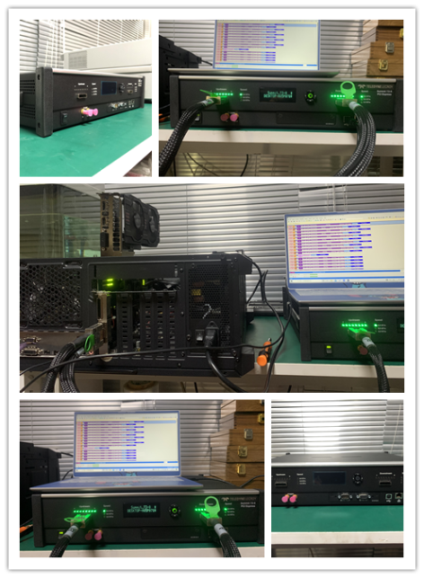

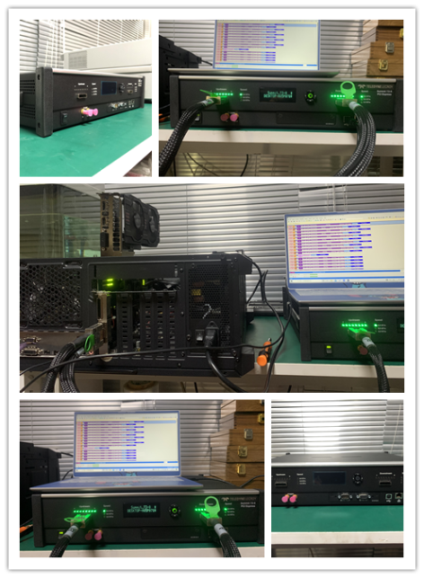

4861

Summit T3-8系統是一個綜合分析工具,用于顯示和分析PCI-express3.1總線的數據流量規范。

2022-03-11 14:44:34 1541

1541 RTL 分區方法是芯片綜合能夠如此快速和有效的主要原因。通過在更高的層次上運行,這種方法一次智能地綜合和計時設計一個分區。然后,在滿足時序之前,它會重新綜合、替換(并更新全局路由)并重新劃分設計的各個部分,直到滿足約束條件。

2022-06-09 16:03:35 1866

1866 Quarus Ⅱ工具提供四種手段分析邏輯綜合結果,包括:RTL Viewer、Technology Viewer、PowerPlay Power Analyzer Tool、State Machine Viewer。

2022-08-25 10:53:03 913

913 ? ? ?什么是 綜合熱分析儀 ?它是一款用于材料科學領域的分析儀器,能夠同時采集DSC和TG信號的一種分析儀。綜合熱分析儀是熱重—差熱聯用熱分析儀器,它是在程序溫度控制下,測定和記錄物質在加熱

2022-10-13 10:59:18 1057

1057

利用工具將RTL代碼轉化為門級網表的過程稱為邏輯綜合。綜合一個設計的過程,從讀取RTL代碼開始,通過時序約束關系,映射產生一個門級網表。

2022-11-28 16:02:11 1822

1822 常規的陣列天線方向圖綜合是基于陣因子分析法,且不考慮單元之間電磁耦合的一種快速分析手段。本次推文則簡單闡述一個基于HFSS的線陣綜合實例。

2022-12-05 11:38:55 858

858 電源系統分析之電源綜合分析

2023-02-07 17:51:16 872

872

系統Verilog RTL模型-這些模型由設計工程師編寫,代表需要在ASIC或FPGA中實現的功能行為

2023-02-09 14:33:22 686

686

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 768

768 很多人詢問關于約束、時序分析的問題,比如:如何設置setup,hold時間?如何使用全局時鐘和第二全局時鐘(長線資源)?如何進行分組約束?如何約束某部分組合邏輯?如何通過約束保證異步時鐘域之間

2023-05-29 10:06:56 372

372

Summit T3-8系統是一個綜合分析工具,用于顯示和分析PCI-express3.1總線的數據流量規范。

2023-06-01 14:52:23 512

512

使用SDC命令create_clock創建時鐘,時鐘周期20,占空比50%的時鐘信號

2023-06-18 09:42:13 2273

2273

綜合熱分析儀是一款什么儀器呢?其實它是一種用于材料科學領域的分析儀器,其主要能夠測量材料的熱穩定性(氧化誘導期)、玻璃化轉變溫度、結晶與結晶熱、相變反應熱等物質變化,然后進行研究和分析。那么,綜合

2023-01-09 14:47:28 720

720

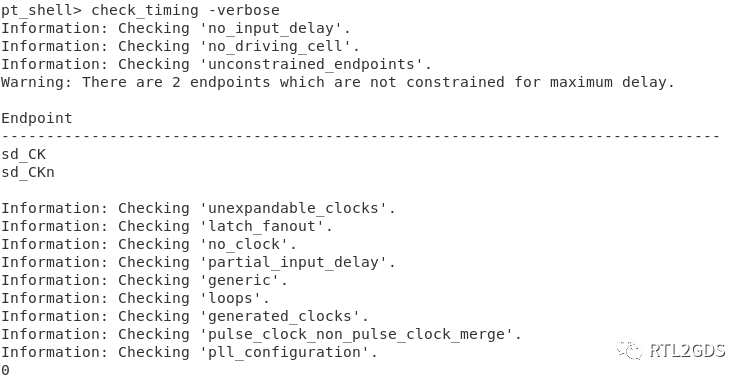

STA是由SDC驅動的,所以SDC的完整性、正確性和一致性直接決定著綜合、布局布線以及STA的有效性。

2023-06-28 17:17:50 2052

2052

Vivado綜合默認是timing driven模式,除了IO管腳等物理約束,建議添加必要的時序約束,有利于綜合邏輯的優化,同時綜合后的design里面可以評估時序。

2023-07-03 09:03:19 414

414 今天我們要介紹的時序概念是設計約束文件 **SDC** . 全稱 ***Synopsys design constraints*** . SDC是一個設計中至關重要的一個文件。

2023-07-03 14:51:21 3874

3874

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3 綜合熱分析儀是一種廣泛應用于材料科學、化學、物理等領域的儀器,能夠同時測量物質的多種熱學性質、設備綜合熱重分析儀TGA及差示掃描量熱儀DSC等。本文將介紹綜合熱分析儀的基本原理、應用場景及其優劣比較

2023-09-11 11:38:43 503

503

邏輯綜合是將RTL描述的電路轉換成門級描述的電路,將HDL語言描述的電路轉換為性能、面積和時序等因素約束下的門級電路網表。

2023-09-15 15:22:52 1919

1919

綜合熱分析儀是一種用于研究物質在不同溫度的熱力學特性的儀器。它通過測量物質的質量、溫度等參數,提供有關物質熱穩定性和化學反應的信息。本文將介紹綜合熱分析儀的工作原理。上海和晟HS-STA-002綜合

2023-11-30 14:04:57 289

289

電子發燒友網站提供《城市綜合管廊監控及安防關鍵技術分析.docx》資料免費下載

2024-01-05 11:35:07 0

0 電子發燒友網站提供《城市綜合管廊監控及安防關鍵技術分析.docx》資料免費下載

2024-01-26 10:00:38 0

0 在材料科學、化學和物理等領域中,熱分析技術扮演著關鍵的角色。綜合熱分析儀(STA),作為這一技術的重要工具,能夠揭示物質在不同溫度下的物理和化學變化。本文將深入探討綜合熱分析儀的工作原理、應用領域

2024-01-29 16:22:07 107

107

電子發燒友App

電子發燒友App

評論