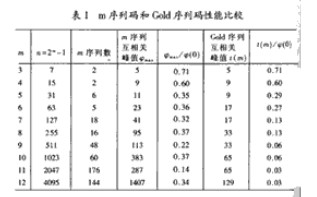

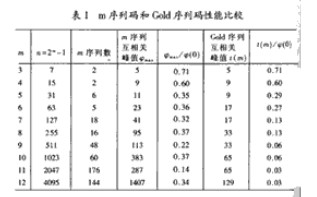

本文介紹一種基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的通信系統(tǒng)同步提取方案的實(shí)現(xiàn)。本文只介紹了M序列碼作為同步頭的實(shí)現(xiàn)方案,對(duì)于m序列碼作為同步頭的實(shí)現(xiàn),只要稍微做一下修改,即加一些相應(yīng)的延時(shí)單元就可以實(shí)現(xiàn)。

2013-04-11 10:53:23 3829

3829

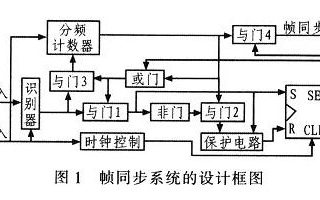

本文介紹了集中式插入法幀同步系統(tǒng)的原理,分析了幀同步系統(tǒng)的工作流程。采用模塊化的設(shè)計(jì)思想,利用VHDL設(shè)計(jì)了同步參數(shù)可靈活配置的幀同步系統(tǒng),闡述了關(guān)鍵部件的設(shè)計(jì)方法,提出了一種基于FPGA的幀同步系統(tǒng)設(shè)計(jì)方案。

2013-11-11 13:36:01 4359

4359

日前,業(yè)界首個(gè)上行載波聚合用例在羅德與施瓦茨的射頻一致性測(cè)試系統(tǒng)R&S? TS8980上認(rèn)證完成。這意味著,支持上行雙載波聚合的Cat7終端,有望將上行速率提升1倍,即將最大速率從50Mbps倍增到100Mbps。此前,羅德曾使用支持Cat6的終端,成功完成LTE Rel-10 下行雙載波聚合驗(yàn)證。

2015-07-22 13:53:18 1458

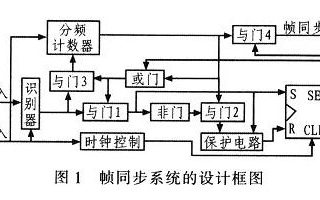

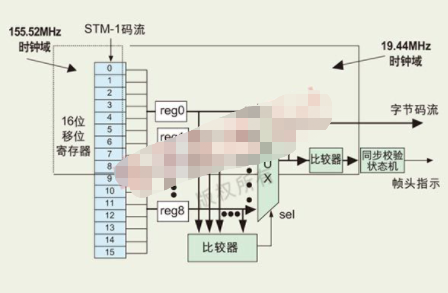

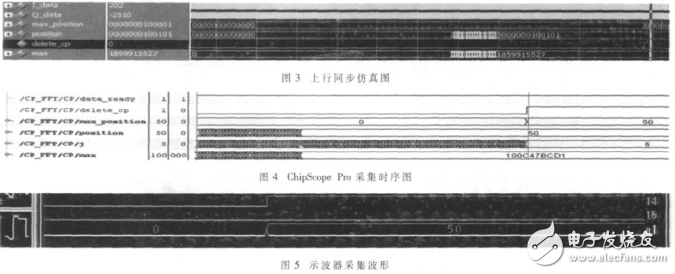

1458 實(shí)現(xiàn)幀同步的關(guān)鍵是把同步碼從一幀幀數(shù)據(jù)流中提取出來(lái)。本設(shè)計(jì)的一幀信碼由39位碼元組成。其中的巴克碼為1110010七位碼,數(shù)據(jù)碼由32位碼元組成。只有當(dāng)接收端收到一幀信號(hào)時(shí),才會(huì)輸出同步信號(hào)。幀同步系統(tǒng)的設(shè)計(jì)框圖如圖1所示。

2020-01-08 16:30:06 11839

11839

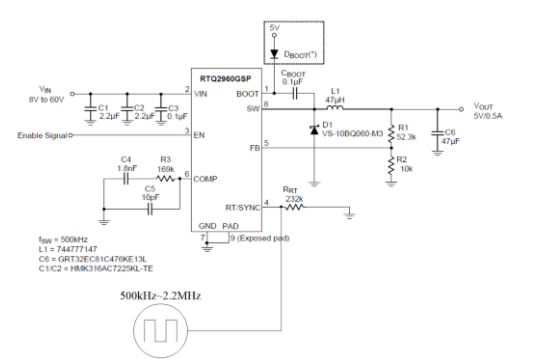

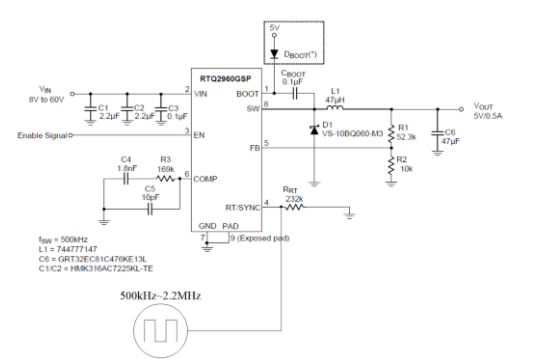

最近介紹的 60V/0.5A~5A 非同步高壓 Buck 轉(zhuǎn)換器 RT(Q)636x 系列(供工業(yè)和商業(yè)系統(tǒng)使用)和 RTQ296x-QA 系列(供車用系統(tǒng)使用)都具有時(shí)鐘信號(hào)外同步的功能,當(dāng)時(shí)

2021-02-08 10:48:00 3420

3420

FPGA設(shè)計(jì)中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開頭和末尾時(shí)刻卻無(wú)法由

2012-08-11 16:22:49

FPGA設(shè)計(jì)中幀同步系統(tǒng)的實(shí)現(xiàn)數(shù)字通信時(shí),一般以一定數(shù)目的碼元組成一個(gè)個(gè)“字”或“句”,即組成一個(gè)個(gè)“幀”進(jìn)行傳輸,因此幀同步信號(hào)的頻率很容易由位同步信號(hào)經(jīng)分頻得出,但每個(gè)幀的開頭和末尾時(shí)刻卻無(wú)法由

2012-08-11 17:44:43

在寬帶無(wú)線接入市場(chǎng)的競(jìng)爭(zhēng)力,3GPP 開展UTRA長(zhǎng)期演進(jìn)(Long Term Evolution ,LTE) 技術(shù)的研究,以實(shí)現(xiàn)3G技術(shù)向B3G和4G的平滑過(guò)渡。LTE的改進(jìn)目標(biāo)是實(shí)現(xiàn)更高的數(shù)據(jù)速率

2019-06-18 07:14:49

LTE-Advanced(簡(jiǎn)稱LTE-A)是LTE技術(shù)的進(jìn)一步演進(jìn)版本,可以實(shí)現(xiàn)更高的峰值速率和系統(tǒng)容量。需要說(shuō)明的,LTE-A不是一項(xiàng)獨(dú)立的技術(shù),而是由3GPP R10-R12版本標(biāo)準(zhǔn)中定義的載波

2019-08-15 06:56:41

3GPP從“系統(tǒng)性能要求”、“網(wǎng)絡(luò)的部署場(chǎng)景”、“網(wǎng)絡(luò)架構(gòu)”、“業(yè) 務(wù)支持能力”等方面對(duì)LTE進(jìn)行了詳細(xì)的描述。與3G相比,LTE具有如下技術(shù)特征[2][3]: (1)通信速率有了提高,下行

2011-10-27 14:16:20

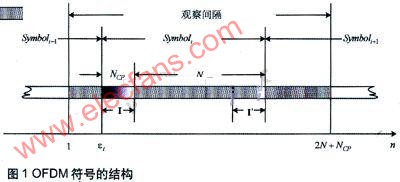

的宏分集技術(shù)在LTE中不再考慮。但是對(duì)于多小區(qū)的廣播業(yè)務(wù),需要通過(guò)無(wú)線鏈路的軟合并獲得高信噪比。在OFDM系統(tǒng)中,軟合并可以通過(guò)信號(hào)到達(dá)UE天線的時(shí)刻都處于CP窗之內(nèi)的RF合并來(lái)實(shí)現(xiàn),這種合并

2011-10-27 14:17:45

的技術(shù)可以被看作“準(zhǔn)4G”技術(shù)。3GPP LTE項(xiàng)目的主要性能目標(biāo)包括:在20MHz頻譜帶寬能夠提供下行100Mbps、上行50Mbps的峰值速率;改善小區(qū)邊緣用戶的性能;提高小區(qū)容量;降低系統(tǒng)延遲

2011-10-27 11:53:26

3GPP從“系統(tǒng)性能要求”、“網(wǎng)絡(luò)的部署場(chǎng)景”、“網(wǎng)絡(luò)架構(gòu)”、“業(yè)務(wù)支持能力”等方面對(duì)LTE進(jìn)行了詳細(xì)的描述。與3G相比,LTE具有如下技術(shù)特征:(1)通信速率有了提高,下行峰值速率為100Mbps

2019-07-01 07:39:53

基于 W-CDMA 的第三代 (3G) 無(wú)線系統(tǒng)已在全球廣泛部署。W-CDMA 技術(shù)通過(guò)在下行鏈路和上行鏈路模式中提供高速分組接入(HSPA) 技術(shù),始終保持強(qiáng)有力的競(jìng)爭(zhēng)水平。為確保 3G 系統(tǒng)在

2019-06-06 07:42:38

fpga和外圍芯片進(jìn)行通訊是不是需要把所有外圍芯片傳進(jìn)來(lái)的信號(hào)進(jìn)行同步,就是用寄存器打一拍(就是把所有wire類型的輸入變量變?yōu)閞eg),輸出也應(yīng)該用寄存器打一拍(就是說(shuō)不能以wire類型的數(shù)據(jù)輸出)。這樣做是不是能一定程度保存信號(hào)同步?

2012-10-28 22:31:25

行同步脈沖與場(chǎng)同步脈沖有什么區(qū)別

2013-10-02 17:05:56

隨著通訊業(yè)的迅猛發(fā)展,4G技術(shù)即LTE 時(shí)代呼之欲出,文章基于3GPP R8 LTE協(xié)議,從頻段、性能、關(guān)鍵 技術(shù)、具體實(shí)現(xiàn)、工程實(shí)施等方面,對(duì)FDD LTE 和TDD LTE 系統(tǒng)進(jìn)行簡(jiǎn)單的比較

2014-09-10 10:08:28

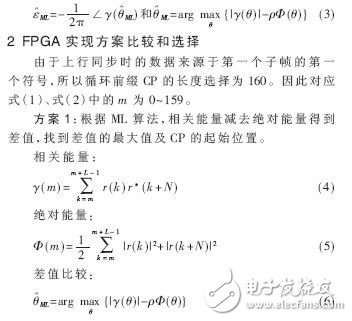

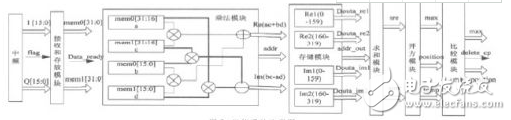

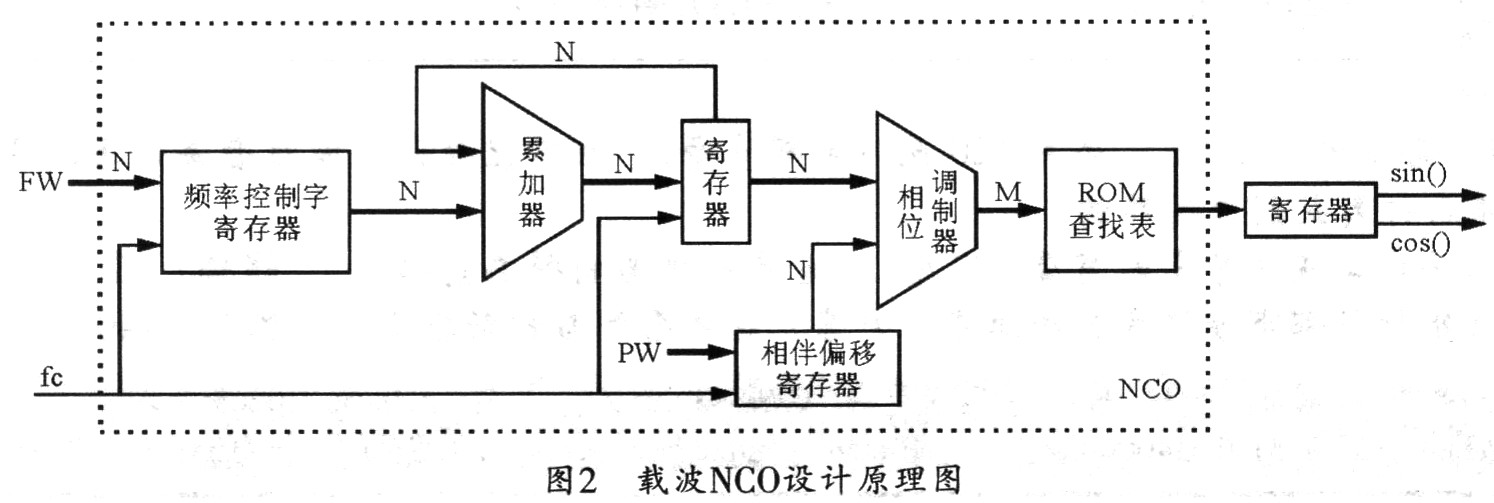

本文主要介紹各部分的算法方案及電路實(shí)現(xiàn)時(shí)所用的FPGA元件的基本結(jié)構(gòu)、設(shè)計(jì)思路。最后通過(guò)對(duì)電路的仿真波形可以看出,這些頻域同步算法和FPGA電路能夠滿足多載波傳輸系統(tǒng)的同步要求。

2021-05-07 06:52:34

我們想開發(fā)一款微型TD-LTE微型直放站,但是同步電路部分沒(méi)有任何經(jīng)驗(yàn)和技術(shù)能力,希望有成熟模塊提供的,我們可以購(gòu)買,如果有開發(fā)能力的可以合作開發(fā),請(qǐng)聯(lián)系QQ625877931

2016-03-20 20:51:38

。TD-LTE、LTE-Advanced與WiMAX系統(tǒng)雖然分屬于IMT2000不同的空中接口技術(shù),但是二者在很多方面都有共同點(diǎn)和相似之處。那么這兩類高性能系統(tǒng)能否實(shí)現(xiàn)相互融合?采用怎樣的方式進(jìn)行融合?是目前產(chǎn)業(yè)非常關(guān)注的一些問(wèn)題。

2019-08-14 07:48:50

具有中國(guó)自主知識(shí)產(chǎn)權(quán)的TD-LTE由于其頻譜利用率高(下行:5bit/S/Hz;上行:2.5bit/S/Hz);高速率(下行:100Mbps;上行:50Mbps);低延時(shí)(100ms控制面,10ms

2019-09-25 08:17:38

)、行同步(HS)、奇偶場(chǎng)(OE)、復(fù)合消隱信號(hào)(BLANK)。數(shù)字信號(hào)處理器DSP是本處理器的核心部分,其功能是完成整個(gè)系統(tǒng)的圖像預(yù)處理以及數(shù)據(jù)流存儲(chǔ)時(shí)序控制等功能。經(jīng)過(guò)DSP處理后輸出

2015-09-10 11:18:56

要求:技能:精通FPGA實(shí)現(xiàn)和LTE物理層坐標(biāo):北京報(bào)酬:詳談備注:已有MATLAB算法代碼有意者請(qǐng)將個(gè)人介紹發(fā)郵箱:hpd3887@163.com

2017-05-17 16:18:14

中國(guó)TD系統(tǒng)如何實(shí)現(xiàn)向TD-LTE發(fā)展?3.5G LTE基站的信號(hào)發(fā)射和接收架構(gòu)應(yīng)該如何實(shí)現(xiàn)?LTE對(duì)發(fā)射通道的總的性能要求是什么?

2021-06-01 06:43:11

隨著全球大多數(shù)的電信運(yùn)營(yíng)商計(jì)劃采用3GPP LTE作為下一代的無(wú)線寬帶技術(shù),LTE技術(shù)已經(jīng)逐步顯露出全球化的趨勢(shì)。激進(jìn)的LTE技術(shù)演示和部署計(jì)劃,以及對(duì)可靠測(cè)試系統(tǒng)的迫切需求,成了電信運(yùn)營(yíng)商們現(xiàn)在

2019-06-03 07:06:26

和MIMO作為其無(wú)線網(wǎng)絡(luò)演進(jìn)的唯一標(biāo)準(zhǔn)。在20MHz頻譜帶寬下,能夠提供下行326Mbit/s與上行86Mbit/s的峰值速率。改善了小區(qū)邊緣用戶的性能,提高小區(qū)榮浪和降低系統(tǒng)延遲。按用戶數(shù)量和市值

2014-11-20 14:31:47

UE 與gNodeB 之間建立和恢復(fù)上行同步。隨機(jī)接入過(guò)程分為基于競(jìng)爭(zhēng)的隨機(jī)接入和基于非競(jìng)爭(zhēng)的隨機(jī)接入:在基于競(jìng)爭(zhēng)的隨機(jī)接入過(guò)程中, 接入前導(dǎo)由 UE 隨機(jī)選定, 不同 UE選擇的前導(dǎo)可能沖突

2021-05-06 09:54:48

隨著通信技術(shù)的蓬勃發(fā)展,3GPP開展UTRA長(zhǎng)期演進(jìn)技術(shù)的研究,即LTE技術(shù),以實(shí)現(xiàn)3G技術(shù)向B3G和4G的平滑過(guò)渡。LTE的改進(jìn)目標(biāo)是實(shí)現(xiàn)更快的數(shù)據(jù)速率、更短的時(shí)延、更低的成本、更高的系統(tǒng)容量以及

2019-07-23 08:26:31

、野外試驗(yàn)以及生產(chǎn)應(yīng)用,證明結(jié)合FPGA技術(shù),時(shí)鐘恢復(fù)和系統(tǒng)同步技術(shù)在地震勘探儀器中具有獨(dú)到的優(yōu)勢(shì),其精度可達(dá)us級(jí),而且穩(wěn)定,實(shí)現(xiàn)方便。地震勘探儀器是一個(gè)高度集成的網(wǎng)絡(luò)采集系統(tǒng),在這些地震勘探儀器中

2019-06-18 08:15:35

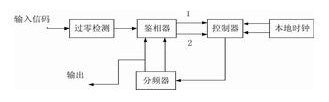

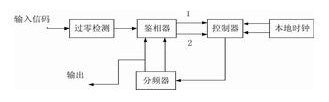

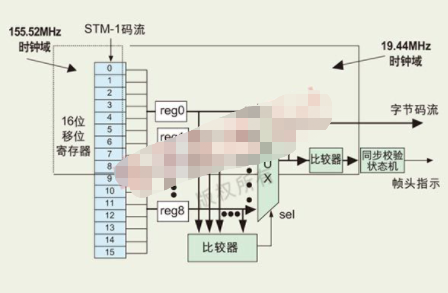

在可靠的通信系統(tǒng)中,要保證接收端能正確解調(diào)出信息,必須要有一個(gè)同步系統(tǒng),以實(shí)現(xiàn)發(fā)送端和接收端的同步,因此同步提取在通信系統(tǒng)中是至關(guān)重要的。一個(gè)簡(jiǎn)單的接收系統(tǒng)框圖如圖1所示。

2019-09-17 06:28:08

在可靠的通信系統(tǒng)中,要保證接收端能正確解調(diào)出信息,必須要有一個(gè)同步系統(tǒng),以實(shí)現(xiàn)發(fā)送端和接收端的同步,因此同步提取在通信系統(tǒng)中是至關(guān)重要的。

2019-09-19 07:28:51

要求:該系統(tǒng)將圖像采集、顯示和存儲(chǔ)功能集成到FPGA平臺(tái)上,本設(shè)計(jì)采用NIOS II 設(shè)計(jì)軟核系統(tǒng),通過(guò)FPGA初始化圖像傳感器OV7670,OV7670再等待場(chǎng)同步,行同步,將采集的數(shù)據(jù)在TFT

2012-05-22 09:22:09

我想做多個(gè)FPGA的時(shí)鐘同步,目前的想法是用一個(gè)FPGA的內(nèi)部時(shí)鐘,復(fù)制到外接IO口,接到另一個(gè)FPGA的外部時(shí)鐘引腳,波形有較小的相移但是可以保證同步。想問(wèn)一下可以復(fù)制多次,驅(qū)動(dòng)多個(gè)FPGA的同步嗎。對(duì)驅(qū)動(dòng)能力有什么要求?其中每一個(gè)FPGA都用的是一個(gè)EP4CE的最小系統(tǒng)板。

2019-01-21 15:07:41

我有一個(gè)Signal Studio N7624B(LTE FDD),并使用4438C Sig Gen來(lái)測(cè)量FDD LTE上行鏈路和下行鏈路信號(hào)。在測(cè)試LTE時(shí),一致性文檔指出正確測(cè)試需要UL參考信道

2019-07-18 09:44:34

應(yīng)用于LTE-OFDM系統(tǒng)的Viterbi譯碼在FPGA中的實(shí)現(xiàn)在OFDM系統(tǒng)中,為了獲得正確無(wú)誤的數(shù)據(jù)傳輸,要采用差錯(cuò)控制編碼技術(shù)。LTE中采用Viterbi和Turbo加速器來(lái)實(shí)現(xiàn)前向糾錯(cuò)。提出

2009-09-19 09:41:24

應(yīng)用于LTE_OFDM系統(tǒng)的Viterbi譯碼在FPGA中的實(shí)現(xiàn)在 系 統(tǒng) 中 為 了 獲 得 正 確 無(wú) 誤 的 數(shù) 據(jù) 傳 輸 要 采 用 差 錯(cuò) 控 制 編 碼 技 術(shù) 中 采 用和 加 速

2012-08-11 15:27:24

嗨,我正在使用Agilent Signal Studio進(jìn)行LTE-LTE-Advanced FDD,以生成用于標(biāo)準(zhǔn)基站LTE測(cè)試的波形文件。目標(biāo)儀器是E4433B。我必須為3GPP測(cè)試模型中定義

2019-01-23 15:11:42

LTE所選擇的上行傳輸方案是一個(gè)新變量:SC-FDMA(單載波-頻分多址)相比于傳統(tǒng)OFDMA其優(yōu)點(diǎn)是既有單載波的低峰均功率比(PAPR),又有多載波的可靠性。在上行鏈路這點(diǎn)特別重要,較低的PAPR可在傳輸功效方面極大提高移動(dòng)終端的性能,因此可延長(zhǎng)電池使用壽命。

2019-08-20 07:22:04

怎樣對(duì)AD7606的8個(gè)采樣通道進(jìn)行同步采樣呢?并對(duì)采樣后的數(shù)據(jù)進(jìn)行卡爾曼濾波處理?

2021-10-19 06:12:57

上行4G,與主站通訊;支持上行以太網(wǎng),與主站通訊;支持上行LORA,與集中器通訊;支持下行MODBUS,水表通訊;支持RS485,與電表通訊。廣和通Cat 1模組賦能智慧網(wǎng)關(guān)無(wú)線聯(lián)網(wǎng)廣和通LTE Cat

2020-10-12 10:49:24

如題,小菜鳥,正在準(zhǔn)備LTE上行信道估計(jì)的論文,搜到了SC-FDMA的生成程序,但是自己水平不行,對(duì)LTE上行信道估計(jì)程序還是很頭大,希望高手分享個(gè)這方面的參考程序,謝謝!

2013-01-16 11:27:00

本帖最后由 eehome 于 2013-1-5 10:05 編輯

測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

2012-08-06 12:37:13

測(cè)控系統(tǒng)中B碼同步技術(shù)的FPGA實(shí)現(xiàn)

2012-08-06 11:48:16

幀同步系統(tǒng)的工作原理是什么?幀同步系統(tǒng)的FPGA設(shè)計(jì)與實(shí)現(xiàn)

2021-04-28 07:20:21

親愛(ài)的各位,我需要讀一個(gè)長(zhǎng)的串行同步數(shù)字?jǐn)?shù)據(jù),例如連續(xù)600位。這系列的0和1s是在時(shí)鐘的下降沿發(fā)送的。我認(rèn)為我不能使用SPI,因?yàn)榇袛?shù)據(jù)時(shí)鐘必須是連續(xù)的。我能在這里收集一些ID嗎?DCI是做這項(xiàng)工作的好選擇嗎?同步時(shí)鐘速度約為5兆赫,而UC I使用的是DSSPICE E512M810。

2020-04-21 11:06:39

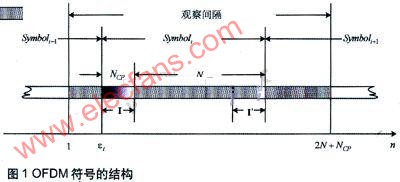

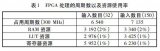

基于FPGA 的OFDM 寬帶數(shù)據(jù)通信同步系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn):正交頻分復(fù)用(OFDM)是第四代移動(dòng)通信的核心技術(shù),本文介紹了一種基于FPGA的OFDM 寬帶數(shù)據(jù)通信同步系統(tǒng)的設(shè)計(jì)方案,該方案為OFDM

2009-06-25 08:18:06 44

44 在介紹了GPS 同步時(shí)鐘基本原理和FPGA 特點(diǎn)的基礎(chǔ)上,提出了一種基于FPGA 的GPS同步時(shí)鐘裝置的設(shè)計(jì)方案,實(shí)現(xiàn)了高精度同步時(shí)間信號(hào)和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

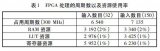

40 從時(shí)分復(fù)接系統(tǒng)對(duì)位同步系統(tǒng)的性能要求出發(fā),提出了一種基于FPGA的快速位同步系統(tǒng)的設(shè)計(jì)方案,給出了位同步系統(tǒng)的實(shí)驗(yàn)仿真,結(jié)果表明該系統(tǒng)有較快的位同步建立時(shí)間,節(jié)省了F

2010-07-28 18:13:40 20

20 從時(shí)分復(fù)接系統(tǒng)對(duì)幀同步系統(tǒng)的性能要求出發(fā),提出了一種采用FPGA實(shí)現(xiàn)幀同步系統(tǒng)的設(shè)計(jì)方案,重點(diǎn)介紹了同步保護(hù)電路的設(shè)計(jì),并給出了FPGA設(shè)計(jì)的實(shí)驗(yàn)仿真,實(shí)驗(yàn)結(jié)果表明該電路

2010-08-06 16:46:59 24

24 TD-SCDMA上行同步碼接收

1 引言

2 TD-SCDMA 系統(tǒng)幀結(jié)構(gòu)

3 TD-SCDMA上行同步過(guò)程

..............

2010-09-15 17:11:31 21

21 為實(shí)現(xiàn)設(shè)備中存在的低速數(shù)據(jù)光纖通信的同步復(fù)接/ 分接,提出一種基于FPGA 的幀同步頭信號(hào)提取檢測(cè)方案,其中幀頭由7 位巴克碼1110010 組成,在數(shù)據(jù)的接收端首先從復(fù)接數(shù)據(jù)中

2010-10-26 16:56:54 46

46 串行同步通信的應(yīng)用

該文給出利用8251A實(shí)現(xiàn)串行同步通訊設(shè)計(jì)的方法

關(guān)鍵詞:

2009-10-17 11:24:07 1987

1987

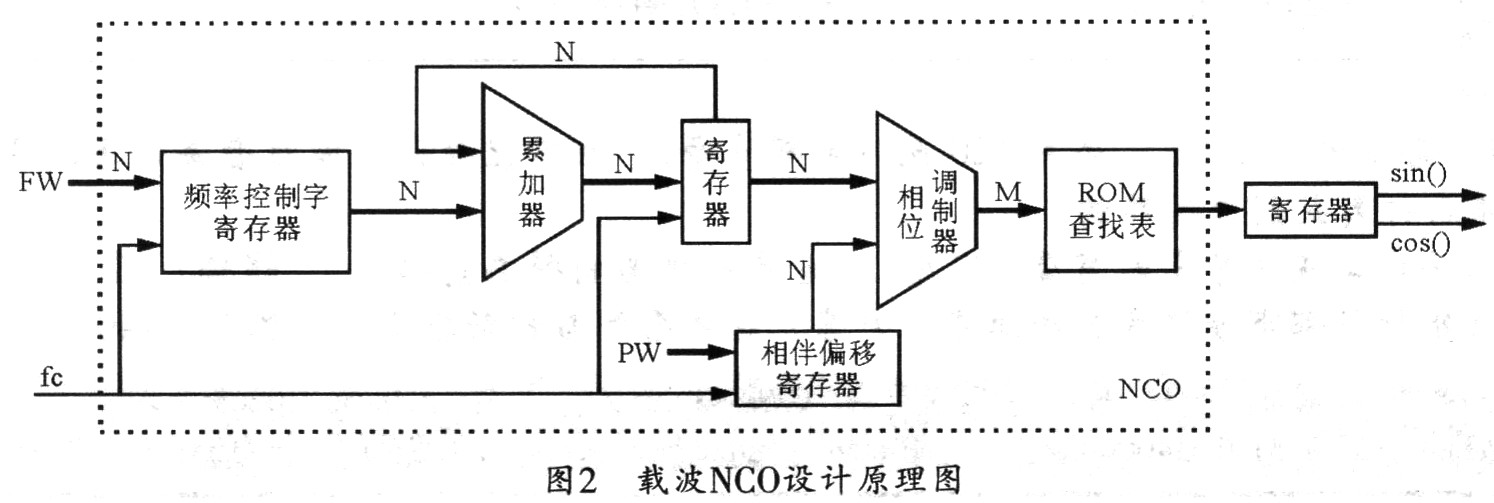

直擴(kuò)OQPSK系統(tǒng)載波跟蹤的 設(shè)計(jì)及FPGA實(shí)現(xiàn)

0 引言??? 載波同步是無(wú)線通信系統(tǒng)中一個(gè)重要的實(shí)際問(wèn)題,是基帶信號(hào)處理的關(guān)鍵技術(shù)。導(dǎo)致載波頻率及相位不

2009-12-12 11:32:02 1407

1407

基于802.16d的定時(shí)同步算法改進(jìn)及FPGA實(shí)現(xiàn)

0 引言

WiMAX ( Wordwide Interoperability for Mi-crowave Access)是代表空中接口滿足IEEE 802.16標(biāo)準(zhǔn)的寬帶無(wú)線通信系統(tǒng)。其

2010-02-22 09:38:31 844

844

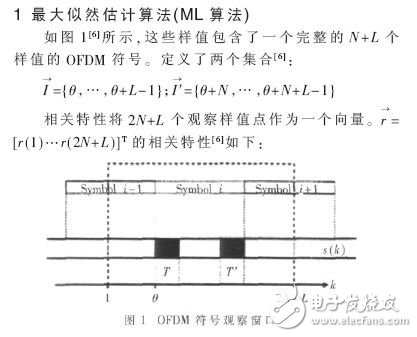

基于循環(huán)前綴的同步算法及FPGA實(shí)現(xiàn)

正交頻分復(fù)用(OrthogonalFrequency Division Multiplexing,OFDM)技術(shù)已經(jīng)成為第四代移動(dòng)通信研究的熱點(diǎn),同時(shí),OFDM同步又是OFDM的關(guān)鍵技

2010-03-23 09:27:48 1530

1530

本文采用VHDL描述語(yǔ)言,充分利用Xilinx公司Spartan II FPGA的系統(tǒng)資源,設(shè)計(jì)實(shí)現(xiàn)了一種非對(duì)稱同步FIFO,它不僅提供數(shù)據(jù)緩沖,而且能進(jìn)行數(shù)據(jù)總線寬度的轉(zhuǎn)換。

2011-01-13 11:33:43 1744

1744 在比較已有FFT實(shí)現(xiàn)方法的基礎(chǔ)上,提出一種基于FPGA的通用FFT處理器的設(shè)計(jì)方案。這種FFT實(shí)現(xiàn)結(jié)構(gòu)根據(jù)不同的輸入數(shù)據(jù)長(zhǎng)度動(dòng)態(tài)配置成相應(yīng)的處理器,可以支持多種基數(shù)為2、3、5的FFT計(jì)算,硬件資源得到了優(yōu)化,處理速度及數(shù)據(jù)精度滿足LTE系統(tǒng)中SC-FDMA基帶信號(hào)的

2011-01-16 12:51:03 922

922

摘要:同步接口是光纖縱差保護(hù)裝置的重要組成部分,本文介紹了Cyclone II FPGA 在光纖縱差保護(hù)同步接口中的應(yīng) 用,詳細(xì)地闡述了FPGA 實(shí)現(xiàn)光纖縱差保護(hù)同步通信接口的原理。大規(guī)模可編

2011-04-06 16:42:11 40

40 本文闡述了主同步搜索的改進(jìn)型算法,并且針對(duì)這種算法提出了基于片上RAM 的實(shí)現(xiàn)方式,最大程度地節(jié)省了FPGA 的硬件資源,為WCDMA 同步的FPGA 實(shí)現(xiàn)提供了很好的解決方案。這種技術(shù)可

2011-05-14 16:45:53 30

30 長(zhǎng)期演進(jìn)(LTE)無(wú)線網(wǎng)絡(luò)給測(cè)試設(shè)備供應(yīng)商提出了若干挑戰(zhàn)。3GPP定義的LTE空中接口,在下行采用正交頻分多址(OFDMA)技術(shù),在上行采用單載頻頻分多址(SC-FDMA)技術(shù),且上下行同時(shí)采用了多輸

2011-12-27 10:27:03 529

529 長(zhǎng)期演進(jìn)(LTE)無(wú)線網(wǎng)絡(luò)給測(cè)試設(shè)備供應(yīng)商提出了若干挑戰(zhàn)。3GPP定義的LTE空中接口,在下行采用正交頻分多址(OFDMA)技術(shù),在上行采用單載頻頻分多址(SC-FDMA)技術(shù),且上下行同時(shí)采用了多輸

2012-02-03 14:32:28 454

454

導(dǎo)頻疊加OFDM同步方法的FPGA實(shí)現(xiàn),目前正交頻分復(fù)用(OFDM)技術(shù)已經(jīng)成為第四代移動(dòng)通信研究的熱點(diǎn),同時(shí)OFDM同步又是OFDM的關(guān)鍵技術(shù)

2012-02-20 15:15:39 1765

1765

同步技術(shù)是跳頻系統(tǒng)的核心。本文針對(duì)FPGA的跳頻系統(tǒng),設(shè)計(jì)了一種基于獨(dú)立信道法,同步字頭法和精準(zhǔn)時(shí)鐘相結(jié)合的快速同步方法,同時(shí)設(shè)計(jì)了基于雙圖案的改進(jìn)型獨(dú)立信道法,同步算

2013-05-06 14:09:20 22

22 基于FPGA的光電系統(tǒng)同步自適應(yīng)電路設(shè)計(jì)與實(shí)現(xiàn)

2016-01-04 17:03:55 10

10 LTE上行干擾協(xié)調(diào)技術(shù)的研究,很好的網(wǎng)絡(luò)資料,快來(lái)學(xué)習(xí)吧。

2016-04-19 11:30:48 18

18 應(yīng)用于LTE_OFDM系統(tǒng)的Viterbi譯碼在FPGA中的實(shí)現(xiàn)

2016-05-11 11:30:19 11

11 為了能在GPS接收端獲取正確導(dǎo)航電文,研究了CJPS接收機(jī)位同步、幀同步的基本原理和實(shí)現(xiàn)方式。提出一種采用FPGA來(lái)實(shí)現(xiàn)位同步、幀同步系統(tǒng)的設(shè)計(jì)方案。使用Xilinx開發(fā)軟件,通過(guò)Verilog代碼

2017-11-07 17:13:39 10

10 (fieldprogrammablegatearray,FPGA)間的大容量數(shù)據(jù)交互,設(shè)計(jì)了一種高速的嵌入式技術(shù)串行高速輸入輸出口(serialrapidIO, SRIO),實(shí)現(xiàn)2塊FPGA芯片間的互連,保證在TD-LTE系統(tǒng)中上行和下行數(shù)據(jù)處理的獨(dú)立性和交互的便捷。

2017-11-17 10:22:44 3941

3941 介紹了精密時(shí)鐘同步協(xié)議(PTP)的原理。本文精簡(jiǎn)了該協(xié)議,設(shè)計(jì)并實(shí)現(xiàn)了一種低成本、高精度的時(shí)鐘同步系統(tǒng)方案。該方案中,本地時(shí)鐘單元、時(shí)鐘協(xié)議模塊、發(fā)送緩沖、接收緩沖以及系統(tǒng)打時(shí)標(biāo)等功能都在FPGA

2017-11-17 15:57:18 6196

6196

主要基于FPGA 實(shí)現(xiàn)TDR-LTE 系統(tǒng)中的ReedR-Muller 譯碼,包括Reed-Muller 譯碼的介紹、方案的構(gòu)成、FPGA 實(shí)現(xiàn)流程、以及實(shí)現(xiàn)結(jié)果分析。并在VirtexR-6 芯片

2017-11-18 06:20:08 2085

2085

LTE系統(tǒng)將最大系統(tǒng)帶寬從5 MHz擴(kuò)展到20 MHz,能夠在20 MHz帶寬內(nèi)實(shí)現(xiàn)50 Mb/s上行瞬間峰值速率和100 Mb/s下行瞬間峰值速率 。

2018-07-18 09:30:00 2528

2528

樣機(jī),它在單SHANNON300 基帶芯片上支持兩路傳輸,使SHANNON300成為世界上第一顆成功驗(yàn)證LTE-Advanced上行載波聚合的芯片。支持雙天線傳輸?shù)纳逃媒K端目前仍然是一個(gè)挑戰(zhàn)。在未來(lái),上行載波聚合和上行MIMO將用來(lái)滿足無(wú)線網(wǎng)絡(luò)上行吞吐量的需求,如多媒體上傳到云服務(wù)等。 在羅德與

2017-12-06 07:26:01 315

315 一般的位同步電路大多采用標(biāo)準(zhǔn)邏輯器件按傳統(tǒng)數(shù)字系統(tǒng)設(shè)計(jì)方法構(gòu)成,具有功耗大,可靠性低的缺點(diǎn)。用FPGA設(shè)計(jì)電路具有很高的靈活性和可靠性,可以提高集成度和設(shè)計(jì)速度,增強(qiáng)系統(tǒng)的整體性能。本文給出了一種基于fpga的數(shù)字鎖相環(huán)位同步提取電路。

2019-04-19 08:24:00 3113

3113

為了實(shí)現(xiàn)基于嵌入式系統(tǒng)的兩路視頻的同步播放控制,本文提出了根據(jù)圖像內(nèi)容檢測(cè)達(dá)到兩路視頻同步播放控制的設(shè)計(jì)思想。根據(jù)該思想設(shè)計(jì)了基于FPGA 的實(shí)驗(yàn)電路,構(gòu)建了完整的系統(tǒng)實(shí)驗(yàn)硬件平臺(tái)。該系統(tǒng)平臺(tái)的建立,證明了基于嵌入式電路的以圖像內(nèi)容檢測(cè)為手段的兩路圖像同步播放控制的可行性。

2018-11-06 19:35:28 7

7 LTE-A 網(wǎng)絡(luò)大規(guī)模的引入和建設(shè),系統(tǒng)容量和數(shù)據(jù)傳輸速率的大幅度增加也給LTE-A 系統(tǒng)測(cè)試設(shè)備和軟件帶來(lái)更大的挑戰(zhàn)。接收端能否準(zhǔn)確恢復(fù)和解析信號(hào)將決定整個(gè)系統(tǒng)的性能,物理下行鏈路的處理和實(shí)現(xiàn)是整個(gè)

2018-11-09 17:15:42 4

4 采用現(xiàn)場(chǎng)可編程門陣列FPGA實(shí)現(xiàn)軟件無(wú)線電技術(shù),控制和調(diào)整擴(kuò)頻通信系統(tǒng)的同步性能。該系統(tǒng)介紹了用FPGA實(shí)現(xiàn)對(duì)采樣信號(hào)正交數(shù)字下變頻,完成同步搜索和頻偏估計(jì),以及糾正載波頻偏和調(diào)整碼元速率,同步跟蹤

2020-07-27 16:53:15 14

14 針對(duì)傳統(tǒng)的小區(qū)內(nèi)開環(huán)功率控制算法通常以提升本小區(qū)的吞吐量性能為目標(biāo),忽略了當(dāng)前小區(qū)用戶對(duì)鄰小區(qū)用戶同頻干擾的問(wèn)題,為提升邊緣用戶性能的同時(shí)兼顧系統(tǒng)整體性能,提出了一種LTE系統(tǒng)小區(qū)間上行聯(lián)合功率控制

2020-10-09 17:38:59 10

10 如何利用FPGA實(shí)現(xiàn)FFT算法,包括算法選取、算法驗(yàn)證、系統(tǒng)結(jié)構(gòu)設(shè)計(jì)、FPGA實(shí)現(xiàn)和測(cè)試整個(gè)流程。設(shè)計(jì)采用Good-Thomas算法,利用Verilog HDL描述的方式實(shí)現(xiàn)了不定點(diǎn)FFT系統(tǒng),并以FPGA芯片virtex4為硬件平臺(tái),進(jìn)行了仿真、綜合、板級(jí)驗(yàn)證等工作。仿真結(jié)果表明

2021-01-25 14:27:15 8

8 LabVIEW 1000米以下的海浪:通過(guò)聲音對(duì)自治單元進(jìn)行同步采樣

2021-04-23 17:36:46 3

3 速率匹配是LTE系統(tǒng)中重要的組成部分。在詳細(xì)分析3GPP協(xié)議中Turbo編碼速率匹配算法的基礎(chǔ)上,給出了一種基于FPGA的速

2021-04-28 09:42:08 2726

2726

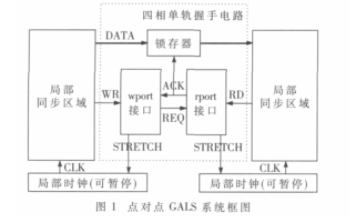

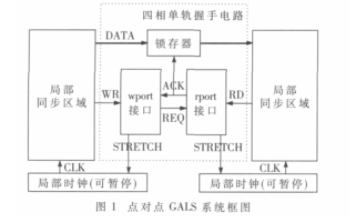

在常規(guī)FPGA中設(shè)計(jì)了基于LUT的異步狀態(tài)保持單元,實(shí)現(xiàn)了全局異步局部同步系統(tǒng)的接口電路、時(shí)鐘暫停電路,進(jìn)一步完

2021-05-26 18:12:38 3436

3436

,首先要從同步數(shù)據(jù)流中提取幀同步信息,幀同步提取性能的優(yōu)劣直接影響整個(gè)數(shù)據(jù)的處理質(zhì)量與整個(gè)系統(tǒng)的性能。使用FPGA技術(shù)可以實(shí)現(xiàn)同步系統(tǒng)的模塊化、小型化和芯片化,得到穩(wěn)定可靠的幀同步器。

2021-06-23 15:44:00 2451

2451

LTE-A系統(tǒng)的主同步信號(hào)重疊分段檢測(cè)算法

2021-06-24 15:38:51 5

5 AN4666_運(yùn)用GPIO和DMA實(shí)現(xiàn)并行同步通信

2022-11-21 17:07:13 0

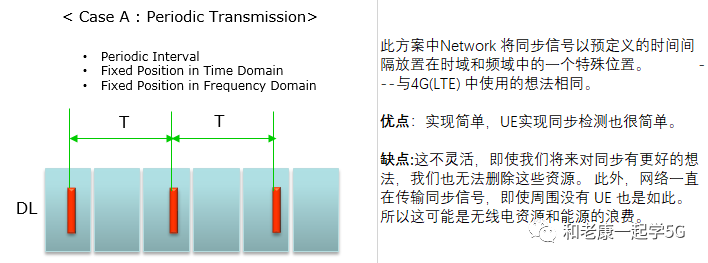

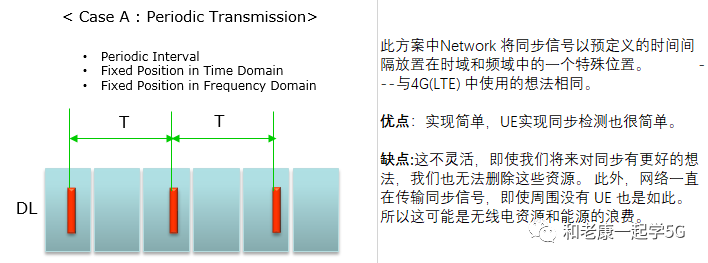

0 在**5G(NR)網(wǎng)絡(luò)中上行和下行同步**中我們可獲悉“ **同步”** 是網(wǎng)絡(luò)(NETWORK)和終端雙方需預(yù)先定義(參考)信號(hào)

2023-06-20 15:14:30 922

922

對(duì)于多位的異步信號(hào)如何進(jìn)行同步呢? 異步信號(hào)(Asynchronous Signals)是指系統(tǒng)中發(fā)生的事件或者信號(hào),它們的發(fā)生時(shí)間不可預(yù)測(cè)、不可控制,與其他的進(jìn)程、線程以及系統(tǒng)中的各種資源之間

2023-09-12 11:18:09 976

976 在Linux系統(tǒng)中提供了多種同步機(jī)制,本文主要講講如何使用pthread_barrier_xxx系列函數(shù)來(lái)實(shí)現(xiàn)多線程之間進(jìn)行同步的方法。

2023-10-23 14:43:06 237

237

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論