摘 要:實現了基于FPGA 的雙線性CFA 插值算法。該算法的處理對象是每個像素為8 bit的XGA @15 Hz 的Bayer 模板數據,目的是能得到每個像素是24 bit 的XGA @15 Hz 的彩色圖像數據。輸入的數據先進入緩存模塊,緩存模塊是由FPGA 內部的雙口的RAM 構成,從緩存中輸出的數據被分成奇行組和偶行組,然后奇行組的數據經選擇器進入奇行奇列運算塊和奇行偶列運算塊,偶行組的數據經選擇器進入偶行奇列運算塊和偶行偶列運算塊,最后在插值控制模塊的作用下,各運算塊處理的數據經輸出選擇器輸出。

像數碼相機這樣的數字圖像設備,考慮到成本和包裝, 輸出的一般是貝爾(Bayer ) 模板[1 ] CFA(Color Filter Array) 圖像,需要通過CFA 插值算法來獲得全彩圖像。

在實現算法時,通常需要專用的DSP (digital signal processing) ,后然采用C 語言或者其他語言編程進行實現;隨著半導體技術的發展, FPGA (field pro-gramming gate array) 作為可編程芯片,其集成度也已達上千萬門, FPGA 的可編程特性使其在SOC( system on a chip) 中發揮著越來越重要的作用,這樣就產生了用FPGA 直接實現算法,而不需要再用價格昂貴的DSP ,筆者就嘗試基于FPGA 實現CFA插值算法。

1 雙線性插值算法

雙線性插值算法[2 ,3 ] 是非自適應算法的一種,輸出的圖像使用鄰近像素中相同顏色成份做線性平均計算來補償每個像素丟失的顏色。如圖1 中,像素(2 , 3) 僅有藍色成份。因此丟失的綠色部份可通過求其上、下、左、右像素的綠色成份的平均值得到。同樣,丟失的紅色可通過對相鄰四個對角上的像素的紅色成份求平均值。這種算法可以被視頻所接受,因為人類的眼睛不容易在動態的兩幀視頻中查覺到模糊。

2 雙線性插值的模塊化設計

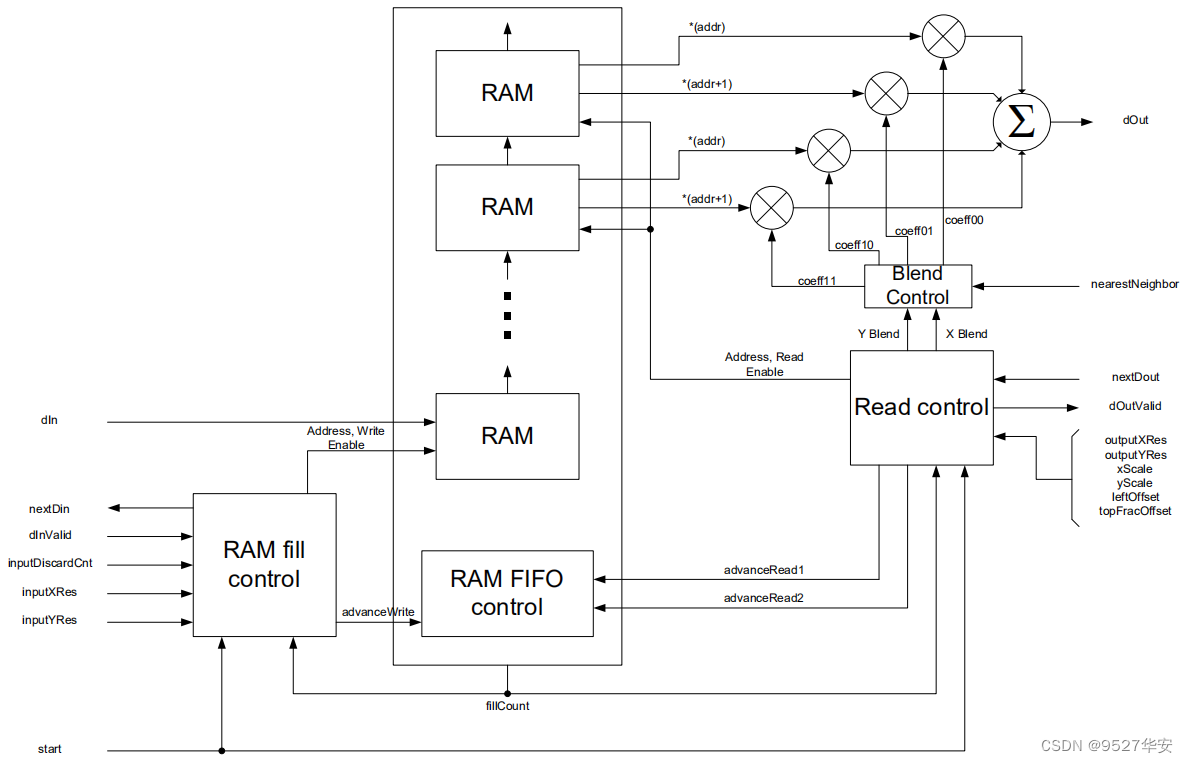

整個設計采取自頂向下的模塊化設計[4 ] 方法,代碼采用VHDL 語言進行編寫,頂層模塊定義為CFA 插值模塊,定義輸入輸出接口信號、復位、時鐘信號,并且描述了內部各子模塊的邏輯連接關系。頂層的下層是由3 個模塊構成,框圖如圖2 所示,設計內容如下:

1) 緩存控制模塊。設計了兩個控制器,其中一個是寫控制器,另一個是讀控制器。寫控制器主要由一個12 位的計數器構成,用高兩位對4 個存儲體進行選擇,低10 位用來產生相應的地址,配合輸入的寫信號對緩存的進行寫操作。讀控制器主要由一個10 位的計數器構成,產生對4 個存儲體進行讀操作的地址。

在此模塊的設計中,考慮到實時處理的因素,在每一幀圖像進來時先寫滿兩個存儲體,每個存儲體的長度剛好等于每行有效像素的個數,也既是存儲了兩行有效像素,在寫到第3 行的第3 個有效像素時,進行存儲體的讀操作。

緩存存放數據的順序是這樣的,最初的一幀圖像的第1 行有效數據存放在1 號存儲體,依次存放下去,第5 行數據再存放到1 號存儲體,這樣循環下去即可,存完一幀后,寫控制器復位,下一幀來時按上述操作進行,如此往復。

緩存控制器對緩存的寫操作是同一時刻只對一個存儲體進行操作,而讀操作是對4 個存儲體同時進行。

2) 緩存模塊。該模塊由4 個相同的1024 ×8 bit的存儲體構成,每個存儲體由FPGA 內部的2 個BLOCKRAM構成,每個存儲體都是雙口的SRAM ,把其中一個端口定義為只寫,另一個端口定義為只讀。每個存儲體的每個端口靠緩存控制模塊發來的讀寫使能信號來進行相應操作。對這4 個存儲體進行編號,依次為1、2、3、4 號存儲體,其中的1、3 號存儲體在這里稱為奇行,2、4 號存儲體在這里稱為偶行。

3) 插值模塊。此模塊由2 個子模塊構成,插值控制模塊和插值運算模塊。

插值控制模塊先對存儲體輸入的數據線進行組合,并對組合后的數據線編號,如圖3 所示,圖3 中方框內的數字分別代表各個存儲體輸出的數據線,經過這樣組合后,就得到24 位寬的數據線,并且數據線的高低位也是如圖示的順序,以1 組為例,存儲體4 的數據線的最高位是組合后的最高位,存儲體2 的數據線的最低位是組合后的最低位。在這里,把1 、3 組稱為奇行組,2 、4 組稱為偶行組。

插值控制模塊內部有一個12 位的計數器,最高位控制進入插值模塊的數據是1 、2 組還是3 、4 組,奇偶行組的數據分別進入各自的3 級寄存器組,如圖4 所示。

?

電子發燒友App

電子發燒友App

評論