在需要多個FPGA芯片的應用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過“成組”加載方式同時加載;

2023-02-20 10:18:27 3783

3783

通過FPGA的多重配置可以有效地精簡控制結構的設計,同時可以用邏輯資源較少的FPGA器件實現需要很大資源才能實現的程序。以Virtex5系列開發板和配置存儲器SPI FLASH為基礎,從硬件電路

2014-01-24 14:17:22 13670

13670

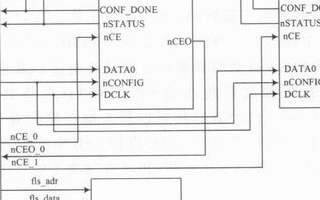

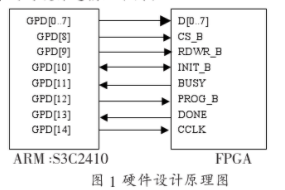

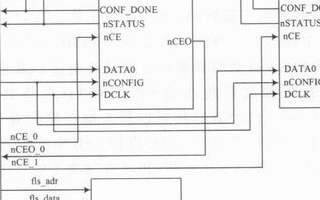

現場可編程門陣列(FPGA)作為專用集成電路(ASIC)領域的一種半定制電路,可以根據設計的需要靈活實現各種接口或者總線的輸出,在設備端的通信產品中已得到越來越廣泛的使用。##在設備端通信產品中,基于CPLD 的FPGA 從并加載框如圖2 所示。

2015-01-30 16:54:39 2847

2847 當FPGA 完成上電自動加載初始化的比特流后,可以通過觸發FPGA 內部的多重啟動事件使得FPGA 從外部配置存儲器(SPI FLASH)指定的地址自動下載一個新的比特流來重新配置。

2015-02-02 11:09:51 1096

1096

大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2019-07-01 17:16:45 16228

16228 目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-10-24 14:52:00 612

612 目前,大多數 FPGA 芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 1780

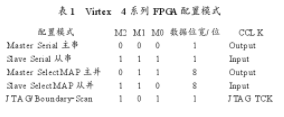

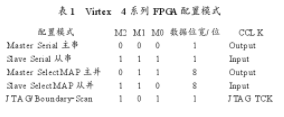

1780 使用的FLASH](4)從并方式。即文章中探討的FPGA 加載方案。2]以Xilinx 公司Spartan - 6 系列FPGA 為例,與從并加載相關的管腳如表1 所示。表1 從并加載管腳名稱由表1

2019-07-12 07:00:09

是基于靜態隨機存儲器(SRAM) 結構的,斷電后程序丟失后的每次上電都需要重新加載程序。且隨著FPGA 規模的升級,加載程序的容量也越來越大,如Xilinx 公司的Spartan - 6 系列中的6SLX150T,其

2019-06-14 06:00:00

使用Platform USB cable II通過JTAG加載程序。接口如下所示(我們還通過USB連接器為電路板供電)我們使用影響軟件來刷新FPGA。JTAG初始化是正確的,如下圖所示,但FPGA未檢測到加載.bit文件。可能導致上述問題的原因是什么?問候HPC

2019-09-26 10:07:29

高電平狀態。接我們單板的GPIO后,我們的FPGA無法正常加載,GPIO管腳從FPGA直連至板間連接器,斷開連接器恢復正常。經過測試發現由于GPIO鏈接對端的高電平,導致我們的GPIO對應BANK

2020-06-12 13:54:15

前言操作環境:Windows 7 64bitISE 14.7 FPGA程序加載與固化將開發板通過Xilinx FPGA JTAG下載器連接到PC機,打開Windows的設備管理器查看下載器是否已正常

2020-09-25 09:57:45

1. 如何實現FPGA局部動態加載。2. pcie部分不變,實現部分程序加載。3. 目前是通過JTAG線,通過PCIE加載的FPGA程序。4. 現在是想通過更改bin文件,不通過JTAG的方式加載。

2021-03-08 09:32:33

請問FPGA邏輯加載方式有哪些?例如flash等

2024-01-26 10:05:13

。使用BITSTREAM.CONFIG.EXTMASTERCCLK_EN屬性在Vivado中設置ExMasterCclk_en選項 三、FPGA加載時序 上電時序圖 上電時序圖 上電配置流程 其配置過程分解為8個步驟。 1、上電 7

2021-01-15 16:43:43

多重通訊的挑戰是什么?

2021-05-13 06:09:40

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行

2019-07-18 08:10:11

本帖最后由 qwerasdzkk 于 2012-3-10 16:00 編輯

[hide]詳解電容在實際電路中應用[/hide]

2012-03-08 09:47:24

學的知識怎樣才能運用到實際中啊

2015-03-13 18:32:49

`1、引言在系統上電時,需要從外部載入所要運行的程序,此過程被稱為程序加載。多數情況下,從外部專用的 讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當系統需要容量大而且 FPGA要加載

2019-12-10 17:42:18

立題簡介:內容:MCU+CPLD/FPGA實現GPIO擴展與控制;來源:實際得出;作用:MCU+CPLD/FPGA實現GPIO擴展與控制;仿真環境:Quartus II 11.0;日期

2021-11-04 07:42:16

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊主要介紹從動串行(SS)加載模式以及從動串行級聯加載模式的使用。內容包括使用從動串行加載模式的軟件配置,使用從動串行加載模式和從動串行級聯加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動串行加載的主控器件時的軟件工作流程。

2022-10-27 08:03:06

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊主要介紹從動并行(SP)加載模式以及從動并行級聯加載模式的使用。內容包括使用從動并行加載模式的軟件配置,使用從動并行加載模式和從動并行級聯加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動并行加載的主控器件時的軟件工作流程。

2022-10-27 07:31:16

Verilog語言在FPGA中運用的簡單實例有什么,求舉例?

2016-03-16 00:59:00

用的FPGA是Sparten6系列的XC6SLX100T的FPGA,選用的FLASH是W25Q128的SPI模式FLASH,燒寫程序大小大概25M,燒寫完后上電啟動,FPGA加載時長大概12秒,啟動比較慢,煩請大佬看看什么原因造成的,有什么解決措施能提高啟動時間?謝謝

2020-06-10 13:55:50

《FPGACPLD設計工具──Xilinx+ISE使用詳解》

2018-01-12 15:04:43

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

發現labview并不是想象中的那么容易,當然,也不會放棄,具體的不知道 labview 到底在現實中是怎么運用?現在自己也沒機會接觸這方面的工作,望前輩給些實例看看,自己也下載了很多的例子,但在實際中是怎么運用的就不是很清楚了。

2013-01-28 16:47:38

1. 現有一塊xc7vx690tffg芯片。2. 之前寫的fpga程序都是通過在vivado上JTAG線的方式,將mcs文件燒寫到flash中,現聽說部分加載fpga程序,可以直接更改上位機程序里的bin文件方式就可部分加載fpga程序,更為方便快捷,還請問部分加載技術該如何實現。

2021-03-01 10:45:28

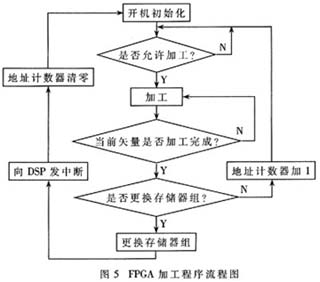

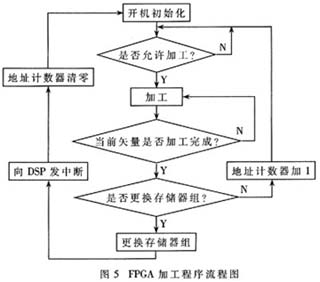

為什么采用FPGA去加載TigerSHARC DSP?如何去設計加載狀態機?加載狀態機有哪幾個典型的加載過程?

2021-04-28 06:30:11

Altera系列FPGA芯片IP核詳解

2016-08-19 17:24:48

卡爾曼濾波在四軸飛行器上的實際運用

2017-04-02 12:39:08

反熔絲FPGA在密碼芯片設計中的運用

2012-08-17 10:37:41

大疆華為等企業fpga面試題詳解視頻。附件是網盤

2018-07-10 10:49:02

使用ICAP-spartan6發送比特流。任務是當我按下按鈕1時,spartan6 FPGA加載黃金比特流,由LED指示燈閃爍表示。類似地,當我按下按鈕2時,FPGA使用ICAP重新配置多引導比特流。請幫我解決這個問題。我有

2019-07-19 12:31:58

目前實現加載的方法通常有兩種:一種是用專用Cable通過JTAG口進行數據加載,另一種是外掛與該FPGA廠商配套的PROM芯片。前者需要在PC機上運行專用的加載軟件,直接下載到FPGA片內,所以掉電

2019-09-05 07:50:03

我正試圖在a7 fpga中實現回退多重啟動。以下是黃金圖像的ise工具中的設置:當我完成將黃金圖像位文件加載到fpga中時,完成的led可以點亮。但當我完成將黃金映像mcs文件加載到fpga中,并在

2020-06-01 06:17:37

目前實現加載的方法通常有兩種:一種是用專用Cable通過JTAG口進行數據加載,另一種是外掛與該FPGA廠商配套的PROM芯片。前者需要在PC機上運行專用的加載軟件,直接下載到FPGA片內,所以掉電

2019-10-11 06:15:28

請問一下有沒有采用EEPROM對大容量FPGA芯片數據實現串行加載的實際方案?

2021-04-08 06:01:39

你好我正在使用ZC706板傳輸調制信號。我們以文本和mat格式的形式提供這些調制信號。我想將這些調制信號加載到FPGA中,所以有沒有辦法直接將數據加載到FPGA中,當我們生成.bit文件時,這些數據

2019-05-06 07:25:49

Altium designer在FPGA及嵌入式智能方面有哪些優勢?怎樣運用Altium Designer平臺實現FPGA的嵌入式系統設計?

2021-04-28 07:05:33

需要將FPGA程序通過I2C或者RS232加載到FPGA內部,然后通過FPGA存儲到SPI FLASH中,再次上電后從SPI FLASH加載。 這個過程中,有以下幾個問題:1.怎樣將.v文件轉換成

2016-04-29 14:46:21

的閃存系列,但內存大小更大。我第一次使用MCS文件加載Flash時工作正常。然而,從那以后,我無法加載FPGA。空白檢查表示設備不是空白,但擦除功能不起作用。此外,只是嘗試通過IMPACT重新編程閃存也

2019-03-19 06:25:56

嗨,我正在使用斯巴達3e入門套件和ise 10.2軟件。我無法將.bit文件加載到fpga中,因為iMPACT顯示錯誤:寫cmdbuffer失敗20000015.write cmdbuffer失敗20000015.Loopback測試失敗。發送字符= 00,接收字符= 00.Cable連接失敗。請幫忙。問候,阿希什

2019-08-29 10:47:39

嗨,我想用許多位文件對FPGA進行編程,即加載一個運行它的位文件并將其結果存儲在一個文件中,然后加載下一個文件,依此類推N位文件。我遇到了多重啟動,看起來像是我問題的解決方案。但在引用網絡時,我發現

2020-04-06 13:23:51

如何用EEPROM對大容量FPGA芯片數據實現串行加載?如何設計并-串轉換時序?

2021-04-29 07:13:12

各位前輩,FPGA采用并行加載方式,現CPLD外掛一片FLASH,要求用CPLD控制加載時序,從FLASH讀取代碼,送入FPGA,應該怎么用CPLD控制加載時序,程序應該怎么寫,有可以參考的資料嗎,謝謝各位了!

2013-02-21 12:07:34

多片fpga組成jtag鏈的時候如何加載?

2023-08-11 09:10:26

紅芯FPGA開發板例程詳解

2013-07-28 20:25:33

我有一個用于過時的Xilinx FPGA的加載文件。是否有機會將其轉換為Xilinx新FPGA的文件?例如斯巴達。以上來自于谷歌翻譯以下為原文I have a loading fille fora

2019-02-13 07:53:44

新手,求基于fpga的spi接口運用實例,小弟感激不盡

2016-01-12 11:06:13

的形狀,serpitine shpae,經過了多少轉。是的,我可以理解寄存器編程位,你只需要編程1和0來編程FPGA的配置但我無法想象程序如何轉換,因此編程芯片并使最終的電線看起來像。軟件如何控制實際

2019-04-15 14:17:53

實際的FPGA編程

2009-07-23 09:54:22 72

72 本文運用黑盒測試的基本理論,提出了FPGA邏輯設計的測試模型,分析了FPGA邏輯設計的基本方法和步驟,最后結合一個實際項目說明了FPGA邏輯設計的測試驗證過程。關鍵詞:黑盒

2009-08-19 09:12:41 9

9 實際運用中差分信號線的分析和LAYOUT隨著近幾年對速率的要求快速提高,新的總線協議不斷的提出更高的速率。傳統的總線協議已經不能夠滿足要求了。串行總線由于更好的抗干

2009-09-30 13:04:16 0

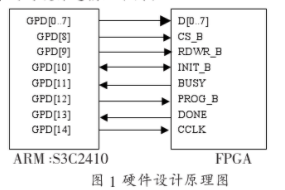

0 本文實現了一種基于ARM-Linux 的FPGA 程序加載方法,詳細討論了加載過程中各個階段程序對配置管腳的操作,給出了硬件實現,編寫了運行于ARM 處理器的嵌入式Linux上的驅動程序。

2009-12-19 16:26:26 30

30 基于ARM+FPGA的可重構控制器設計及其在加載系統中的應用:文章提出了一種基于ARM+FPGA結構的可重構控制囂的設計方法.并采用此方法開發了用于加載系統的2通道電液伺服控制器

2010-03-02 12:03:21 29

29 DSP和FPGA在大尺寸激光數控加工系統中的運用

激光切割和雕刻以其精度高、視覺效果好等特性,被廣泛運用于廣告業和航模制造業。在大尺寸激光加工系統的開發過程中

2009-11-12 10:04:03 503

503

汽車電子中的DSP和FPGA運用

1 引言

20世紀末,全球范圍內興起的信息革命浪潮,為汽車工業的突破性發展提供了千載難逢的機遇,信息

2010-03-03 11:10:28 358

358 介紹了一種基于SRAM技術的FPGA可編程邏輯器件的編程方法,能在系統復位或上電時自動對器件編程。有效地解決了基于SRAM的FPGA器件掉電易失性問題,針對當前系統規模的日益增大,本文提出了一種用單片機對多片FPGA自動加載配置的解決方案.

2011-03-15 16:41:22 21

21 根據FPGA芯片加載時序分析,本文提出了采用通過市面上常見的Flash ROM芯片替代專用PROM的方式,通過DSP的外部高速總線進行FPGA加載;既節約了系統成本,也能達到FPGA上電迅速加載的目的

2011-08-16 16:26:14 1558

1558

異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 一、類加載器 類加載器(ClassLoader),顧名思義,即加載類的東西。在我們使用一個類之前,JVM需要先將該類的字節碼文件(.class文件)從磁盤、網絡或其他來源加載到內存中,并對字節碼進行

2017-09-27 14:27:21 0

0 工作效率。通過FPGA 的多重配置可以有效地精簡控制結構的設計,同時可以用邏輯資源較少的FPGA 器件實現需要很大資源才能實現的程序。以Virtex5系列開發板和配置存儲器SPIFLASH為基礎,從硬件電路和軟件設計兩個方面對多重配置進行分析,給出了多

2017-10-12 17:57:08 15

15 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 滿足設計需求。FPGA的多重加載可以解決可編程資源不足的難題。FPGA多重加載是將設計的多個模式的比特文件存儲到Flash,用戶可以根據需要選擇加載不同模式的比特文件。FPGA的多重加載解決了可編程資源不足的問題,提高了FPGA可編程資源的利用率。

2017-11-18 04:41:50 5879

5879

在FPGA編寫代碼時就將更多的問題考慮到位。本文針對項目過程中碰到的一些實際問題進行闡述,希望可以為大家在FPGA編程過程中提供一些幫助。 項目描述:該項目是一個實時頻譜監測、流盤以及跳頻信號檢測

2017-11-18 05:20:01 10581

10581

本文檔內容介紹了GD32單片機程序分散加載的方法,圖像詳解,供參考。

2017-11-22 11:02:01 38

38 多重通訊裝置結構設計 (Device’s Architecture),芯片的底層結構設計 (Underlying Chipset Architecture), 軟件驅動和編寫測試軟件的靈考能力;所以

2017-12-08 08:13:24 1217

1217

本文檔內容介紹了基于xilinxFPGA選型詳解,供參考查閱

2018-03-15 15:58:01 4

4 29張圖詳解PLC技術的實際應用,PLC技術的實際案例匯總。

2018-08-25 10:11:18 15193

15193 Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據不同時刻的需求,可以從FLASH 中貯存的多個比特文件選擇加載其中的一個,實現系統功能的變換。

2018-12-04 08:37:00 4654

4654

FPGA 的配置數據通常存放在系統中的存儲器件中,上電后控制器讀取存儲器中的bit 文件并加載到FPGA 中,配置方式有JTAG、從并、從串、主從4 種,不同廠家叫法不同,但實現方式基本都是一樣的。

2018-10-30 08:58:00 7921

7921

FPGA有多種配置/加載方式。粗略可以分為主動和被動兩種。主動加載是指由FPGA控制配置流程,被動加載是指FPGA僅僅被動接收配置數據。

2018-10-05 10:12:00 17251

17251 可編程的雙重優點,被廣泛應用于通信領域中。FPGA在上電后,需要加載配置文件對內部各功能模塊進行初始化,而配置文件加載的效率直接影響系統的初始化時間。因此如何設計一種高效的FPGA加載方案,是通信系統設計中的一個重要環節。

2019-02-19 14:49:08 1900

1900

加載系統。該系統通過USB芯片將PC中的配置文件傳送給CPLD,CPLD再將其寫入FLASH芯片,FLASH芯片可以長久地存儲配置文件。這樣FPGA每次上電后CPLD將FLASH中的配置文件讀出來配置

2019-02-20 15:36:23 2799

2799

在系統上電時,需要從外部載入所要運行的程序,此過程被稱為程序加載。多數情況下,從外部專用的 讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當系統需要容量大而且 FPGA要加載的程序可以

2019-03-22 16:20:14 952

952 本設計采用FPGA技術,在FPGA中實現8051單片機的軟核,將外部SPI Flash中的代碼數據加載到FPGA內部ram,然后復位 MC8051,實現外部flash啟動MC8051。

2019-06-11 17:47:00 3

3 FPGA在系統上電時,需要從外部載入所要運行的程序,此過程被稱為程序加載。多數情況下,FPGA從外部專用的 EPROM讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當系統需要容量大而且

2020-08-13 17:16:46 1805

1805

基于SRAM結構的FPGA容量大,可重復操作,應用相當廣泛;但其結構類似于SRAM,掉電后數據丟失,因此每次上電時都需重新加載。

2021-03-26 13:52:58 4008

4008

(UG332) 即為《Spartan-3 系列配置用戶指南》 在此用戶指南中,并未涵蓋有關從 SPI 閃存啟動時,如何使用內部配置訪問端口 (ICAP) 來支持在 Spartan-3AN FPGA

2021-06-25 17:25:26 1629

1629 淺談光伏并網柜的實際運用(實用開關電源技術)-淺談光伏并網柜的實際運用? ? ? ? ? ? ? ? ? ? ? ? ??

2021-09-23 17:38:14 14

14 FPGA-DCM使用詳解(通信電源技術期刊編輯部電話)-該文檔為FPGA-DCM使用詳解文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 因為在S6或者其他7系列的FPGA中,是有一套非常成熟的FPGA加載機制(Xilinx有很詳細的指導手冊),但是來到Zynq時代,這個方式變了。為什么呢?因為現在zynq上有ARM了,所有的加載工作實際上可以借由ARM來實現

2022-05-09 10:53:02 2263

2263 電子發燒友網站提供《安路EG4X FPGA從動串行加載模式.pdf》資料免費下載

2022-09-27 10:55:18 1

1 電子發燒友網站提供《安路EG4X FPGA從動并行加載模式.pdf》資料免費下載

2022-09-27 10:44:27 1

1 在不帶內置ARM核的AMD FPGA產品系列中,FPGA的程序加載方式并沒有發生大的變化

2023-07-07 14:14:58 981

981

電子發燒友App

電子發燒友App

評論