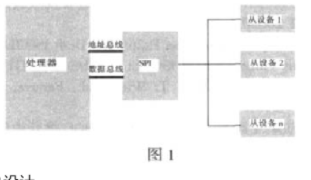

最近,Digilent開源技術(shù)社區(qū)收到了兩個(gè)關(guān)于如何在Zynq SoC和Zynq UltraScale + MPSoC上實(shí)現(xiàn)SPI接口的問題。在回答了這些問題之后,我認(rèn)為有必要寫一篇如何實(shí)現(xiàn)SPI的文章,在此分享。

當(dāng)我們?cè)谠O(shè)計(jì)中使用Zynq SoC或Zynq UltraScale + MPSoC時(shí),可以有兩種方法來實(shí)現(xiàn)SPI接口:

1. 使用PS端的SPI控制器(PS端有兩個(gè)SPI控制器)

2. 在PL端使用配置成標(biāo)準(zhǔn)SPI通信的AXI Quad SPI (QSPI) IP模塊

?

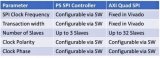

我們可以根據(jù)應(yīng)用的要求來選擇使用哪種方法實(shí)現(xiàn)SPI控制器。兩種SPI的實(shí)現(xiàn)方式都支持四種SPI模式,并且都可以作為SPI主設(shè)備或SPI從設(shè)備。下表列出了它們之間的一些差異:

首先,我們演示一下如何使用PS端的SPI控制器進(jìn)行SPI傳輸。在Zynq MIO configuration選項(xiàng)卡中選中SPI控制器,這就將SPI包含在了設(shè)計(jì)中。在這個(gè)例子中,我將把SPI信號(hào)連接到Digilent ARTY Z7開發(fā)板的SPI接口,這需要通過PL I/O使用EMIO。

圖:?jiǎn)⒂肧PI并將端口映射到EMIO

在選擇好相應(yīng)的選項(xiàng)后,唯一要做的就是連接SPI端口的I/O。具體要如何進(jìn)行連接取決于我們是需要配置一個(gè)SPI主設(shè)備還是從設(shè)備。在SPI控制器上,每個(gè)SPI端口都有對(duì)應(yīng)的可用輸入(xxx_i)輸出端口(xxx_o)。端口的正確連接十分關(guān)鍵,如果連接錯(cuò)誤,當(dāng)運(yùn)行應(yīng)用程序時(shí),將得到完全錯(cuò)誤的運(yùn)行結(jié)果,這可能需要花費(fèi)我們幾個(gè)小時(shí)的時(shí)間來尋找問題的源頭。另外,當(dāng)配置成SPI從設(shè)備時(shí),有一個(gè)名稱為Slave Select的輸入;而當(dāng)用作SPI主設(shè)備時(shí),將有三個(gè)選擇引腳。

當(dāng)正確配置好I/O并創(chuàng)建了工程,我們就可以使用應(yīng)用軟件中的SPI配置選項(xiàng)將SPI控制器配置成為主設(shè)備或從設(shè)備。使用PS SPI控制器配置和傳輸數(shù)據(jù),需要使用由XSPIps.H定義的BSP(板卡支持包)所提供的API接口。在第一個(gè)例子中,我們將SPI控制器配置為SPI主設(shè)備。

默認(rèn)情況下,SPI使用8位傳輸。但是,我們也可以將傳輸配置成更大的16或32位。對(duì)于8位傳輸,我們?cè)贑程序中可以使用u8數(shù)據(jù)類型。對(duì)于16位或32位傳輸,分別使用16位或32位對(duì)數(shù)據(jù)進(jìn)行讀寫緩存。

一開始,這可能會(huì)導(dǎo)致一些問題或生成編譯器警告,因?yàn)閳?zhí)行如下所示的兩個(gè)數(shù)據(jù)傳輸API函數(shù)都需要發(fā)送和接收緩沖區(qū)的數(shù)據(jù)類型為u8:

s32 XSpiPs_Transfer(XSpiPs *InstancePtr, u8 *SendBufPtr, u8 *RecvBufPtr, u32 ByteCount);

s32 XSpiPs_PolledTransfer(XSpiPs *InstancePtr, u8 *SendBufPtr, u8 *RecvBufPtr, u32 ByteCount);

為了解決使用u16和u32數(shù)據(jù)類型的問題,我們需要將緩沖區(qū)轉(zhuǎn)換為u8指針,如下所示:

XSpiPs_PolledTransfer(&SpiInstance, (u8*)&TxBuffer, (u8*)&RxBuffer, 8);

這樣設(shè)置將就使得我們能夠傳輸大小為8,16或32位的數(shù)據(jù)了。為了演示這一設(shè)置,我將SPI主設(shè)備IO連接到Digilent Digital Discovery口袋儀器來測(cè)試傳輸?shù)臄?shù)據(jù)。在應(yīng)用軟件中使用上述方法將數(shù)據(jù)寬度從8位變?yōu)?6位。

?

圖:Arty Z7開發(fā)板與Digital Discovery口袋儀器

圖:Zynq SoC PS SPI主設(shè)備發(fā)送四個(gè)8位字

圖:PS SPI主設(shè)備發(fā)送四個(gè)16位字

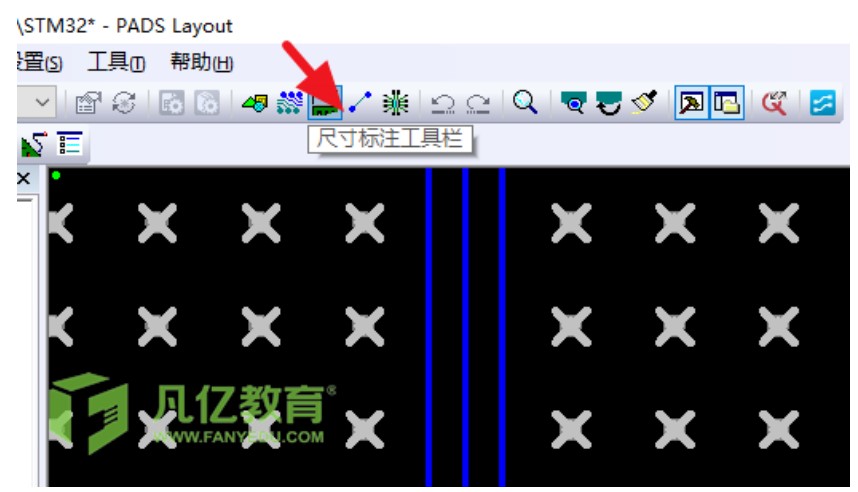

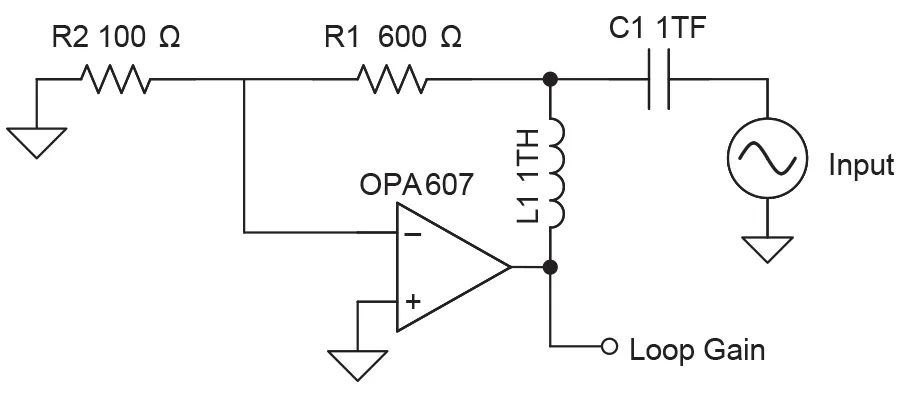

另一個(gè)實(shí)現(xiàn)SPI接口的方法是使用AXI QSPI IP核,使用這種方法需要在Vivado中進(jìn)行的設(shè)置比較多,需要花費(fèi)比較長的時(shí)間。在AXI QSPI配置對(duì)話框中,我們可以配置傳輸?shù)膶挾取㈩l率和從設(shè)備的數(shù)量。最重要的一個(gè)選項(xiàng)就是選擇AXI QSPI IP核是作為SPI主設(shè)備還是從設(shè)備。如果要配置成SPI主設(shè)備,就必須選中enable master mode選項(xiàng)。如果要配置成為從設(shè)備,則必須取消該選項(xiàng)以確保SPISel輸入引腳的存在。當(dāng)SPI IP核作為從設(shè)備時(shí),該引腳需要連接到主設(shè)備的slave select.端口。

圖:配置AXI Quad SPI

與PS SPI控制器一樣,BSP也為SPI IP提供一個(gè)API接口。我們可以用它來開發(fā)應(yīng)用軟件,這個(gè)API是在文件XSPI.h中定義的。作為例子的第二部分,我將使用這個(gè)API來配置AXI QSPI作為SPI從設(shè)備。

為了演示創(chuàng)建軟件后AXI QSPI核可以正確的以SPI從設(shè)備方式進(jìn)行工作。我再次使用Digilent Digital Discovery口袋儀器作為SPI主設(shè)備,使數(shù)據(jù)在兩者之間傳輸。

圖:SPI從設(shè)備收發(fā)數(shù)據(jù)(藍(lán)色的數(shù)據(jù)由Zynq SPI Slave輸出)

有興趣的朋友,可以點(diǎn)擊: ,下載參考上述兩個(gè)演示例程的Vivado設(shè)計(jì)文件。

圖:最終的block diagram

當(dāng)然,如果使用Xilinx FPGA代替Zynq SoC或Zynq UltraScale MPSoC,則可以使用具有相同AXI QSPI配置的MicroBlaze軟核來實(shí)現(xiàn)SPI接口。只要正確地將其定義為主設(shè)備或從設(shè)備即可。

希望這篇文章能夠幫助你了解如何使用這兩種不同的方法創(chuàng)建主/從SPI接口。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論