題主最近開始接觸和FPGA的方案驗(yàn)證相關(guān)的工作內(nèi)容,需要把握FPGA內(nèi)部資源的詳細(xì)信息,所以又仔細(xì)查看了官方的器件手冊(cè)。這一次給大家分享的內(nèi)容主要涉及Xilinx FPGA內(nèi)的CLBs,SelectIO和Clocking資源,適合對(duì)FPGA設(shè)計(jì)有時(shí)序要求,卻還沒有足夠了解的朋友。

參考器件上,雖然一些專用的資源都集中在高端的FPGA型號(hào)中,不過題主想了想,還是把它們放在該系列后續(xù)的文章中吧。下文中的舉證皆來自Spartan6器件文檔,所以也不會(huì)超出Spartan6涵蓋內(nèi)容。

傳統(tǒng)的FPGA內(nèi)部資源分類作三類,可配置邏輯模塊(Configurable Logic Block)、輸入輸出模塊(InputOutput Block)和內(nèi)部布線資源(Interconnect)三個(gè)部分,這些大家都知道的。隨著FPGA的發(fā)展,為了滿足對(duì)信號(hào)處理和片上儲(chǔ)存的需要,又在前三類基礎(chǔ)上增加了塊RAM(BRAM)、時(shí)鐘管理單元和硬件乘法器,之后又在部分系列里增加了PPC和高速串行輸入與輸出等等。

下文將要提到的CLB、SelectIO和Clocking資源里,SelectIO資源是比較豐富的一類,所以在順序上把它放在最后。

正文:

首先說說CLB吧,它是一類最重要,其實(shí)也是最易于使用的結(jié)構(gòu)。Xilinx把盡可能多的資源配置接口開放給用戶,但是出于控制開發(fā)周期,并且提高系統(tǒng)穩(wěn)定性的考慮,CLB不是其中之一,它的配置方案幾乎全部由IDE實(shí)現(xiàn)過程智能分配,用戶可以約束特殊Slice的位置,但很少有這種必要,交給IDE來完成會(huì)更加有效。

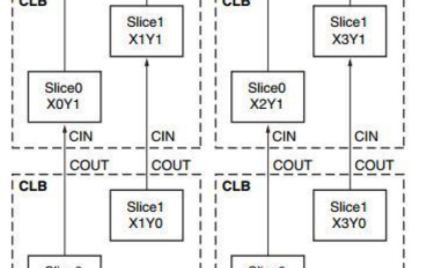

來看看它的結(jié)構(gòu)(有一些圖片資料不好找,后期整合的時(shí)候會(huì)補(bǔ)全):

① CLB資源會(huì)根據(jù)FPGA的尺寸被內(nèi)部時(shí)鐘網(wǎng)絡(luò)分割成若干個(gè)區(qū)域,一般每個(gè)區(qū)域是40個(gè)CLB單元高度;

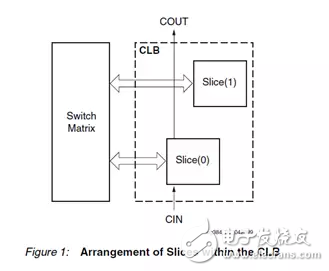

② 每個(gè)CLB連接到一個(gè)開關(guān)矩陣來接入全局布線矩陣;

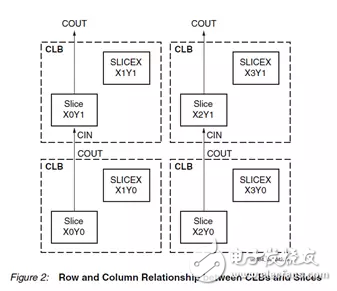

③ 一個(gè)CLB單元包含 一對(duì)Slice單元(兩個(gè)Slice無直接連接,并且在CLB間成列分布,每個(gè)縱列的Slice有一條獨(dú)立的進(jìn)位鏈);

④ 一個(gè)CLB中下方的Slice記為Slice0,上方的記為Slice1;

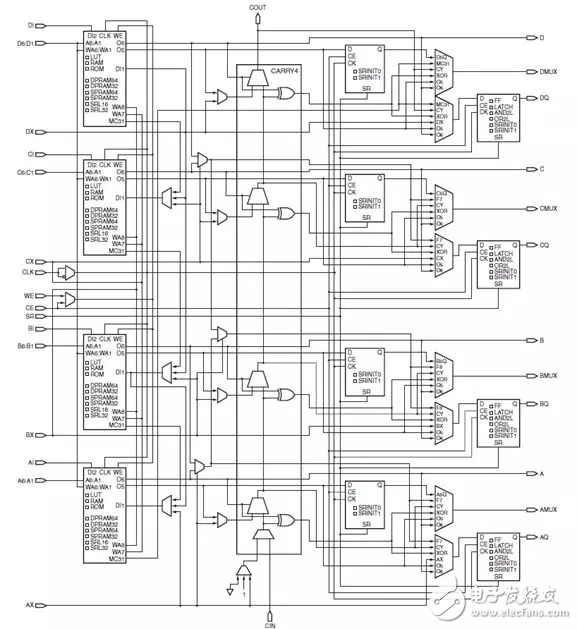

⑤ 每個(gè)Slice包含4個(gè)查找表(LUTs),8個(gè)存儲(chǔ)單元(FF),以及一些選擇器和進(jìn)位邏輯,這些單元用于提供邏輯、算術(shù)和ROM功能;

⑥ 有一部分Slice支持DistributedRAM和32位移位寄存器功能,被記為SLICEM,其他的記為SLICEL(一個(gè)CLB最多有一個(gè)SLICEM,每個(gè)CLB縱列至少有一個(gè)SLICEM,在DSP48E(XilinxFPGA內(nèi)的硬件乘法器)縱列旁的兩個(gè)CLB縱列,每一個(gè)CLB都有SLICEM)。

SLICEM

(DistributedRAM和ShiftRegisters資源都在LUTs上掛載)

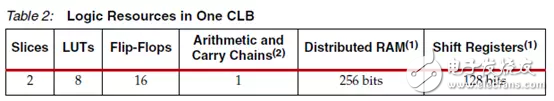

最后看一下一個(gè)CLB中的資源總量:

當(dāng)然具體到Slice中幾種資源還有一些細(xì)節(jié)需要關(guān)注,主要是和LUTs的特性相關(guān),不過等后面加入案例來講吧。如果此前你已經(jīng)對(duì)FPGA設(shè)計(jì)有一些經(jīng)驗(yàn)和體會(huì)的話,現(xiàn)在想必已經(jīng)對(duì)FPGA的查找表結(jié)構(gòu)有了自己的理解。

還是簡(jiǎn)單提及一下LUTs的作用,就是查表,,,在我看來,它就是一個(gè)6輸入2輸出的多功能選擇器,可以直接把Verilog中always塊的行為映射到它的行為上,通過對(duì)輸入端口的連接配置,它就能夠?qū)崿F(xiàn)我們需要的信號(hào)行為模型。完整的過程以后會(huì)加入案例來講。讓我們緩一口氣,先進(jìn)入下一個(gè)內(nèi)容。

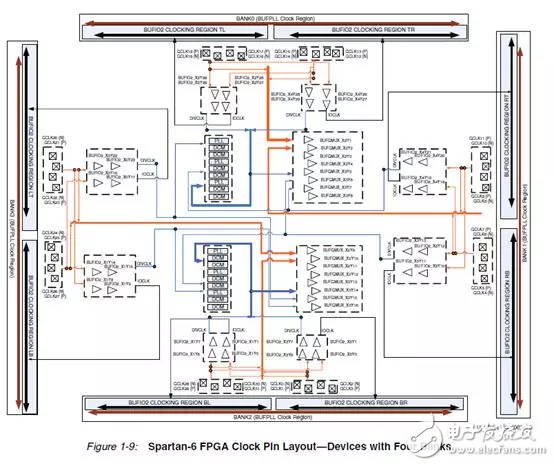

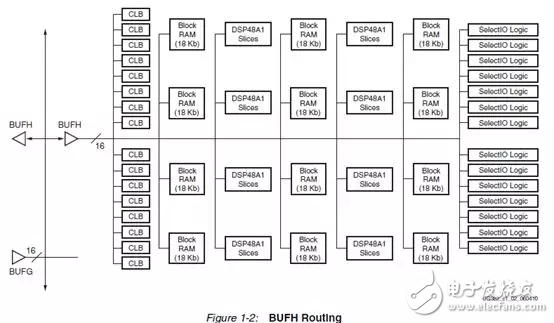

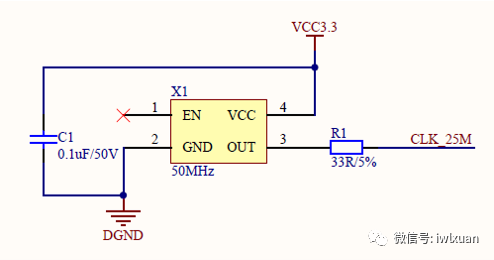

XilinxFPGA內(nèi)部有復(fù)雜的時(shí)鐘資源網(wǎng)絡(luò),來維護(hù)大數(shù)量邏輯資源條件下的時(shí)序要求和系統(tǒng)穩(wěn)定。主要分為全局時(shí)鐘線和局部時(shí)鐘網(wǎng)絡(luò),在Spartan6上,還有數(shù)字時(shí)鐘管理器(DCM)和數(shù)字鎖相環(huán)(PLL)兩種硬核資源,用以輔助時(shí)鐘資源網(wǎng)絡(luò)。Spartan6內(nèi)部提供了16個(gè)全局時(shí)鐘驅(qū)動(dòng)buffer和40個(gè)局部時(shí)鐘的,它們均勻地分布在上文提到的被時(shí)鐘網(wǎng)絡(luò)分割出來的各區(qū)域中:

我們可以通過例化BUFG和BUFIO等原語調(diào)用這些資源,為GTP(H/X/Z)和DDR、AD/DA這樣的高速信號(hào)組提供更低相位偏移的時(shí)鐘參考,但是時(shí)鐘資源的分配有比較多的使用規(guī)則,在資源有限而布線拮據(jù)的情況下,時(shí)常會(huì)被Xilinx規(guī)則檢查器告知使用違例。之后題主會(huì)結(jié)合一些真實(shí)案例來引導(dǎo)大家去規(guī)避這樣的錯(cuò)誤。

時(shí)鐘資源所用的篇幅也很短,事實(shí)上涉及到時(shí)鐘的問題很多,但是要在需要的時(shí)候再去認(rèn)識(shí)才有價(jià)值,不然沒有依據(jù)的去了解,也沒有什么價(jià)值。接下來看看FPGA內(nèi)部最為豐富的I/O資源,畢竟現(xiàn)在市場(chǎng)上FPGA最廣泛和最擅長(zhǎng)的,就是做接口,下文包含的很多內(nèi)容,在多個(gè)系列的FPGA上都是差不多的規(guī)范:

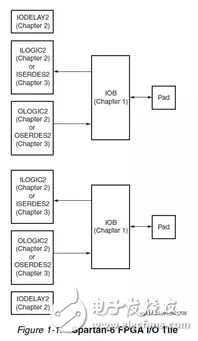

① FPGA的I/O資源被分布在若干個(gè)Bank中,每個(gè)Bank中有20個(gè)I/O Tile;

② 一個(gè)Tile包含2個(gè)IOB,2個(gè)ILOGIC,2個(gè)OLOGIC和2個(gè)IOEDLAY,用于對(duì)雙端(差分)信號(hào)配對(duì);

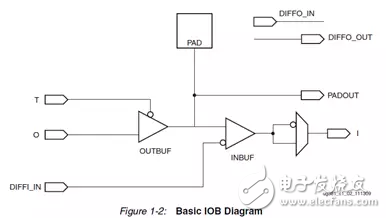

③ IOB包含輸入、輸出和三態(tài)驅(qū)動(dòng),可配置為不同的I/O標(biāo)準(zhǔn);IOB直連一對(duì)I(O)LOGIC,I(O)LOGIC包含數(shù)據(jù)I/O的邏輯資源和三態(tài)控制,I(O)LOGIC也可以通過調(diào)用相關(guān)原語配置為I(O)SERDES,實(shí)現(xiàn)數(shù)據(jù)的串并行轉(zhuǎn)換;

IOB單元支持大量的接口標(biāo)準(zhǔn),可以對(duì)負(fù)載能力和轉(zhuǎn)換速率進(jìn)行控制。并且同Bank內(nèi)支持復(fù)合電壓輸出,以驅(qū)動(dòng)一些低壓I/O標(biāo)準(zhǔn),不過對(duì)參考電平的選擇有一些規(guī)則。

對(duì)于單端和雙端信號(hào)I/O,可以選擇很多種buffer配置方式去驅(qū)動(dòng)這些信號(hào),當(dāng)然IDE的實(shí)現(xiàn)過程中也幫我們配置好了很多,作為用戶,常用的像IBUFG、IBUFR這樣的時(shí)鐘驅(qū)動(dòng)資源,IBUFDS、OBUFDS實(shí)現(xiàn)信號(hào)單雙端轉(zhuǎn)換,以及用OBUFT實(shí)現(xiàn)三態(tài)控制等等。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論