先給大家簡單快速地介紹一下 Vivado 集成設(shè)計環(huán)境,即 IDE。當打開 Vivado 工程后,會有一個工程概要,向您介紹工程的設(shè)置、警告和錯誤信息以及工程的一般狀態(tài)。

2012-04-25 09:00:43 6408

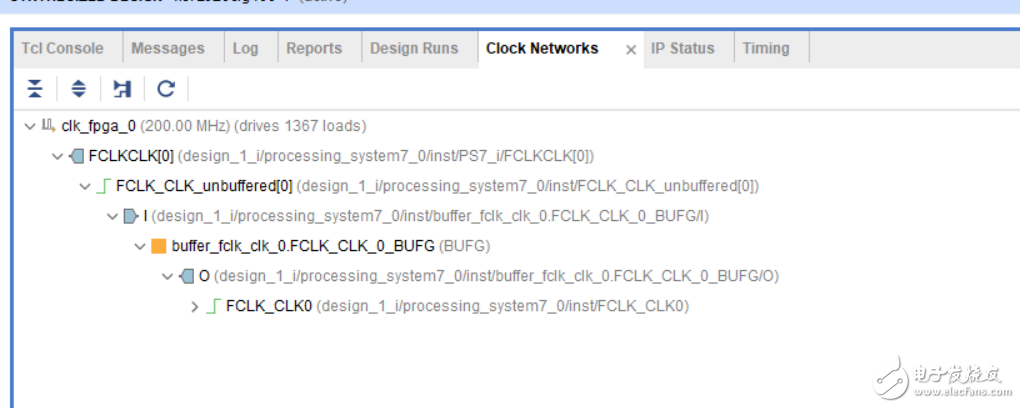

6408 路徑分析問題作一介紹: 1、時鐘網(wǎng)絡(luò)分析 時鐘網(wǎng)絡(luò)反映了時鐘從時鐘引腳進入FPGA后在FPGA內(nèi)部的傳播路徑。 報告時鐘網(wǎng)絡(luò)命令可以從以下位置運行: ① VivadoIDE中的Flow

2020-11-29 10:34:00 7410

7410 時序約束的目的就是告訴工具當前的時序狀態(tài),以讓工具盡量優(yōu)化時序并給出詳細的分析報告。一般在行為仿真后、綜合前即創(chuàng)建基本的時序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進行最基本時序約束相關(guān)腳本。

2022-03-11 14:39:10 8731

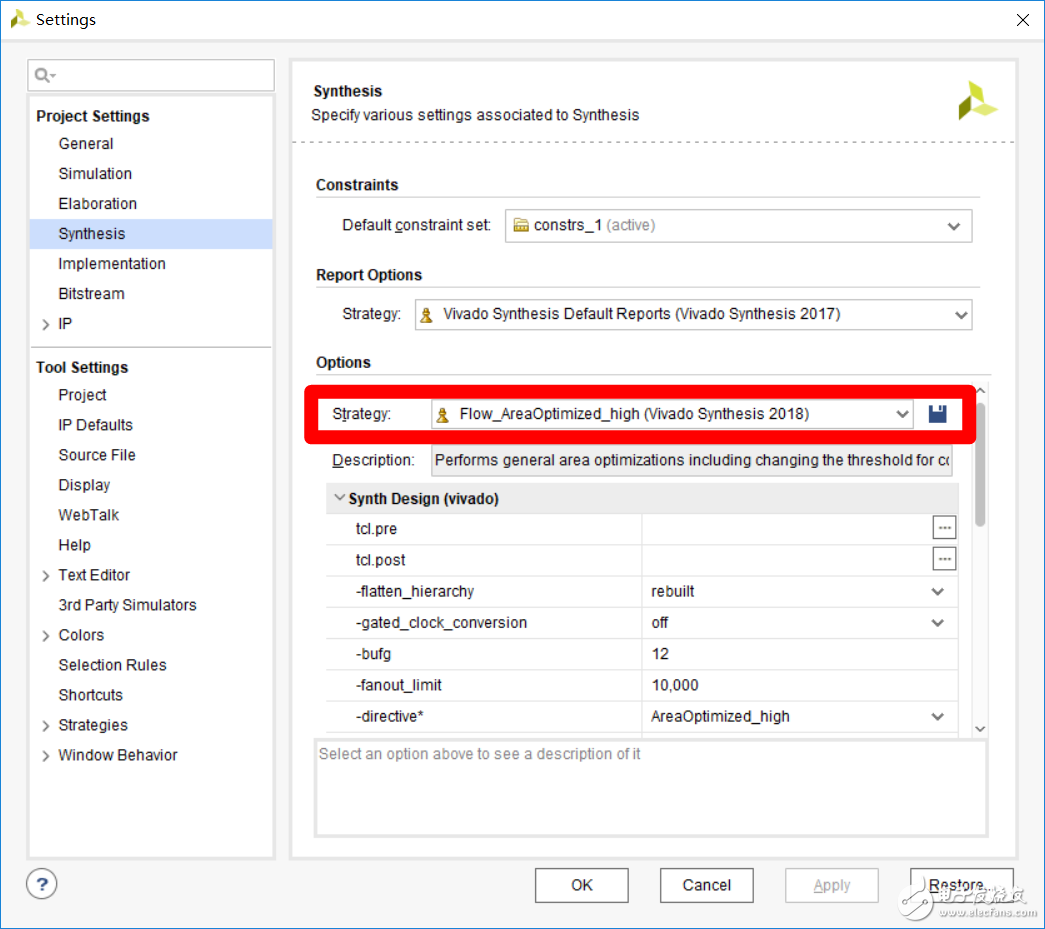

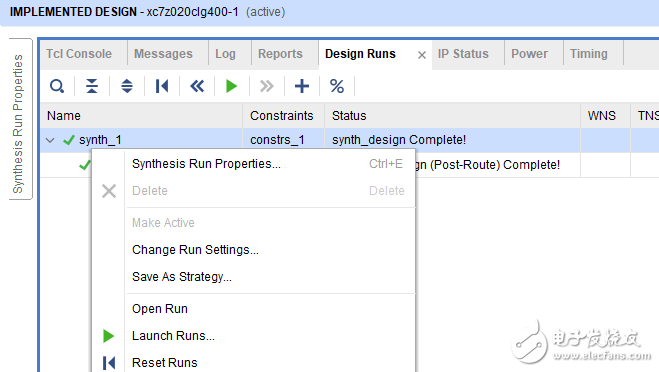

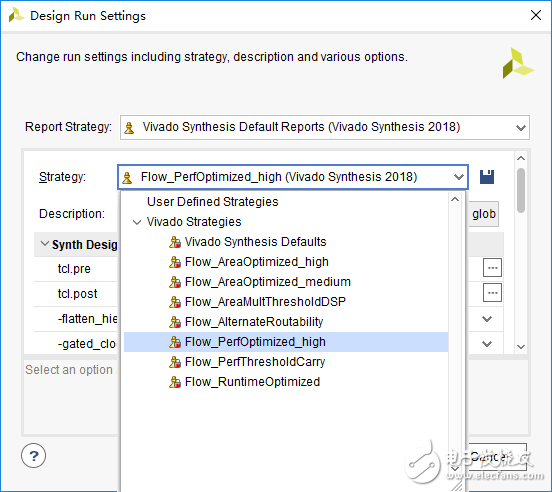

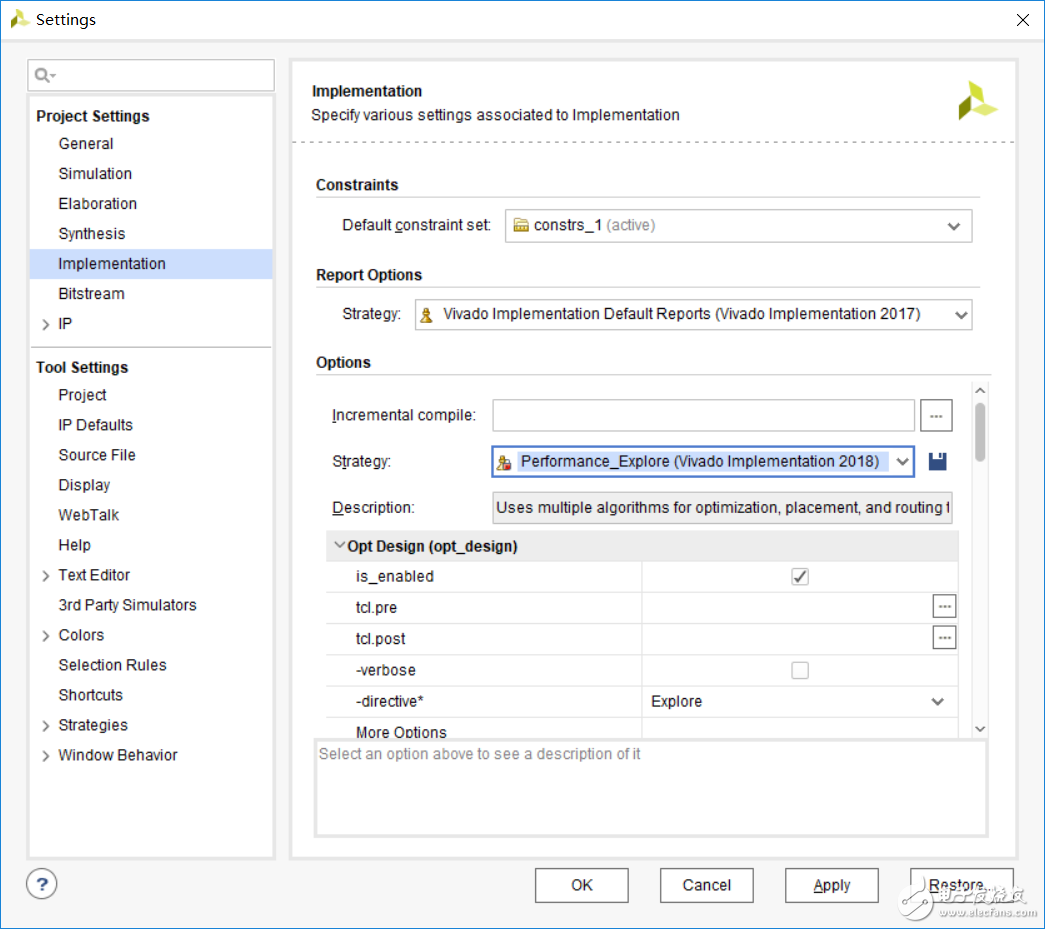

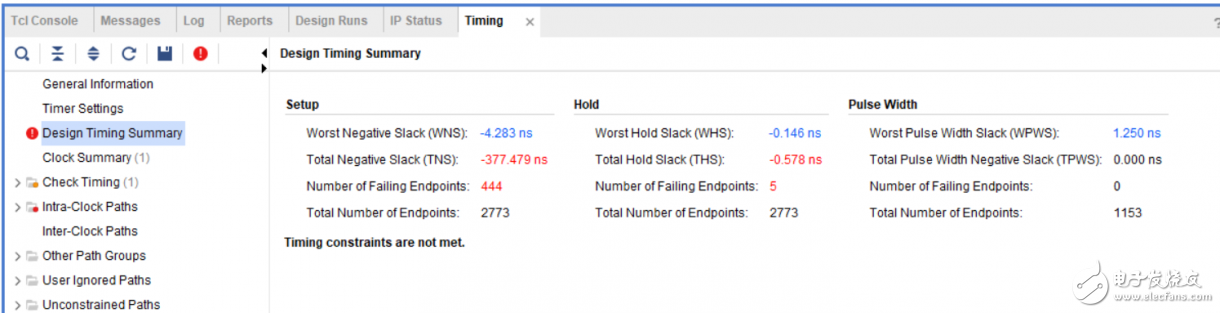

8731 在Vitis完成這個過程的底層,實際調(diào)用的是Vivado。Vitis會指定默認的Vivado策略來執(zhí)行綜合和實現(xiàn)的步驟。當默認的Vivado策略無法達到預(yù)期的時序要求時,我們需要在Vivado中分析

2022-08-02 08:03:38 1016

1016

時序分析是FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-10-21 09:28:58 1284

1284 學習。個人學習的時候可以根據(jù)實際情況選擇最高至Vivado2019.1。(從Vivado2019.2開始,PS開發(fā)使用Vitis,沒有SDK了)第1章 FPGA技術(shù)分析 / 11.1 FPGA內(nèi)部結(jié)構(gòu)

2020-10-21 18:24:48

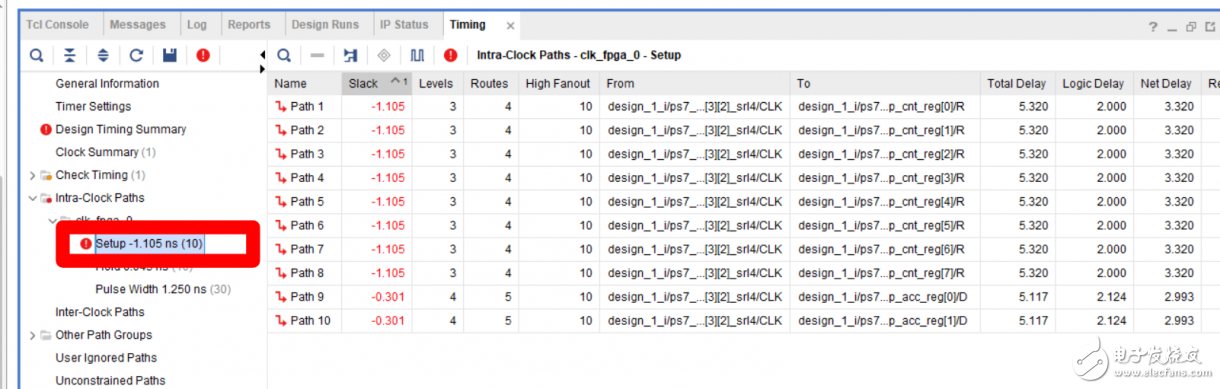

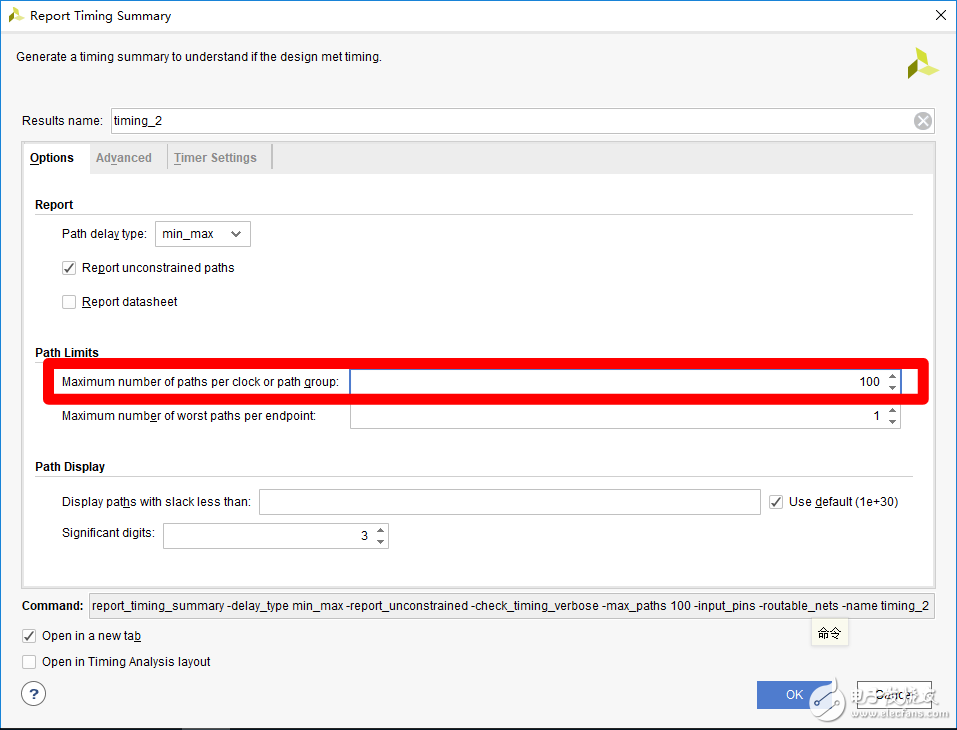

Vivado運行Report Timing Summary時,只顯示各個子項目最差的十條路徑,很可能并不包含你最關(guān)心的路近,這個時候顯示指定路徑的時序報告就顯得很重要了,下面就簡單介紹一下

2021-01-15 16:57:55

的。來獲取關(guān)于原始的 ISE 設(shè)計套件以及 Xilinx 在 Vivado 中對這些開發(fā)工具做改進的理由的討論。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的設(shè)備,但是

2021-01-08 17:07:20

嗨,您能告訴我與vivado時序分析相關(guān)的用戶指南嗎?謝謝

2020-03-16 08:14:45

vivado軟件的安裝教程以及license

2023-12-21 19:50:00

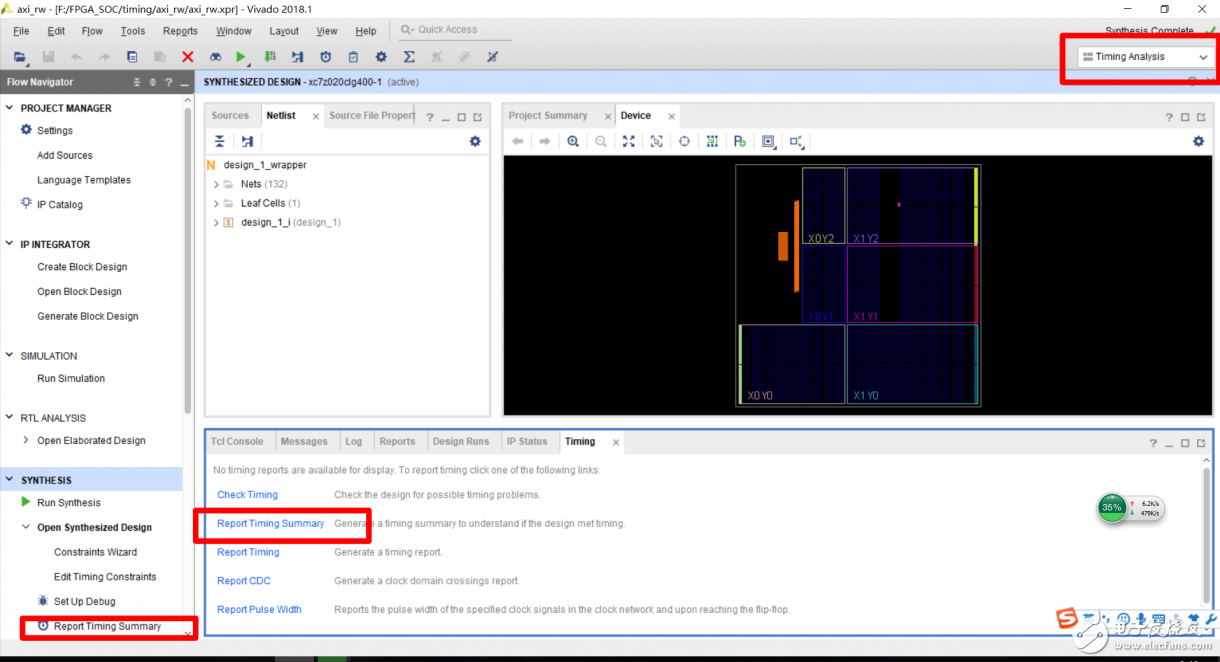

轉(zhuǎn)自:VIVADO時序分析練習時序分析在FPGA設(shè)計中是分析工程很重要的手段,時序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習VIVADO軟件時序分析的筆記,小編這里

2018-08-22 11:45:54

1、FPGA中的時序約束--從原理到實例 基本概念 建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。 電路中的建立時間和保持時間其實跟生活中的紅綠燈很像

2022-11-15 15:19:27

關(guān)于靜態(tài)分析和時序約束的文章

2014-07-17 12:12:35

設(shè)計的驗證平臺,以此來提高工作效率。論文介紹了FF-DX地址計算部件的時序建模和靜態(tài)時序分析方法。在靜態(tài)時序分析之后,將SDF文件中的延時信息反標到邏輯網(wǎng)表中,通過動態(tài)時序驗證進一步保證設(shè)計的時序收斂

2011-12-07 17:40:14

關(guān)于車載信息中心電路保護措施的介紹與分析

2021-05-14 07:12:04

關(guān)于時序邏輯等效性的RTL設(shè)計和驗證流程介紹。

2021-04-28 06:13:14

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

FPGA時序分析系統(tǒng)時序基礎(chǔ)理論對于系統(tǒng)設(shè)計工程師來說,時序問題在設(shè)計中是至關(guān)重要的,尤其是隨著時鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫窗口越來越小,要想在很短的時間限制里,讓數(shù)據(jù)信號從驅(qū)動端完整

2012-08-11 17:55:55

FPGA時序相關(guān)的資料。都看完看懂時序就沒問題了。分了三個附件:第一個是通過一些例子教你如何搞定時序分析。第二個附件是網(wǎng)上各種大神們對時序的理解,主要是他們的博客鏈接以及網(wǎng)站鏈接。第三個是其他的一些零散的關(guān)于時序的資料。

2012-11-12 17:45:28

FPGA中幾個基本的重要的時序分析參數(shù)介紹(fmax\tsu\th\tco\tpd)今天無聊,翻開書偶看到介紹時序部分的東西,覺得其中幾個參數(shù)縮寫所代表的含義應(yīng)該記住,故寫如下文章……FPGA中

2012-04-09 09:41:41

約束文件(XDC文件),它包含用于時序分析的“create_clock”和“set_input_jitter”約束。在ISE 14.7和Spartan-3 FPGA中,我可以使用稱為“時鐘向?qū)А钡腎P來

2019-08-02 09:54:40

本手冊通過一個示例工程,講解了使用 TD 和 Vivado 下時序約束的對比,詳細對比了時序約束的命令、時序約束結(jié)果的展示以及部分時序路徑。

2022-10-27 06:21:47

嗨,我們正在嘗試使用Vivado工具鏈手動路由FPGA,并想知道應(yīng)該使用什么工具來手動路由Virtex 7 FPGA。還可以在Vivado時序分析器工具中指定溫度和電壓值來估算設(shè)計時序嗎?我們將如

2018-10-25 15:20:50

`基于 FPAGxilinx vivado 仿真模式介紹本文介紹一下xilinx的開發(fā)軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。分別為:1. run

2018-01-24 11:06:12

FPGA外部的芯片,可能是FPGA內(nèi)部的硬核。對于FPGA design來說,必須要關(guān)注在指定要求下,它能否正常工作。這個正常工作包括同步時序電路的工作頻率,以及輸入輸出設(shè)備的時序要求。在FPGA

2019-07-09 09:14:48

靜態(tài)時序分析STA是什么?靜態(tài)時序分析STA的優(yōu)點以及缺點分別有哪些呢?

2021-11-02 07:51:00

關(guān)于多參數(shù)土壤分析儀的參數(shù)詳細介紹【云唐科器】土壤是植物生長的基礎(chǔ),養(yǎng)分含量決定了作物的產(chǎn)量和質(zhì)量。在農(nóng)業(yè)生產(chǎn)過程中,有必要做好土壤養(yǎng)分的檢測。傳統(tǒng)的測試方法

2021-03-15 16:29:36

Cadence高速PCB的時序分析:列位看觀,在上一次的連載中,我們介紹了什么是時序電路,時序分析的兩種分類(同步和異步),并講述了一些關(guān)于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的時序分析 1.引言 時序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發(fā)了一封 e-mail,希望能夠得到一份時序分析的案

2010-04-05 06:37:13 0

0 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎(chǔ)常用時序概念QuartusII中的時序分析報告

設(shè)置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 在討論時序邏輯電路的分析與設(shè)計之前,讓我們先回顧一下在第四章中介紹過的時序電路結(jié)構(gòu)框圖和一些相關(guān)術(shù)語。時序電路的結(jié)構(gòu)框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 跳變點是所有重要時序分析工具中的一個重要概念。跳變點被時序分析工具用來計算設(shè)計節(jié)點上的時延與過渡值。跳變點的有些不同含義可能會被時序分析工程師忽略。而這

2010-09-15 10:48:06 1461

1461

介紹了采用STA (靜態(tài)時序分析)對FPGA (現(xiàn)場可編程門陣列)設(shè)計進行時序驗證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 討論了靜態(tài)時序分析算法及其在IC 設(shè)計中的應(yīng)用。首先,文章討論了靜態(tài)時序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時的因素。最后通過一個完整的IC 設(shè)計

2011-12-20 11:03:16 95

95 DDR_SDRAM介紹和時序圖,DDR_SDRAM介紹和時序圖

2016-02-23 11:58:38 6

6 靜態(tài)時序分析基礎(chǔ)及應(yīng)用

2017-01-24 16:54:24 7

7 時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

高速數(shù)字電路互連時序模型與布線長度分析 高速電路設(shè)計領(lǐng)域,關(guān)于布線有一種幾乎是公理的認識,即等長走線,認為走線只要等長就一定滿足時序需求,就不會存在時序問題。本文對常用高速器件的互連時序建立模型

2017-10-15 10:24:53 1

1 過程必須以滿足XDC中的約束為目標來進行。那么: 如何驗證實現(xiàn)后的設(shè)計有沒有滿足時序要求? 如何在開始布局布線前判斷某些約束有沒有成功設(shè)置? 如何驗證約束的優(yōu)先級? 這些都需要用到Vivado中的靜態(tài)時序分析工具。

2017-11-17 18:03:55 34003

34003

時序分析基本概念介紹——STA概述,動態(tài)時序分析,主要是通過輸入向量作為激勵,來驗證整個設(shè)計的時序功能。動態(tài)時序分析的精確與否取決于輸入激勵的覆蓋率,它最大的缺點就是速度非常慢,通常百萬門的設(shè)計想全部覆蓋測試的話,時間就是按月來計算了。

2017-12-14 17:01:32 27851

27851

時序分析基本概念介紹——時序庫Lib。用于描述物理單元的時序和功耗信息的重要庫文件。lib庫是最基本的時序庫,通常文件很大,分為兩個部分。

2017-12-15 17:11:43 10427

10427

時序分析基本概念介紹——Timing Arc

2018-01-02 09:29:04 23487

23487

在實際工程中,如何利用好這一工具仍值得考究。本文將介紹使用Vivado HLS時的幾個誤區(qū)。

2018-01-10 14:33:02 19813

19813

本文介紹一下xilinx的開發(fā)軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。 分別為: 1. run behavioral simulation-----行為級仿真,行為

2018-05-29 13:46:52 7674

7674 來維持嗎? 1、Vivado基本操作流程 2、時序基本概念 3、時序基本約束和流程 4、Baselining時序約束 5、CDC時序約束 6、I/O時序 7、例外時序約束 8、時序收斂優(yōu)化技術(shù)

2018-08-06 15:08:02 400

400 今天我們要介紹的時序分析概念是ETM。全稱extracted timing model。這是在層次化設(shè)計中必須要使用的一個時序模型文件。由block owner產(chǎn)生,在頂層設(shè)計使用。

2018-09-24 19:30:00 16300

16300

平時用得可能比較少,是PT產(chǎn)生的一個spice信息文件,可以用來和HSPICE做correlation。我們平時使用PT做得是gate level的時序分析,如果想做transistor level的時序分析,那可以采用HSPICE做電路仿真。

2018-09-23 16:52:00 6170

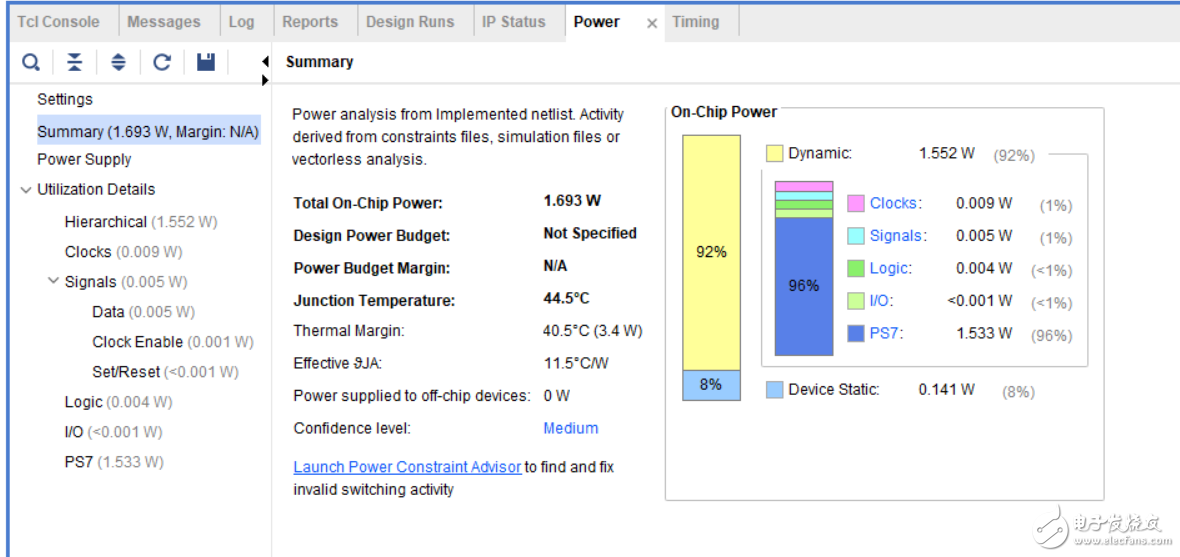

6170 了解Vivado設(shè)計套件中的一些廣泛的設(shè)計分析功能,旨在識別可能影響性能的設(shè)計中的問題區(qū)域。

2018-11-27 07:10:00 4613

4613 了解report_design_analysis,這是一個新的Vivado報告命令,可以獨特地了解時序和復(fù)雜性特征,這些特性對于分析時序收斂問題很有價值。

2018-11-26 07:01:00 3314

3314 今天我們要介紹的時序分析概念是Combinational logic. 中文名組合邏輯單元。這是邏輯單元的基本組成器件。比如我們常見的and, or, not, nand,nor等門電路。

2019-05-14 17:27:07 5391

5391

時序分析是以分析時間序列的發(fā)展過程、方向和趨勢,預(yù)測將來時域可能達到的目標的方法。此方法運用概率統(tǒng)計中時間序列分析原理和技術(shù),利用時序系統(tǒng)的數(shù)據(jù)相關(guān)性,建立相應(yīng)的數(shù)學模型,描述系統(tǒng)的時序狀態(tài),以預(yù)測未來。

2019-11-15 07:02:00 2570

2570

關(guān)于Vivado Dashboard的功能可閱讀這篇文章(Vivado 2018.3這個Gadget你用了嗎)Vivado 2019.1的Dashboard功能進一步增強。

2019-06-12 14:49:24 7677

7677

此次研討會為該系列的第一期,旨在深入剖析 Vivado 高速時序收斂技術(shù)。另外我們還將總結(jié)高速設(shè)計面臨的挑戰(zhàn),介紹設(shè)計分析、設(shè)計向?qū)?b class="flag-6" style="color: red">以及設(shè)計復(fù)雜性和擁塞的分析方法。

2019-07-31 17:54:28 2093

2093 交互式時鐘域的交叉分析:該功能支持設(shè)計人員在設(shè)計早期階段調(diào)試CDC問題。結(jié)合Vivado設(shè)計套件的交互式時序分析和交叉探測特性,CDC分析功能可提供強大的時序分析和調(diào)試功能,并加速產(chǎn)品上市進程。

2019-08-01 09:14:54 1862

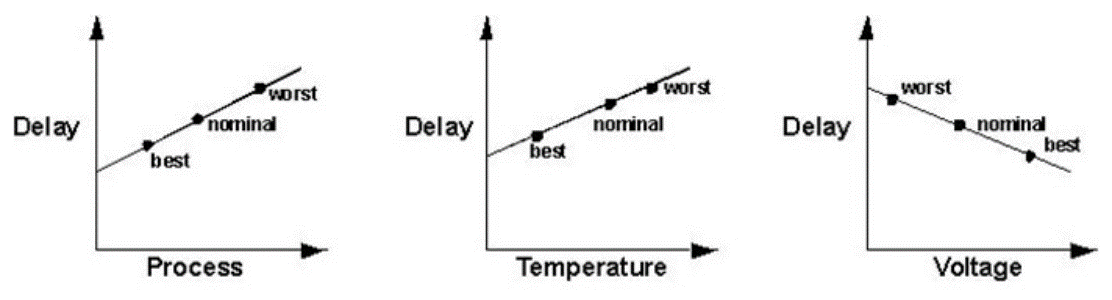

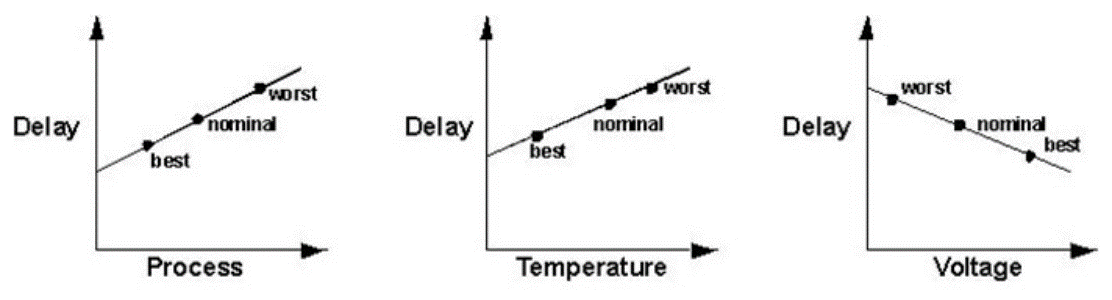

1862 即便是同一種FF,在同一個芯片上不同操作條件下的延時都不盡相同,我們稱這種現(xiàn)象為OCV(on-chip variation)。OCV表示的是芯片內(nèi)部的時序偏差,雖然很細小,但是也必須嚴格考慮到時序分析中去。

2019-07-25 11:22:30 4462

4462

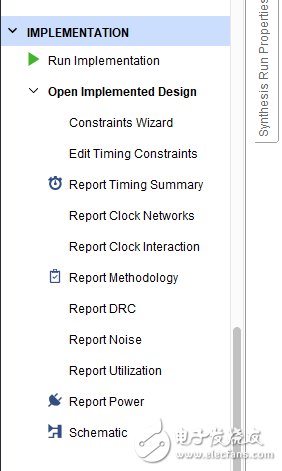

上面我們講的都是xdc文件的方式進行時序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進行時序約束:時序約束編輯器(Edit Timing Constraints )和時序約束向?qū)В–onstraints Wizard)。兩者都可以在綜合或?qū)崿F(xiàn)后的Design中打開。

2020-03-08 17:17:00 19067

19067

BY Hemang Divyakant Parikh 有多種類型的時序違例可歸類為脈沖寬度違例。 - 最大偏差違例(詳見 此處 ) - 最小周期違例(本文詳解之重點)。 - 最大周期違例

2020-11-19 13:48:45 4673

4673

1 I/O延遲約束介紹 要在設(shè)計中精確建模外部時序,必須為輸入和輸出端口提供時序信息。Xilinx Vivado集成設(shè)計環(huán)境(IDE)僅在FPGA邊界內(nèi)識別時序,因此必須使用以下命令指定超出這些邊界

2020-11-29 10:01:16 4315

4315 靜態(tài)時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態(tài)時序分析,靜態(tài)時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 本文檔的主要內(nèi)容詳細介紹的是華為FPGA硬件的靜態(tài)時序分析與邏輯設(shè)計包括了:靜態(tài)時序分析一概念與流程,靜態(tài)時序分析一時序路徑,靜態(tài)時序分析一分析工具

2020-12-21 17:10:54 18

18 時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文檔的主要內(nèi)容詳細介紹的是時序分析的靜態(tài)分析基礎(chǔ)教程。

2021-01-14 16:04:00 14

14 本文檔的主要內(nèi)容詳細介紹的是時序分析的Timequest教程免費下載。

2021-01-14 16:04:00 3

3 本文檔的主要內(nèi)容詳細介紹的是時序分析的Timequest教程免費下載。

2021-01-14 16:04:00 15

15 本文檔的主要內(nèi)容詳細介紹的是FPGA的時序分析的優(yōu)化策略詳細說明。

2021-01-14 16:03:59 17

17 本文檔的主要內(nèi)容詳細介紹的是FPGA的時序分析的優(yōu)化策略詳細說明。

2021-01-14 16:03:59 19

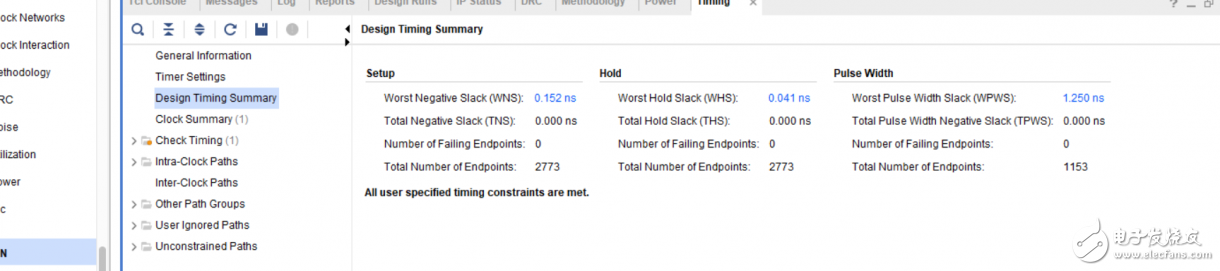

19 在Vivado中分析時序問題的原因(不在本篇中詳細討論), 并根據(jù)時序失敗的原因調(diào)整Vivado各個步驟的選項。有時我們也需要調(diào)整Vivad

2021-07-28 10:12:47 1758

1758

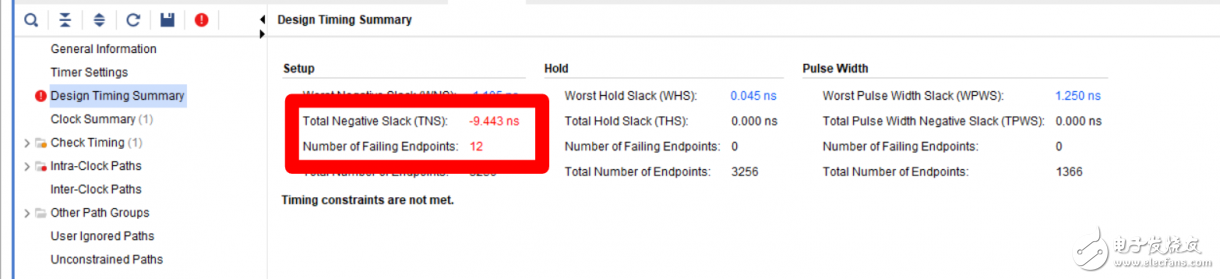

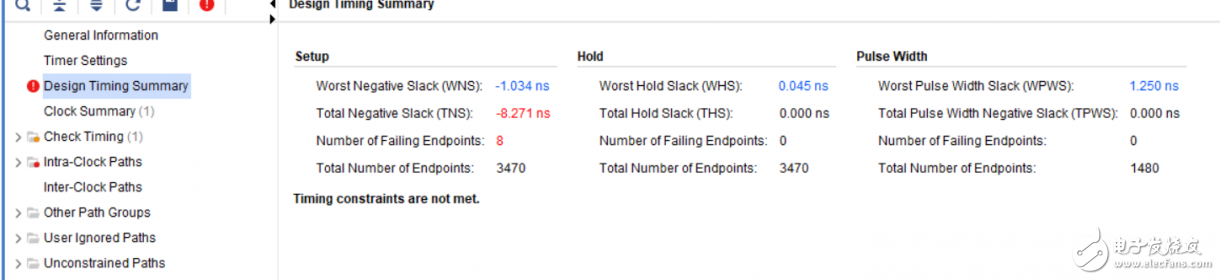

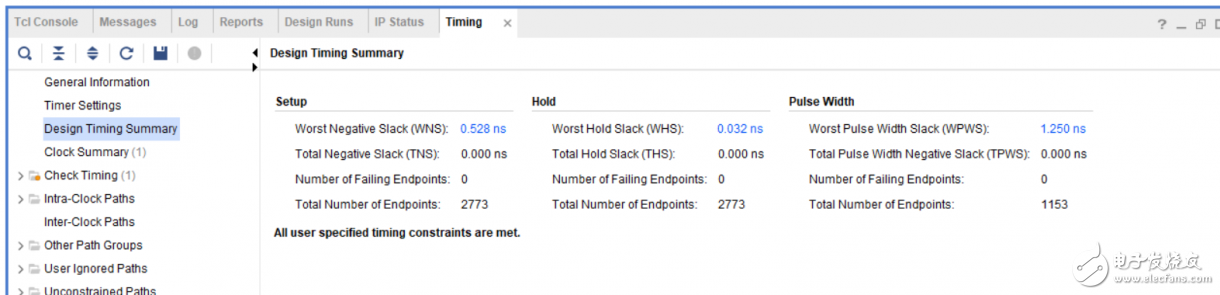

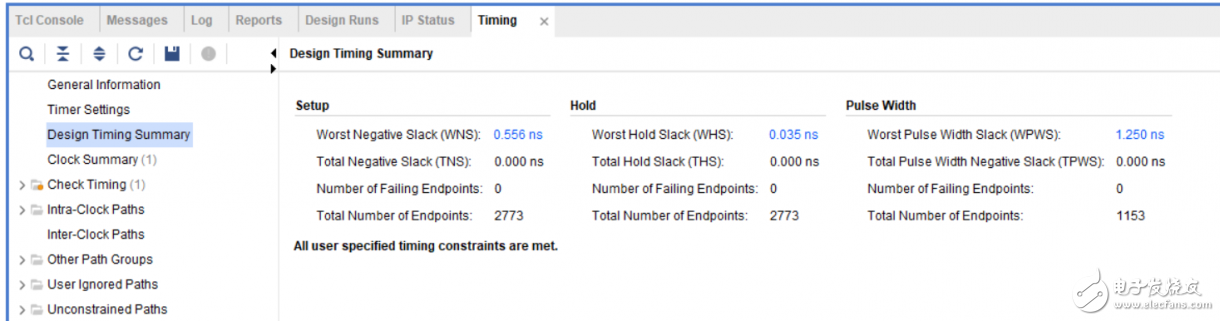

VIVADO中時序報告中WNS,WHS,TNS,THS含義運行“report_timing”或“report_timing_summary”命令后,會注意到 WNS、TNS、WHS 和 THS

2021-10-21 14:32:35 18650

18650

時序分析時FPGA設(shè)計中永恒的話題,也是FPGA開發(fā)人員設(shè)計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 關(guān)于紅外通信原理時序圖介紹,幫助單片機寫代碼程序

2022-06-26 09:25:11 0

0 要從時序分析刪除一組路徑,如果您確定這些路徑不會影響時序性能(False 路徑),可用FROM-TO 約束以及時序忽略 (TIG) 關(guān)鍵字。

2022-08-02 08:57:26 517

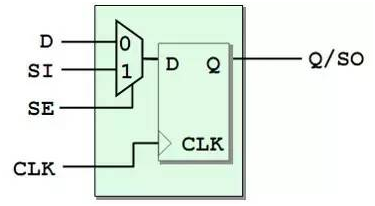

517 組合邏輯和時序邏輯電路是數(shù)字系統(tǒng)設(shè)計的奠基石,其中組合電路包括多路復(fù)用器、解復(fù)用器、編碼器、解碼器等,而時序電路包括鎖存器、觸發(fā)器、計數(shù)器、寄存器等。 在本文中,小編簡單介紹關(guān)于時序電路的類型和特點等相關(guān)內(nèi)容。

2022-09-12 16:44:00 7234

7234

前言 在上篇文章里《時序分析基本概念(一)——建立時間》,我們向大家介紹了建立時間的基本概念和計算方法。

2022-10-09 11:59:45 2696

2696 。在【時序分析的原理】章節(jié)中,我們介紹了很多原理性的東西,而在本章節(jié),我們將為大家介紹在解決具體問題時該如何向時序分析工具表述清楚我們的意圖,從而啟動其強大的邏輯錐求解功能來得出我們所關(guān)心的時序分析報告。

2022-12-28 15:18:38 1893

1893 對 FPGA 設(shè)計的實現(xiàn)過程必須以滿足 XDC 中的約束為目標進行。那我們?nèi)绾悟炞C實現(xiàn)后的設(shè)計有沒有滿足時序要求?又如何在開始布局布線前判斷某些約束有沒有成功設(shè)置?或是驗證約束的優(yōu)先級?這些都要用到 Vivado 中的靜態(tài)時序分析工具。

2023-05-04 11:20:31 2368

2368

前面幾篇文章已經(jīng)詳細介紹了FPGA時序約束基礎(chǔ)知識以及常用的時序約束命令,相信大家已經(jīng)基本掌握了時序約束的方法。

2023-06-23 17:44:00 1260

1260

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會提供時序報告,以方便開發(fā)者判斷自己的工程時序是否滿足時序要求。

2023-06-23 17:44:00 531

531

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向?qū)В–onstraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

FPGA開發(fā)過程中,vivado和quartus等開發(fā)軟件都會提供時序報告,以方便開發(fā)者判斷自己的工程時序是否滿足時序要求。

2023-06-26 15:29:05 531

531

向量和動態(tài)仿真 。本文將介紹靜態(tài)時序分析的基本概念和方法,包括時序約束,時序路徑,時序裕量,setup檢查和hold檢查等。 時序路徑 同步電路設(shè)計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最

2023-06-28 09:38:57 714

714

今天要介紹的時序分析基本概念是lookup table。中文全稱時序查找表。

2023-07-03 14:30:34 667

667

今天我們要介紹的時序分析概念是 **min pulse width** ,全稱為最小脈沖寬度檢查。這也是一種非常重要的timing arc check,經(jīng)常用在時序器件或者memory上面。

2023-07-03 14:54:11 1198

1198

今天我們要介紹的時序分析概念是clock gate。 clock gate cell是用data signal控制clock信號的cell,它被頻繁地用在多周期的時鐘path,可以節(jié)省功耗。

2023-07-03 15:06:03 1484

1484

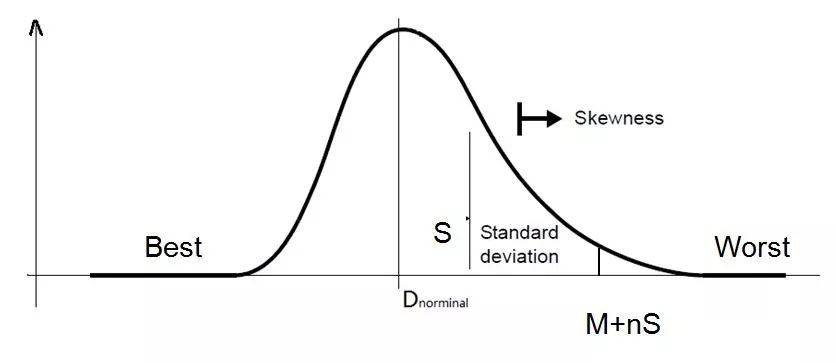

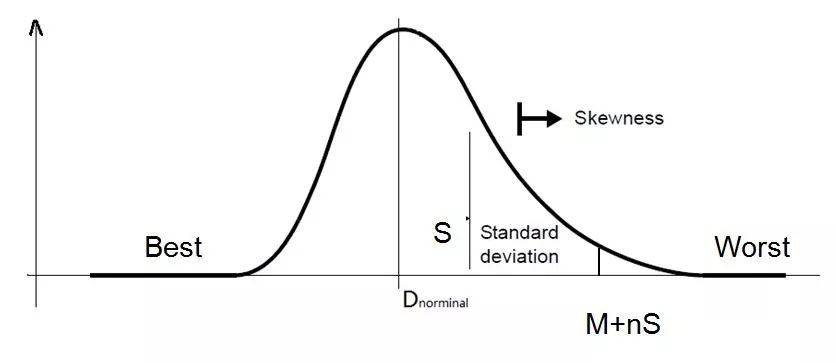

今天我們介紹的時序分析概念是 **SOCV** 。也被叫作POCV,全稱為 **Statistic OCV** . 這是一種比AOCV更加先進的分析模式。

2023-07-03 15:19:00 1347

1347

今天我們要介紹的時序分析概念是 **AOCV** 。全稱Stage Based Advanced OCV。我們知道,在OCV分析過程中,我們會給data path,clock path上設(shè)定單一的timing derate值。

2023-07-03 16:29:05 1164

1164

??本文主要介紹了靜態(tài)時序分析 STA。

2023-07-04 14:40:06 528

528

今天我們要介紹的時序分析基本概念是MMMC分析(MCMM)。全稱是multi-mode, multi-corner, 多模式多端角分析模式。這是在先進工藝下必須要使用的一種時序分析模式。

2023-07-04 15:40:13 1461

1461

今天要介紹的時序分析基本概念是skew,我們稱為偏差。

2023-07-05 10:29:37 2120

2120

今天要介紹的時序分析基本概念是Slew,信號轉(zhuǎn)換時間,也被稱為transition time。

2023-07-05 14:50:53 1530

1530

今天我們要介紹的時序分析概念是 **時序路徑** (Timing Path)。STA軟件是基于timing path來分析timing的。

2023-07-05 14:54:43 985

985

今天我們要介紹的時序基本概念是Timing arc,中文名時序弧。這是timing計算最基本的組成元素,在昨天的lib庫介紹中,大部分時序信息都以Timing arc呈現(xiàn)。

2023-07-06 15:00:02 1397

1397

今天主要介紹的時序概念是時序庫lib,全稱liberty library format(以? lib結(jié)尾),

2023-07-07 17:15:00 1645

1645

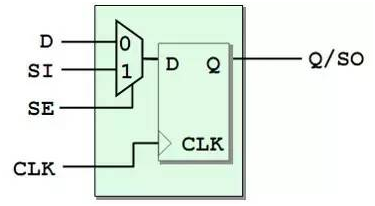

今天要介紹的時序基本概念是Mode(模式). 這是Multiple Scenario環(huán)境下Sign off的一個重要概念。芯片的設(shè)計模式包括最基本的功能function模式,以及各種各樣相關(guān)的測試模式。

2023-07-10 17:21:38 1721

1721

本文詳細介紹了vivado軟件和modelsim軟件的安裝,以及vivado中配置modelsim仿真設(shè)置,每一步都加文字說明和圖片。

2023-08-07 15:48:00 1478

1478

有些時候在寫完代碼之后呢,Vivado時序報紅,Timing一欄有很多時序問題。

2024-01-05 10:18:36 291

291

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論