基于FPGA和DDS的信號(hào)源設(shè)計(jì)

1 引言

直接數(shù)字頻率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽樣定理理論和現(xiàn)代器件生產(chǎn)技術(shù)發(fā)展的一種新的頻率合成技

2010-02-21 09:15:21 1833

1833

一般的雷達(dá)信號(hào)源實(shí)現(xiàn)主要有三種方式:第一種方式是采用DDS和MCU控制器件結(jié)合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結(jié)合的方式:第三種是由FPGA等可編程器件實(shí)現(xiàn)DDS的方式。第一種方式利用專用DDS器件可以產(chǎn)生具有較好的雜散抑制和諧波抑制性能的雷達(dá)波形。

2020-07-27 08:50:28 3381

3381

使用AD9833信號(hào)發(fā)生芯片可以產(chǎn)生0~12.5Mhz的信號(hào),包括有正弦波、三角波以及方波。利用其中的諧波,可以直接產(chǎn)生調(diào)頻廣播接收范圍內(nèi)的調(diào)頻信號(hào)。 中國調(diào)頻廣播所占的頻率范圍:87.5

2021-01-01 09:42:00 2635

2635 一般的雷達(dá)信號(hào)源實(shí)現(xiàn)主要有三種方式:第一種方式是采用DDS和MCU控制器件結(jié)合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結(jié)合的方式:第三種是由FPGA等可編程器件實(shí)現(xiàn)DDS的方式。第一種方式利用專用DDS器件可以產(chǎn)生具有較好的雜散抑制和諧波抑制性能的雷達(dá)波形。

2020-12-01 10:13:20 1323

1323

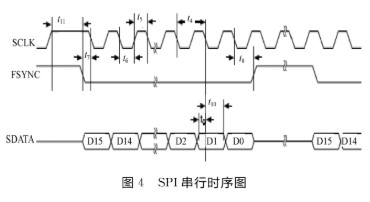

很多時(shí)候我們需要輸出某種函數(shù)信號(hào),如方波、三角波、正弦波等,但想要獲得這樣的函數(shù)信號(hào),不論是硬件電路還是軟件實(shí)現(xiàn),卻并不是一件簡(jiǎn)單的事情。不過AD9833這類函數(shù)生成芯片可以簡(jiǎn)化這方面的操作,這一節(jié)我們就來設(shè)計(jì)并實(shí)現(xiàn)AD9833的驅(qū)動(dòng)。

2022-12-09 15:50:27 4434

4434

1. 該模塊是購置于淘寶 GY9833: Price: 6.85。 AD9833購買模塊以及測(cè)試實(shí)驗(yàn) 2. 測(cè)試實(shí)驗(yàn)板 (1) Hardware AltiumDesign\Test\2020

2020-12-04 16:29:09 4844

4844 FPGA(現(xiàn)場(chǎng)可編程門陣列)作為信號(hào)源的主要平臺(tái),利用DDFS技術(shù)產(chǎn)生一個(gè)按指數(shù)衰減的頻率可調(diào)正弦衰減信號(hào)。

2019-06-24 06:18:55

基于STM32F103RCT6的AD9833驅(qū)動(dòng)開發(fā)(代碼可以免費(fèi)發(fā)郵箱)AD9833手冊(cè)分析管腳定義:手冊(cè)就先講到這里,不明白的歡迎評(píng)論區(qū)留言,另外我會(huì)把代碼還有手冊(cè)一并發(fā)送給感興趣的朋友

2021-08-24 07:54:20

內(nèi)容是關(guān)于DDS信號(hào)發(fā)生器芯片AD9833的最小原理圖

2020-02-21 17:18:28

。這是加了負(fù)載后,AD9833輸出的波形,波形不穩(wěn)定,幅值減小且頻率變?yōu)?MHZ這是負(fù)載電路中一級(jí)放大的輸出信號(hào)波形,不穩(wěn)定且不滿足設(shè)計(jì)的放大倍數(shù)這是負(fù)載電路2級(jí)放大后輸出信號(hào)波形,波形穩(wěn)定,頻率為

2013-11-26 15:03:26

利用STM32控制AD9833,生成10KHz正弦波,實(shí)驗(yàn)中發(fā)現(xiàn),輸出的正弦信號(hào)存在一個(gè)很大的偏置電壓,約為0.37V,輸出信號(hào)幅值為0.6Vpp,實(shí)際操作中利用相同code分別下載了兩個(gè)

2023-12-08 07:40:25

1.FPGA-現(xiàn)場(chǎng)可編程門陣列 每一塊FPGA芯片都是由有限多個(gè)帶有可編程連接的預(yù)定義源組成來實(shí)現(xiàn)一種可重構(gòu)數(shù)字電路。 圖1.FPGA不同構(gòu)成 FPGA芯片說明書中,包含了可編程邏輯模...

2021-07-30 07:23:42

CPLD是什么?FPGA包含哪幾類可編程資源呢?FPGA可編程器件和CPLD可編程器件有哪些相同點(diǎn)和不同點(diǎn)?

2021-11-10 07:42:51

是今天FPGA(現(xiàn)場(chǎng)可編程門陣列)流的混合信號(hào)版。可配置模擬IC已經(jīng)出現(xiàn)了多年,表面看來對(duì)市場(chǎng)的影響不及其數(shù)字同胞FPGA(現(xiàn)場(chǎng)可編程門陣列)。不過,當(dāng)前的經(jīng)濟(jì)形勢(shì)卻使可編程模擬標(biāo)準(zhǔn)產(chǎn)品的概念突然顯現(xiàn)出

2019-07-05 07:51:19

25年前,賽靈思(Xilinx)公司發(fā)明了FPGA(現(xiàn)場(chǎng)可編程門陣列)。如今,以FPGA為代表的可編程芯片應(yīng)用已經(jīng)成為勢(shì)不可擋的發(fā)展趨勢(shì),尤其在ASSP和傳統(tǒng)ASIC之間出現(xiàn)的市場(chǎng)缺口上,FPGA將開辟出新的領(lǐng)域,而目前席卷全球的金融危機(jī)更是成為FPGA迅速發(fā)展的催化劑。

2019-07-25 08:05:19

高性能直接數(shù)字合成DDS(Direct DigitalSynthesis)技術(shù)、數(shù)字信號(hào)處理DSP(Digital Signal Processing)技術(shù)及大規(guī)模可編程邏輯器件技術(shù)和電子計(jì)算機(jī)

2021-04-06 08:57:59

:GPIO5[4]、GPIO5[6]和GPIO5[9]。

波形發(fā)生器

TL6748-PlusTEB實(shí)驗(yàn)箱采用板載波形信號(hào)發(fā)生器,波形信號(hào)發(fā)生器采用的芯片是AD9833。

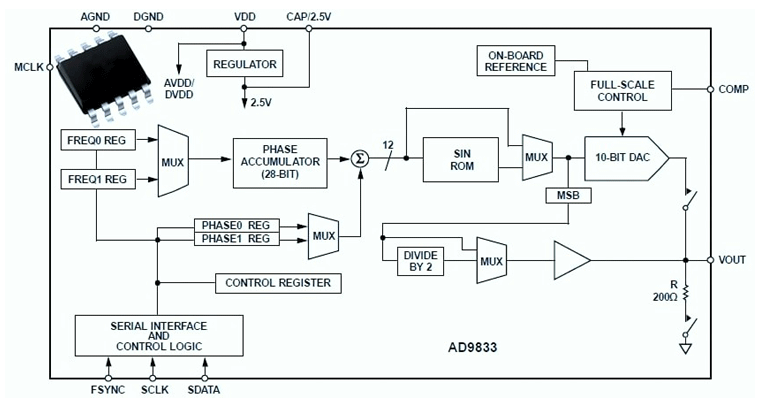

AD9833是一款低功耗、可編程

2024-02-21 14:28:07

S9227如何實(shí)現(xiàn)可編程控制需要加上什么樣子的轉(zhuǎn)換電路以及轉(zhuǎn)換電路接到什么樣子的可編程芯片能連接到LED數(shù)碼管上,求大神詳解并給出相應(yīng)電路圖

2019-06-14 15:26:35

發(fā)生器。函數(shù)信號(hào)發(fā)生器的實(shí)現(xiàn)方法通常是采用分立元件或單片專用集成芯片,但其頻率不高,穩(wěn)定性較差,且不易調(diào)試,開發(fā)和使用上都受到較大限制。隨著可編程邏輯器件(FPGA)的不斷發(fā)展,直接頻率合成(DDS)技術(shù)

2012-05-12 23:01:54

都應(yīng)該知道... 2、方案闡述(歡迎網(wǎng)友給予指點(diǎn))AD9833作為一個(gè)可編程波形發(fā)生器件,作為一個(gè)編程初學(xué)者我就把這個(gè)器件大材小用來實(shí)現(xiàn)信號(hào)發(fā)生功能。AD9833的控制和數(shù)據(jù)信息就由51單片機(jī)提供,再加上

2014-07-01 18:26:42

可編程邏輯器件市場(chǎng)約為35億美元。固定邏輯器件市場(chǎng)約為120億美元。然而,近年來,PLD銷售額的增長速度已經(jīng)超過基于傳統(tǒng)門陣列技術(shù)的固定邏輯器件的銷售增長速度。而且,高性能FPGA現(xiàn)在已開始從采用最先

2009-05-29 11:36:21

使用51驅(qū)動(dòng)AD9833模塊的使用關(guān)于AD9833相關(guān)參數(shù)程序流程代碼片上傳程序總結(jié)關(guān)于AD9833AD9833是一款低功耗、可編程波形發(fā)生器,能夠產(chǎn)生正弦波、三角波和方波輸出。各種類型的檢測(cè)、信號(hào)

2021-12-01 07:53:11

利用STM32控制AD9833,生成10KHz正弦波,實(shí)驗(yàn)中發(fā)現(xiàn),輸出的正弦信號(hào)存在一個(gè)很大的偏置電壓,約為0.37V,輸出信號(hào)幅值為0.6Vpp,實(shí)際操作中利用相同code分別下載了兩個(gè)

2018-11-26 09:17:00

【作者】:張雅珍;魏榕山;【來源】:《中國儀器儀表》2010年03期【摘要】:采用DDS芯片AD9833為信號(hào)產(chǎn)生芯片,AVR單片機(jī)ATMega16L為控制器,配合外圍I/O器件,設(shè)計(jì)了一種結(jié)構(gòu)簡(jiǎn)便

2010-04-24 08:59:31

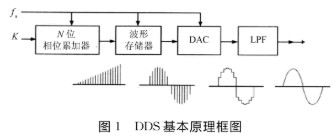

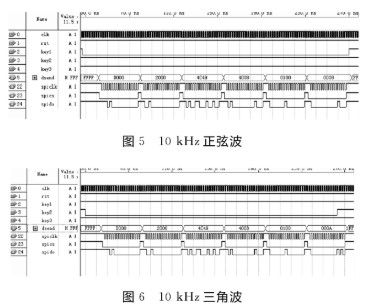

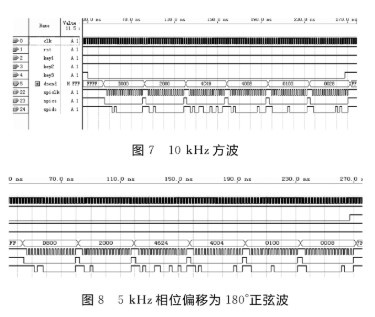

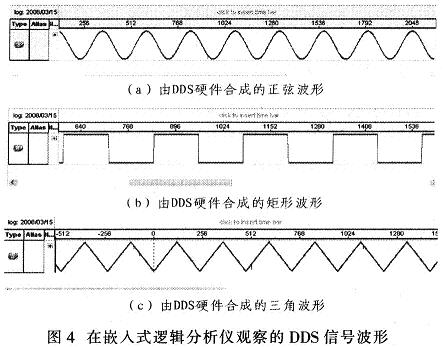

),它采用數(shù)字電路合成所需波形,具有精度高、產(chǎn)生信號(hào)信噪性能好、頻率分辨率高、轉(zhuǎn)換速度快等優(yōu)點(diǎn)。本文設(shè)計(jì)的掃頻信號(hào)源是基于DDS技術(shù),并在Altera公司的EP2C20上實(shí)現(xiàn)邏輯綜合、布局布線、時(shí)序

2019-07-04 07:42:59

在電子信息領(lǐng)域,函數(shù)發(fā)生器(信號(hào)源)是通用的設(shè)備。近年來電子信息技術(shù)的飛速發(fā)展,使得各領(lǐng)域?qū)?b class="flag-6" style="color: red">信號(hào)源的要求在不斷提高。不但要求其頻率穩(wěn)定度和準(zhǔn)確度高,要求頻率改變的方便性,而且還要求可以產(chǎn)生任意波形

2019-11-04 08:00:46

性能好,規(guī)模大,可重復(fù)編程,開發(fā)投資小等優(yōu)點(diǎn)。隨著微電子技術(shù)的發(fā)展,FPGA的成本不斷下降,正逐漸成為各種電子產(chǎn)品不可或缺的重要部件。由于FPGA有著如此眾多的優(yōu)點(diǎn),因此系統(tǒng)采用FPGA作為控制芯片,實(shí)現(xiàn)可編程電壓源系統(tǒng),為需要可調(diào)電壓源的電子產(chǎn)品提供高精度、高可靠性的電壓。但是,誰知道我們具體該怎么做嗎?

2019-08-07 08:03:09

介紹了利用現(xiàn)場(chǎng)可編程邏輯門陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)方法,給出了采用ALTERA公司的ACEX系列FPGA芯片EP1K30TC進(jìn)行直接數(shù)字頻率合成的VHDL源程序。

2021-04-30 06:29:00

可編程電源指某些功能或參數(shù)可以通過計(jì)算機(jī)軟件編程進(jìn)行控制的電源。可編程電源的實(shí)現(xiàn)方法有很多種。其中,現(xiàn)場(chǎng)可編程門陣列(Field ProgrammableGate Array,FPGA)具有性能好,規(guī)模大,可重復(fù)編程,開發(fā)投資小等優(yōu)點(diǎn)。

2019-11-04 06:26:07

請(qǐng)問如何設(shè)計(jì)并制作一種高速雙路可編程信號(hào)源?

2021-04-22 07:03:12

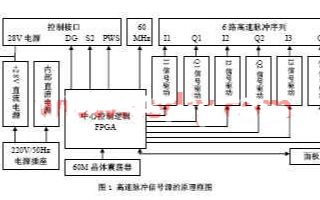

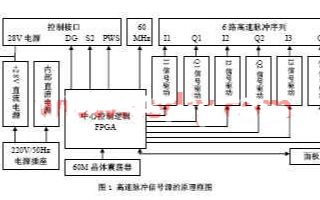

本文設(shè)計(jì)了一種以FPGA、高速D/A為核心,能產(chǎn)生多路頻率可調(diào)信號(hào)的信號(hào)源系統(tǒng)。

2021-05-08 09:12:14

Virtex系列FPGA性能是什么?基于Virtex系列FPGA的可編程嵌入式信號(hào)處理背板的設(shè)計(jì)

2021-05-08 06:39:32

性能好,規(guī)模大,可重復(fù)編程,開發(fā)投資小等優(yōu)點(diǎn)。隨著微電子技術(shù)的發(fā)展,FPGA的成本不斷下降,正逐漸成為各種電子產(chǎn)品不可或缺的重要部件。由于FPGA有著如此眾多的優(yōu)點(diǎn),因此系統(tǒng)采用FPGA作為控制芯片,實(shí)現(xiàn)可編程電壓源系統(tǒng),為需要可調(diào)電壓源的電子產(chǎn)品提供高精度、高可靠性的電壓。

2019-08-19 06:54:51

本設(shè)計(jì)就是采用Lattice公司的高密度在系統(tǒng)可編程芯片pLSI/ispLSI1016設(shè)計(jì)的一個(gè)通信數(shù)字信號(hào)源?設(shè)計(jì)中采用兩套地址總線(微機(jī)總線與isp總線)分時(shí)對(duì)兩片RAM進(jìn)行讀寫操作,并采用不斷查詢端口的方式進(jìn)行協(xié)調(diào)控制,從而產(chǎn)生出滿足設(shè)計(jì)要求的數(shù)字碼流?

2021-04-30 06:09:11

本文提出一種利用復(fù)雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)設(shè)計(jì)技術(shù)[3]實(shí)現(xiàn)專用鍵盤接口芯片的方案。

2021-04-15 06:55:36

本文針對(duì)遙測(cè)應(yīng)用,以大容量FPGA器件為核心,實(shí)現(xiàn)了電源獨(dú)立的不同頻率、不同波形的多路模擬量信號(hào)源。

2021-04-30 06:12:38

想在protues中仿真波形發(fā)生器,但是沒有AD9833的模型,請(qǐng)問哪位大神有AD9833元件庫或者提供一下可代替芯片。

2014-04-29 09:15:01

現(xiàn)場(chǎng)可編程門陣列(FPGA)是一種可編程邏輯器件,由成千上萬個(gè)完全相同的可編程邏輯單元組成,周圍是輸入/輸出單元構(gòu)成的外設(shè)。制造完成后,FPGA可以在工作現(xiàn)場(chǎng)編程,以便實(shí)現(xiàn)特定的設(shè)計(jì)功能。典型設(shè)計(jì)工

2019-08-06 08:27:36

之前用的是AD9833,但是最高耐溫是105℃。現(xiàn)在想找一個(gè)耐溫125℃的,找了AD9833-EP,AD9837兩個(gè),和AD9833引腳一樣的,現(xiàn)在想問的就是AD9833-EP,AD9837和AD9833除了耐溫還有什么不同嗎?選擇哪個(gè)作為替換比較好呢?

2018-08-18 06:00:04

請(qǐng)問哪位大俠有AD9833/4用DSP進(jìn)行編程輸出正弦或方波?初來匝道,請(qǐng)多關(guān)照,不勝感謝

2019-03-15 16:41:35

文中介紹一種基于DDFS(直接頻率合成)技術(shù)的可編程音頻儀器測(cè)試信號(hào)源設(shè)計(jì)。

2021-05-10 06:05:17

最近調(diào)試AD9833的時(shí)候遇到個(gè)問題,請(qǐng)教一下大家。

目前用AD9833發(fā)生正弦波信號(hào),基本電路就是AD9833+運(yùn)放跟隨,可以得到想要的頻率,比如我設(shè)置的20kHz,示波器上可以看到20kHz信號(hào)。但是這個(gè)正弦信號(hào)上有一個(gè)低頻的周期信號(hào),頻率大概是零點(diǎn)幾Hz,很奇怪,不知道這個(gè)低頻信號(hào)怎么來的。

2023-12-06 08:18:36

一般的雷達(dá)信號(hào)源實(shí)現(xiàn)主要有三種方式:第一種方式是采用DDS和MCU控制器件結(jié)合的方式;第二種是DDS、MCU控制器件和FPGA等可編程器件結(jié)合的方式:第三種是由FPGA等可編程器件實(shí)現(xiàn)DDS的方式

2020-11-24 06:39:52

提出了一種基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的全球定位系統(tǒng)(GPS)衛(wèi)星信號(hào)模擬源系統(tǒng)的設(shè)計(jì)方案。FPGA作為一種常用的可編程器件,將其應(yīng)用到模擬信號(hào)源系統(tǒng)中,并配合射頻模塊,實(shí)現(xiàn)

2009-05-26 20:40:01 33

33 基于AD9833的高精度可編程波形發(fā)生器系統(tǒng)設(shè)計(jì):介紹一種基于AD9833的高精度可編程波形發(fā)生器系統(tǒng)解決方案,該系統(tǒng)具有可編程設(shè)置、波形頻率和峰峰值等功能,從而解決DDS輸出波

2009-05-26 23:37:57 149

149 針對(duì)我國工業(yè)自動(dòng)化儀表行業(yè)普遍應(yīng)用的各種信號(hào)輸出制的儀表,設(shè)計(jì)出儀用標(biāo)準(zhǔn)直流信號(hào)源。它可以為各種信號(hào)制儀表的校對(duì)提供標(biāo)準(zhǔn)信號(hào)源。本儀用標(biāo)準(zhǔn)直流信號(hào)源具有輸出精

2009-09-02 17:50:37 26

26 本設(shè)計(jì)就是采用Lattice公司的高密度在系統(tǒng)可編程芯片pLSI/is p LS I016設(shè)計(jì)的一個(gè)通信數(shù)字信號(hào)源。設(shè)計(jì)中采用兩套地址總線( 微機(jī)總線與i s p

2009-11-27 11:15:23 18

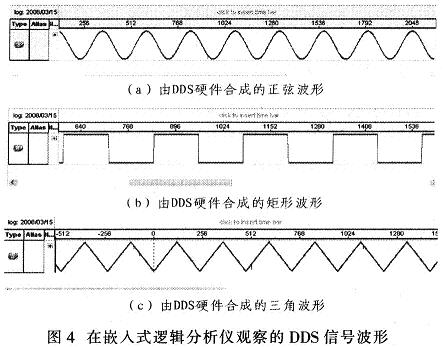

18 基于FPGA的DDS信號(hào)源設(shè)計(jì)與實(shí)現(xiàn)

利用DDS和 FPGA 技術(shù)設(shè)計(jì)一種信號(hào)發(fā)生器.介紹了該信號(hào)發(fā)生器的工作原理、 設(shè)計(jì)思路及實(shí)現(xiàn)方法.在 FPGA 器件上實(shí)現(xiàn)了基于 DDS技

2010-02-11 08:48:05 223

223 本文設(shè)計(jì)了一種基于DDS芯片AD9833的高性能正弦掃頻式恒流源。正弦波信號(hào)源采用了新型DDS芯片AD9833,并利用濾波芯片LTC1560-1進(jìn)行低通濾波;V/I轉(zhuǎn)換電路采用了改進(jìn)型Howland電流泵,從

2010-08-03 15:45:05 195

195 在AD9833的模擬輸出是fMCLK/228 x FREQREG其中FREQREG是頻率選擇寄存器的值裝入。該信號(hào)將逐步轉(zhuǎn)移登記由2π/4096x PHASEREG在PHASEREG選擇階段是值

2010-08-20 15:50:24 165

165 【摘 要】 利用DSP和CPLD來設(shè)計(jì)寬帶信號(hào)源,將DSP軟件控制上的靈活性和CPLD硬件上的高速、高集成度和可編程性有機(jī)地結(jié)合起來,一方面使得信號(hào)源控制簡(jiǎn)單、可靠,同時(shí)保證產(chǎn)生

2009-05-16 19:06:01 1031

1031

摘要:采用Lattice公司的在系統(tǒng)可編程器件pLSI/ispLSI1016,設(shè)計(jì)出一個(gè)具有可變格式、可變長度和可變速率的通信數(shù)字信號(hào)源,從而可以產(chǎn)生出符

2009-06-20 14:00:21 547

547

基于DDS芯片AD9833的音源發(fā)生器設(shè)計(jì)

在 2008年浙江省大學(xué)生電子設(shè)計(jì)競(jìng)賽中,有一個(gè)題目是“音樂演奏器設(shè)計(jì)”,要求用12個(gè)鍵盤演奏音樂,其中有一個(gè)關(guān)于音階的技術(shù)指標(biāo)

2009-11-03 09:01:15 1946

1946

基于并口通訊的雙路高速可編程數(shù)字及模擬信號(hào)源設(shè)計(jì)

應(yīng)用EPP模式的并口通訊實(shí)現(xiàn)了一種可同時(shí)輸出數(shù)字和模擬信號(hào)的雙路可編程信號(hào)源;使用一片C

2009-12-08 14:31:54 952

952

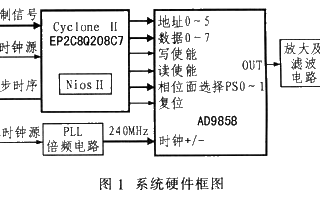

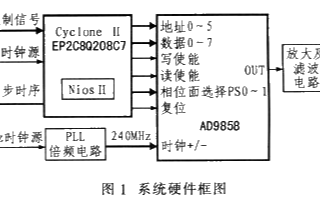

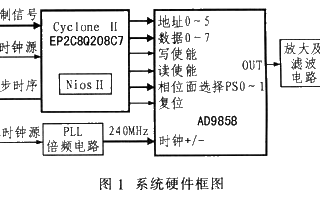

基于CycloneII系列FPGA的DDFS信號(hào)源實(shí)現(xiàn)

0 引言

在電子信息領(lǐng)域,函數(shù)發(fā)生器(信號(hào)源)是通用的設(shè)備。近年來電子信息技術(shù)的飛速發(fā)展,使得各領(lǐng)域?qū)?b class="flag-6" style="color: red">信號(hào)源的要

2009-12-14 11:16:51 1224

1224

AD9833型高精度可編程波形發(fā)生器設(shè)計(jì)方案

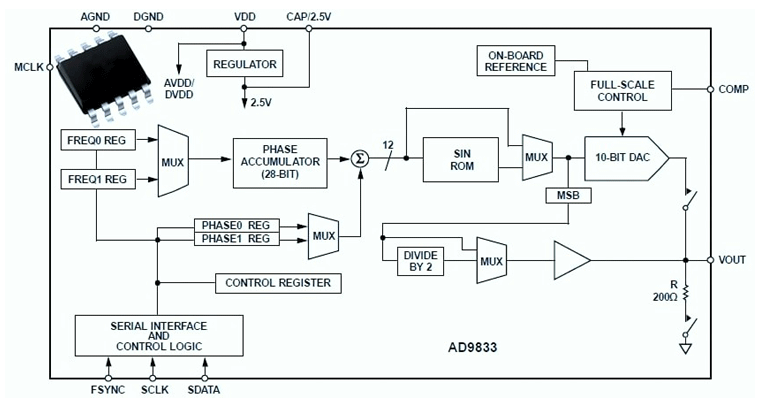

AD9833是ADI公司生產(chǎn)的一款低功耗,可編程波形發(fā)生器,能夠產(chǎn)生正弦波、三角波、方波輸出。波形發(fā)生器廣

2010-02-26 14:37:13 5751

5751

采用FPGA的可編程電壓源系統(tǒng)原理及設(shè)計(jì)計(jì)

概述:介紹一種基于FPGA的可編程電壓源系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)。采用FPGA為控制芯片,應(yīng)用Quartus

2010-03-22 14:31:44 2096

2096

采用Silicon公司C8051F340微處理器芯片,控制直接數(shù)字頻率合成芯片AD9858輸出模擬雷達(dá)信號(hào)。文中說明了電路設(shè)計(jì)結(jié)構(gòu)和軟件設(shè)計(jì)方法,并對(duì)信號(hào)源的性能進(jìn)行了可行性驗(yàn)證。

2011-10-19 15:07:25 44

44 運(yùn)用DDS技術(shù)實(shí)現(xiàn)傳輸速率可變的LVDS信號(hào),并使用LabView圖形編程工具,實(shí)現(xiàn)了數(shù)字信號(hào)源的交互界面,可以產(chǎn)生由上位機(jī)程控信號(hào)傳輸速率和數(shù)據(jù)內(nèi)容可變的LVDS信號(hào)。

2011-12-16 14:33:16 65

65 雷達(dá)信號(hào)源的設(shè)計(jì)在雷達(dá)測(cè)試中有著非常重要的作用。FPGA具有集成度高、通用性好、設(shè)計(jì)靈活、編程方便等諸多優(yōu)點(diǎn),因此采用AD9854和FPGA來設(shè)計(jì)雷達(dá)信號(hào)源。

2012-02-10 09:58:08 2148

2148

該信號(hào)源可輸出正弦波、方波和三角波,輸出信號(hào)的頻率以數(shù)控方式調(diào)節(jié),幅度連續(xù)可調(diào)。與傳統(tǒng)信號(hào)源相比,該信號(hào)源具有波形質(zhì)量好、精度高、設(shè)計(jì)方案簡(jiǎn)潔、易于實(shí)現(xiàn)、便于擴(kuò)展與維

2012-03-23 11:05:53 197

197 現(xiàn)場(chǎng)可編程邏輯陣列器件(FPGA)具有編程方便、高集成度、高可靠性等優(yōu)點(diǎn)。為了滿足科研和實(shí)際測(cè)試要求,本文設(shè)計(jì)了一種以FPGA、高速D/A為核心,能產(chǎn)生多路頻率可調(diào)信號(hào)的信號(hào)源系

2012-05-23 11:32:49 1195

1195

以16 位高精度D/A轉(zhuǎn)換器為核心構(gòu)建波形重構(gòu)電路,將單片機(jī)和FPGA 組合實(shí)現(xiàn)總體控制,完成了基于FPGA的實(shí)時(shí)可編程高精度信號(hào)源設(shè)計(jì)。利用單片機(jī)集成的16 位高精度A/D 構(gòu)建了一個(gè)閉

2012-05-28 10:06:08 930

930

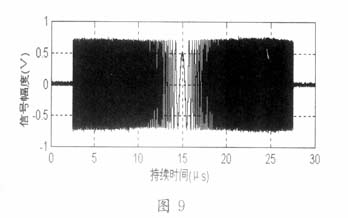

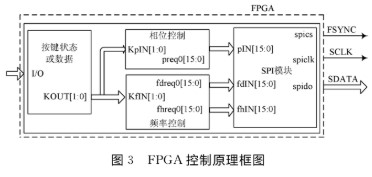

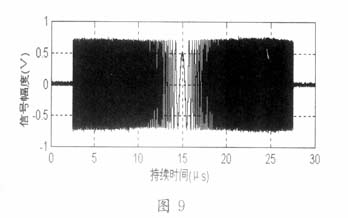

文中介紹一種基于DDFS(直接頻率合成)技術(shù)的可編程音頻儀器測(cè)試信號(hào)源設(shè)計(jì)。該系統(tǒng)采用單片機(jī)作為控制器,以FPGA(現(xiàn)場(chǎng)可編程門陣列)作為信號(hào)源的主要平臺(tái),利用DDFS技術(shù)產(chǎn)生一

2013-05-06 11:40:23 23

23 AD9833型高精度可編程波形發(fā)生器及其應(yīng)用。

2016-01-22 14:42:31 0

0 自己動(dòng)手設(shè)計(jì)信號(hào)發(fā)生器,AD9833能很好的輸出各種波形。

2016-02-29 15:08:16 0

0 基于FPGA的DDS信號(hào)源研究與設(shè)計(jì)_南楠.pdf 關(guān)于干擾的,不知道。

2016-05-16 17:15:25 4

4 多路同步數(shù)字調(diào)相信號(hào)源一般采用單片機(jī)和多片專用DDS芯片配合實(shí)現(xiàn)。該技術(shù)同步實(shí)現(xiàn)復(fù)雜,成本高。給出了一種基于FPGA的多路同步信號(hào)源的設(shè)計(jì)方法,通過VHDL語言硬件編程實(shí)現(xiàn)了基于單片FPGA

2016-05-27 13:47:49 7436

7436

The AD9833 is a low power, programmable waveform generator capable of producing sine, triangular

2017-10-19 15:30:51 12

12 ,具有廣泛的應(yīng)用前景。雷達(dá)信號(hào)源是現(xiàn)代雷達(dá)系統(tǒng)的核心部分。隨著電子信息技術(shù)的發(fā)展,雷達(dá)系統(tǒng)對(duì)雷達(dá)信號(hào)源的要求越來越高。

2017-11-18 12:50:12 6172

6172 為了滿足科研與實(shí)驗(yàn)需要,提出并實(shí)現(xiàn)了一種以FPGA和高速D/A為核心,其結(jié)構(gòu)簡(jiǎn)單,控制靈活,信號(hào)質(zhì)量高的多功能信號(hào)源生成系統(tǒng)。該信號(hào)源生成系統(tǒng)能夠?qū)崟r(shí)產(chǎn)生中心頻率在30~130MHz的各種雷達(dá)、通信

2017-11-23 13:24:01 3837

3837 矢量信號(hào)源與射頻信號(hào)源的區(qū)別是什么?本文為你帶來矢量信號(hào)源與射頻信號(hào)源的詳細(xì)詳細(xì)介紹及區(qū)別分析。

2018-01-08 09:54:13 22244

22244

AD9833是一種低功率可編程波形發(fā)生器,能夠產(chǎn)生正弦、三角形和方波輸出。在各種類型的傳感、致動(dòng)和時(shí)域反射測(cè)量應(yīng)用中需要波形生成。輸出頻率和相位是軟件可編程的,允許容易調(diào)諧。不需要外部組件。頻率

2018-06-19 08:00:00 65

65 下,檢測(cè)靈敏度隨激勵(lì)頻率的增大而增大[1]。相比較其他信號(hào)合成技術(shù),直接數(shù)字頻率合成(Direct Digital frequency Synthesis,DDS)具有頻率轉(zhuǎn)換時(shí)間短,頻率分辨率高,可編程和全數(shù)字化[2]。

2018-06-29 14:00:00 6290

6290

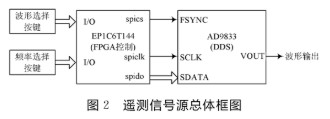

隨著遙測(cè)系統(tǒng)的不斷發(fā)展,系統(tǒng)復(fù)雜程度也隨之提高,因此在終端設(shè)計(jì)中,對(duì)信號(hào)源的頻率穩(wěn)定度、幅值范圍和頻率范圍提出了越來越高的要求。這就要求遙測(cè)系統(tǒng)具備高碼速、實(shí)時(shí)可重構(gòu)、處理復(fù)雜結(jié)構(gòu)的能力,傳統(tǒng)的數(shù)字電路難以實(shí)現(xiàn)這些復(fù)雜功能。

2019-04-23 08:16:00 1933

1933 電子發(fā)燒友網(wǎng)為你提供ADI(ti)AD9833相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有AD9833的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,AD9833真值表,AD9833管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:09:35

來說,信號(hào)源本身的工作應(yīng)該更穩(wěn)定、可靠;另一方面,小型化、通用化信號(hào)源的設(shè)計(jì)和實(shí)現(xiàn)是信號(hào)采集系統(tǒng)的必然要求。因此,必須采用先進(jìn)的設(shè)計(jì)方法和大規(guī)模可編程邏輯器件加以實(shí)現(xiàn)才能適應(yīng)這種發(fā)展趨勢(shì),CPLD/FPGA等大規(guī)模可編程邏輯器件的發(fā)展和EDA技術(shù)的成熟為此奠定了良好的軟硬件基礎(chǔ)。

2020-08-07 17:02:12 1116

1116

詳細(xì)簡(jiǎn)紹了AD9833的使用,含中文手冊(cè),51&32例程等。

2021-06-02 17:39:34 26

26 AD9833 IBIS型號(hào)

2021-06-05 20:02:42 16

16 AD9833評(píng)估軟件

2021-06-07 21:21:11 14

14 片上可編程系統(tǒng)SOPC是一種靈活、高效的SoC解決方案,而FPGA 是可編程再設(shè)計(jì)的“萬能”芯片,FPGA是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,在硅片上預(yù)先設(shè)計(jì)實(shí)現(xiàn)的具有可編程特性的集成電路,未來的FPGA芯片密度不斷提高。

2021-10-01 09:07:00 1614

1614 使用51驅(qū)動(dòng)AD9833模塊的使用關(guān)于AD9833相關(guān)參數(shù)程序流程代碼片上傳程序總結(jié)關(guān)于AD9833AD9833是一款低功耗、可編程波形發(fā)生器,能夠產(chǎn)生正弦波、三角波和方波輸出。各種類型的檢測(cè)、信號(hào)

2021-11-23 17:06:13 48

48 在本文中,我們將使用 Arduino 和 AD9833 DDS 函數(shù)發(fā)生器模塊構(gòu)建一個(gè)簡(jiǎn)單的信號(hào)發(fā)生器,它可以在輸出端產(chǎn)生最大頻率為 12 MHz 的正弦波、方波和三角波。最后,我們將在示波器的幫助下測(cè)試輸出頻率。

2022-08-04 16:55:39 5605

5605

電子發(fā)燒友網(wǎng)站提供《基于AD9833的DDS單通道三信號(hào)發(fā)生器.zip》資料免費(fèi)下載

2022-08-09 09:17:44 11

11 的頻率合成器相比,DDS具有低成本、低功耗、高分辨率和快速轉(zhuǎn)換時(shí)間等優(yōu)點(diǎn),廣泛使用在電信與 電子 儀器領(lǐng)域,是實(shí)現(xiàn)設(shè)備全數(shù)字化的一個(gè)關(guān)鍵技術(shù)。在各行各業(yè)的測(cè)試應(yīng)用中,信號(hào)源扮演著極為重要的作用。但信號(hào)源具有許多不同的類型,不同類型的信號(hào)源在功能和特性上各不相同,分別

2023-07-24 17:30:04 483

483

AD9833是一種數(shù)字控制的頻率合成器,通常用于產(chǎn)生精確的頻率輸出信號(hào)。調(diào)整AD9833的輸出幅度可以通過以下幾種方式進(jìn)行控制: 電源電壓調(diào)節(jié):AD9833的輸出幅度與其工作電源電壓有關(guān)。通過改變

2024-01-09 10:40:09 662

662

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論