電子發燒友網核心提示: 根據ALTERA官方FAE(現場應用工程師)的強烈建議,請注意不要隨意帶電插拔JTAG下載接口,否則會損壞FPGA芯片的JTAG口信號管腳。 現象: 在排除了下載線的問題

2012-09-05 09:00:42 12784

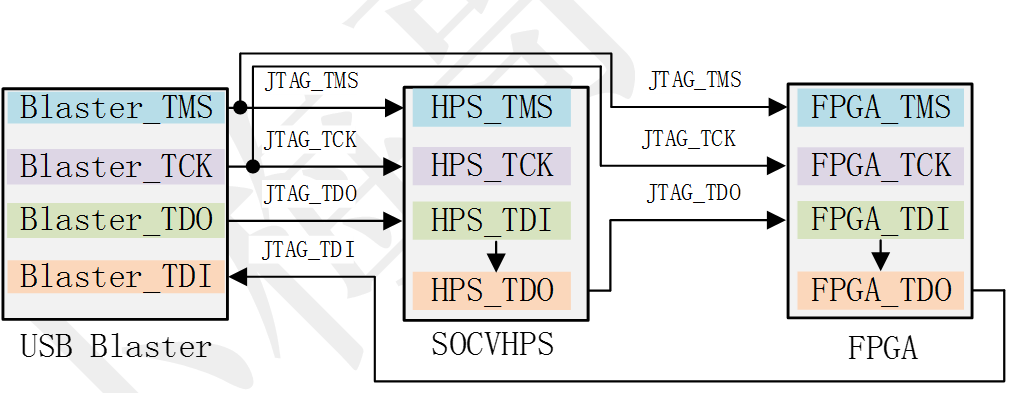

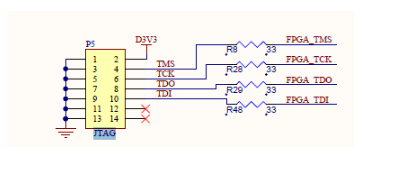

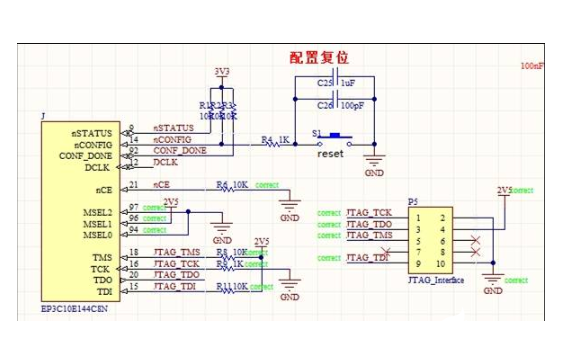

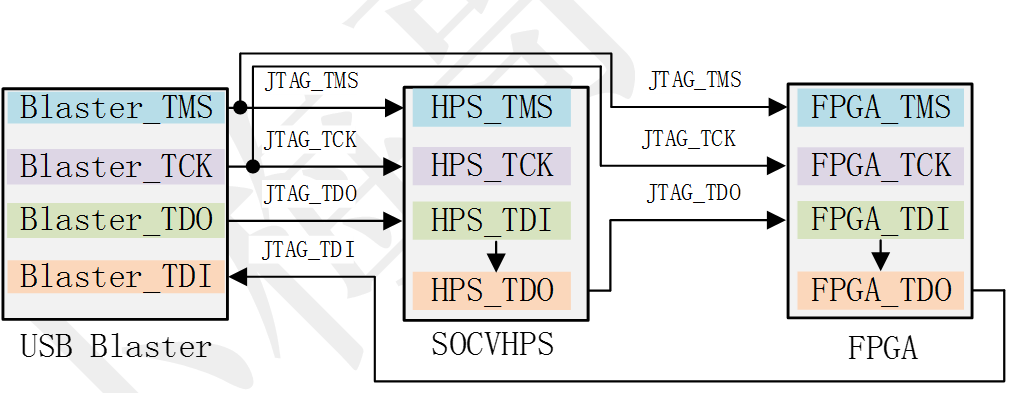

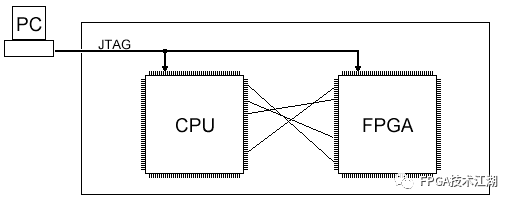

12784 SoC FPGA作為在同一芯片上同時集成了FPGA和HPS的芯片,其JTAG下載和調試電路相較于單獨的FPGA或ARM處理器都有一些差異,但是同時兩者又有緊密的聯系。

2020-08-08 10:08:00 1633

1633

FPGA的管腳主要包括:用戶I/O(UserI/O)、配置管腳、電源、時鐘及特殊應用管腳等。其中有些管腳可有多種用途,所以在設計FPGA電路之前,需要認真的閱讀相應

2019-09-18 07:34:49

=FLASE繞過PAR的檢查,這樣就只是將本該接入專用時鐘管腳(或者叫做全局時鐘管腳)的信號,接到了普通IO口上,但并沒有做好如何用普通IO口來引入全局時鐘,Xilinx官方論壇上更是有老外直接指出這只

2019-07-09 08:00:00

Buffer,支持施密特觸發器的磁滯功能。20/26. nCONFIG專用的輸入管腳。這個管腳是一個配置控制輸入腳。如果這個腳在用戶模式下被置低,FPGA就會丟失掉它的配置數據,并進入一個復位狀態,并將所有

2014-12-29 11:46:33

舉例——altera FPGA配置全過程一個器件完整的配置過程將經歷復位、配置和初始化等3個過程。FPGA正常上電后,當其nCONFIG管腳被拉低時,器件處于復位狀態,這時所有的配置RAM內容被清空

2017-11-22 09:35:19

手上有一塊黑金AX309的板子,Jtag口的排針間距是2.0mm,而我zturn]按道理現在板子高級了,應該都會有保護電路的吧,但是還是要謹慎啊。

2020-04-25 07:00:00

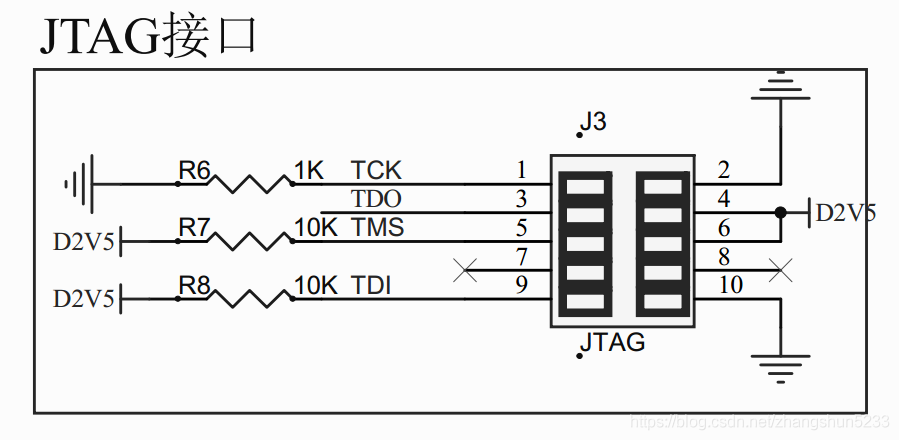

現象: 在排除了下載線的問題后,還是不能訪問FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已經損壞。此時請用萬用表檢查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一個信號對地短路則表示JTAG信號管腳已經損壞。

2019-05-31 07:01:06

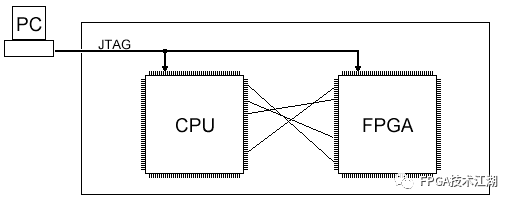

FPGA的JTAG接口和ARM的JTAG接口線是否可以共用同一線呢?是否可以用同usb轉JTAG線給ARM和FPGA以及dsp調試程序呢?

2022-08-10 14:54:43

今天下載時,下載一直失敗,經測量后發現JTAG的TDI引腳與地短路了,請問這能說明是FPGA芯片內部的JTAG接口壞了嗎?還是有肯能是別的問題?有誰遇見過沒?

2013-04-05 22:49:11

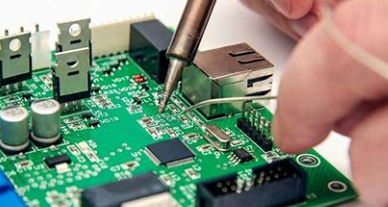

電源部分。使用萬用表進行測試,排除電源短路等情況后,上電測量電壓是否正確。(2)然后焊接FPGA及相關的下載電路。再次測量電源地之間是否有短路現象,上電測試電壓是否正確,然后將手排除靜電后觸摸FPGA

2012-08-12 11:52:54

JTAG口如何配置?怎么使用?

2021-10-29 07:22:26

使用聞亭XDS560V2仿真器,自己做的F***板子,JTAG口經常燒掉,JTAG電路如圖,請問是什么原因,用著用著TRST就和地短路了,已經燒了三個芯片了

2020-05-11 09:52:32

我設計的是FPGA的板子,用JTAG燒寫。直接燒FPGA是沒有問題的,但是燒ROM就會出錯,IDCODE=ff檢驗不通過。網上有人說是JTAG的電平不夠。求問是不是布線的時候JTAG口距離FPGA一定要近一些,線短一些才行?

2013-07-26 15:29:20

“DONE沒有變高”,而當我拿出芯片內核或來自內核的一些信號時,編程成功但之后我的JTAG停止工作。如果我嘗試在iMPACT中初始化JTAG鏈,它會詢問我是否有此設備的BSDL或BIT文件,或者如果我嘗試

2018-10-08 11:19:37

jtag口可以成功下載,as口下載成功但是程序不運行,找了好久一直沒找到原因,電路配置都沒有問題。

2018-01-30 21:30:04

的程序員正常工作7-I檢查我的jtag鏈是否確保電氣關閉(有一個跳線,你可以擴展你的jtag鏈認為FMC連接器)8-我在程序員和fpga板之間使用了兩條不同的電纜(電纜沒問題)解決了所有嫌疑人之后,我

2019-07-11 13:04:21

重點檢查涌浪吸收電路、過電壓保護電路、整流電路是否有故障。如果是行輸出管擊穿,可能保險電阻燒毀,這時應重點檢查行逆程電容是否開焊或燒毀,+B電壓是否過高等故障。燒毀:往往是由于過電流引起,或欠激勵

2013-01-25 21:41:06

請教各位大神!是否可以通過FPGA內核配置的雙口RAM,實現FPGA與DSP之間的數據交換?可以的話怎么實現?怎么設置FPGA的內核RAM?如何連接DSP的外部存儲器XINTF的引腳和FPGA的引腳?謝謝!

2017-12-07 15:44:03

我想通過JTAG在我的設計中內部訪問寄存器。1)如何掛鉤fpga JTAG鏈?2)是否有JTAG控制器IP?我看了,沒看到一個。謝謝,弗雷德

2020-05-29 06:13:24

是+ 1.8V。 BOth是相同的電壓范圍。但是,電壓源是不同的。但是,我想在同一個JTAG鏈中連接兩個設備。如果按照附圖所述進行連接,JTAG鏈是否會檢測CPLD和FPGA?MagalingamCPLD.docx之間的JTAG鏈連接圖103 KB

2020-05-29 14:17:04

CYCLONE IV FPGA 想用JTAG口編程FLASH,MSEL所在BANK被用于DDR,IO電壓為1.8V,手冊的配置方案表中AS模式的配置電壓標準沒有1.8V。是否可以理解成在JTAG方式

2019-03-21 10:24:44

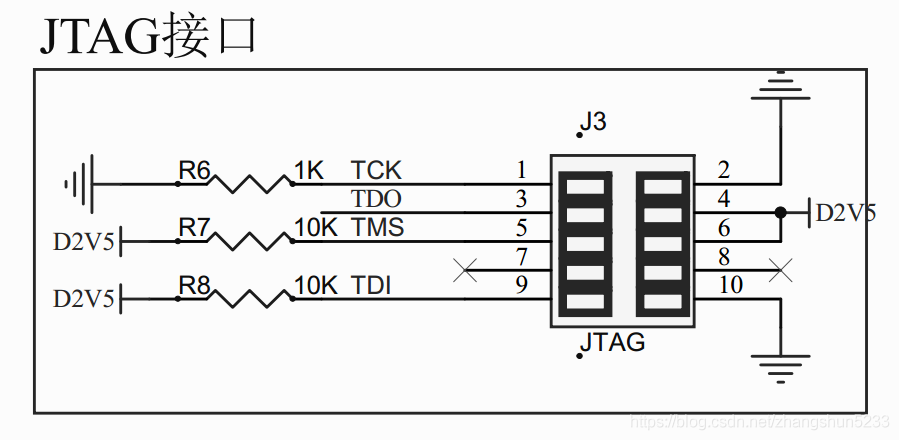

本人學生一枚,在畫的第一塊FPGA板上采用的EP3C25E144這個片子,實際調試中遇到了如下問題,焊上去之后整個JTAG口無法正常工作,TMS與TDI電壓時鐘與VCCIO存在一個壓降,VCCIO用的為3.3v,而這個量管腳的電壓為2.5v,各為幫忙看下JTAG口這部分電路是否存在問題,謝謝的了。

2013-03-30 21:24:12

`各位大佬們,為啥我一上電24V,電容發熱,熱敏電阻被擊穿啊`

2019-11-16 11:02:24

您好:麻煩問一下,你們這個OKMX6UL-C2 的底板是否引出了SAI ,是和那個JTAG 口復用嗎? 還是通過那個GPIO1 ,GPIO2 引出。謝謝。恩。不對吧,我都買了,銷售說是和那個JTAG 管腳復用的。

2022-01-10 07:45:12

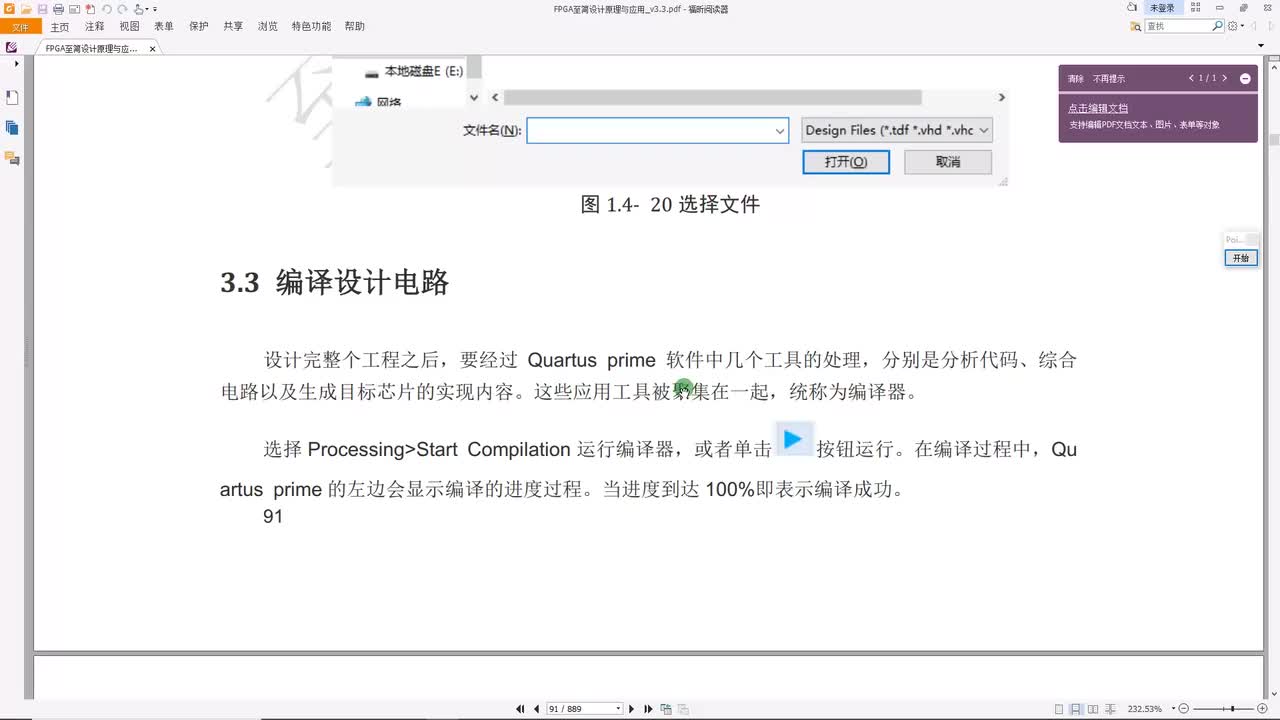

Quartus II 下FPGA管腳鎖定在新建工程、編輯文件、編譯、排錯完成后就進入管腳鎖定以及電平設置階段。這里還是以一位全加器為例介紹管腳鎖定。開發板使用FII-PRA006. 開發工具

2021-07-30 15:09:59

,FPGA無法從EEPROM-XCF32P中自動加載程序,但是通過JTAG口可以給FPGA燒些程序,而且程序也可以燒寫到XCF32P中。4.用示波器測試FPGA的CCLK管腳,無法測試到CCLK。資料上

2015-08-15 09:20:26

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到

2021-05-28 09:23:25

`網上看到了各種版本,有說JTAG口要用3.3V,有說要用2.5V的。手頭有個USB_BLASTER的下載器。不知道具體要用多少伏的。還有一個問題,看官方手冊,說JTAG口的6腳不接。但是我手頭有個開發板,JTAG的6腳與4腳接在一起了。`

2017-10-18 11:29:10

對JTAG的資料認識:(2)JTAG小知識我們經常為了方便,隨意插拔JTAG下載口,在多數情況下不會發生任何問題。仍然有很小的概率因為熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿

2015-05-23 15:51:49

,RTCK管腳一般是用來控制是否使能JTAG接口的,請查閱數據手冊;F - 如果你用的芯片比較特殊,例如STR91X,因為內部掃描鏈是串接的,請設置好TAP,以讓仿真器知道掃描鏈的長度;

2011-11-30 10:18:29

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。JTAG協議制定了一種邊界掃描的規范,邊界掃描架構提供了有效的測試布局緊湊的PCB板上元

2020-02-25 18:40:45

將兩片CPLD的jtag口級聯 是否可以實現一個jtag燒寫兩片芯片

2017-03-31 17:31:54

什么是電容擊穿?電容器被擊穿的條件是什么?電容擊穿是開路還是短路?電容擊穿的原因是什么?如何避免介質擊穿?

2021-06-18 09:59:11

下面的問題,因為熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿。至此,也有人懷疑是否是盜版的USB Blaster或者ByteBlasterII設計簡化,去除了保護電路導致的。但經過很多

2023-05-19 19:47:36

熱插拔而產生的JTAG口的靜電和浪涌,最終導致FPGA管腳的擊穿。至此,也有人懷疑是否是盜版的USB Blaster或者ByteBlasterII設計簡化,去除了保護電路導致的。但經過很多實際情況的反饋

2024-01-19 21:19:29

右鍵然后點擊 show IO banks,這個時候就會看到FPGA的管腳被幾種顏色劃分開了。一種顏色下的IO口代表一組bank。你在吧管腳的locaTIon約束完成以后。IO Bank會自動填充完畢

2019-04-03 07:00:00

,請數據流加載方向如圖7.17所示。當然了,有人可能在想,JTAG在線配置是否和配置芯片加載相沖突呢?非也,JTAG在線配置的優先級是最高的,無論此時FPGA中在運行什么邏輯,只要JTAG下載啟動,則FPGA便停下當前的工作,開始運行JTAG下載的新的配置數據。圖7.17 FPGA離線加載原理 `

2018-03-05 16:30:35

每個單片機GPIO口都有個管腳電平標準,例如輸入到管腳的電壓小于1V被識別為0,大于2V被識別為1,但是如果輸入的電壓是在1-2V之間呢,是會被隨機識別為1或0,還是會是空或者出錯誤?數據手冊沒有

2018-01-19 10:32:11

嗨,我一直在看這個問題:http://forums.xilinx.com/t5/Xilinx-Boards-and-Kits/spartan6-fpga-Jtag

2019-08-01 08:17:03

AVR單片機使用JTAG口作為普通I/O口的方法有哪幾種?JTAG口的配置方式是什么?如何去使用JTAG口?使用JTAG口需要注意什么事項?

2021-07-07 06:22:05

小妹正在做一個軟件,想通過編程把數據傳到PC的并口在從其與jtag接口相連通過從JTAG口TDI串入數據和指令,再從TDO串出掃描結果,在主機上進行比對以實現測試,目前我主要用VC來編程。請問一下我

2008-08-15 16:21:01

我想知道是否有人能指出一份文件,該文件為Xilinx FPGA中的JTAG操作提供了深入的技術細節。我正在考慮將自己的TAP控制器構建到JTAG程序/更新FPGA。我還想了解Xilinx特定JTAG

2019-01-24 09:36:40

現在設計FPGA電路,想用EP4CE40F484,可是數據手冊里沒有A1、B2······這些管腳的定義,想請問一下FPGA管腳定義改怎么看啊?

2018-03-29 10:53:04

的糾紛。防護的話加齊納穩壓管保護。 現在的mos管沒有那么容易被擊穿,尤其是是大功率的vmos,主要是不少都有二極管保護。vmos柵極電容大,感應不出高壓。與干燥的北方不同,南方潮濕不易產生靜電。還有

2018-10-22 15:35:34

司用UF1M的二極管(1A1000V)接在14管腳上,低壓啟動100V時,二極管的電流過大1.2A會擊穿二極管,高壓220V時電壓在1A左右沒有問題,請大神分析下,在它負極端接一個10的電阻對不對,能不能起到限流的作用呢?

2019-01-11 08:00:00

是這樣的。。 LPC2103的 JTAG口 也就是P0.27-P0.31口 如果想作為I/O口的話應該怎么樣設置呢? 光對這幾個管腳進行管腳配置好像沒有用的。。是不是應該對JTAG功能進行屏蔽呢,該怎么屏蔽啊?有沒有大神來指導一下。。

2014-01-14 15:06:02

如題,怎么通過XILINX的FPGA 的JTAG 抓取CPU MPC865T的時序信號,CPU是否需要一個驅動器才可以發送片選以及讀寫等信號?求懂的大神說說,萬分感謝!

2016-06-22 13:11:11

現在懷疑板子上的電容被擊穿了,請問電容被擊穿是開路還是短路?謝謝

2016-11-29 21:04:02

本帖最后由 yangk1990 于 2013-3-8 17:11 編輯

本人初學,需要設計一個示波器觀測電容器被擊穿的波形(或者可變電容逐漸減小到變成導體也行),但電容器的擊穿著實不會...希望大神們能夠指點一下!

2013-03-07 20:38:47

XAPP1251說明顯示,可以在Zynq ARM處理器上運行XVC服務器來控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一個FPGA中控制PL JTAG?可以使用運行在設備PS部分上

2020-07-30 13:51:19

TM4C將jtag口鎖定后解鎖,就會將flash全部擦除。而在bootloader中只看到編程的命令,沒有讀取的命令。那這樣的話是否將jtag口鎖定后是否就能起到保護flash代碼的作用,而不需要使用MPU。因為MPU部分沒做過,看文檔也是看得云里霧里的。

2019-09-09 07:43:19

本帖最后由 一只耳朵怪 于 2018-6-21 15:55 編輯

JTAG調試的下載器選用TI有配套的么?JTAG口在電路設計上可以如FPGA的JTAG口一樣設計為2.54間距的排針么

2018-06-21 04:41:08

實驗用到基于FPGA的數據采集板,兩個月前焊好調試好了。現在拿出來用發現用不了串口通信業有問題,但是通過JTAG和AS口都能下載成功程序。在這樣的情況下有沒有可能板子已經壞了?求高手解答

2015-01-28 17:28:28

不出高壓。與干燥的北方不同,南方潮濕不易產生靜電。還有就是現在大多數CMOS器件內部已經增加了IO口保護。但用手直接接觸CMOS器件管腳不是好習慣。至少使管腳可焊性變差。 MOS管被擊穿的原因

2022-05-14 10:22:39

本檢查清單向你揭示了如何提高你的FPGA設計的速度和可靠性,本檢查清單適用于Xilinx公司的Virtex系列FPGA.采用這些技巧應該能改進你的設計性能,本檢查清單應該能幫助所有的FPGA設計

2009-02-07 10:21:06 28

28 本內容向大家提供了JTAG功能及系統設計 JTAG也是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的高級器件都支持JTAG協議,如DSP、FPGA器件等。標準的JTAG接口是

2011-03-30 10:04:32 0

0 通常所說的JTAG大致分兩類,一類用于測試芯片的電氣特性,檢測芯片是否有問題;一類用于Debug;一般支持JTAG的CPU內都包含了這兩個模塊。

2011-09-28 10:16:17 3327

3327 如何檢查光耦是否損壞?

2012-07-02 14:02:13 7265

7265 Xilinx的JTAG電纜可以通過FPGA“直接”燒寫SPI/BPI。很多對xilinx開發環境不熟悉的用戶,如果第一次接觸這種燒寫模式可能會有疑惑,FPGA是如何做到JTAG和Flash之間

2017-02-08 02:40:11 6513

6513

最近自己做了一塊FPGA板子,不慎將PROM的兩根引腳連錯,導致在配置時無法正確識別PROM的型號,顛三倒四地排除了一個星期問題最終幸運解決。之后感嘆自己實在是不小心,導致如此低級錯誤,不過排錯

2017-02-11 06:53:11 2895

2895 同志們,根據ALTERA官方FAE(現場應用工程師)的強烈建議,請注意不要隨意帶電插拔你的JTAG下載接口,否則會損壞FPGA芯片的JTAG口信號管腳。

2019-07-31 17:35:00 0

0 檢查文件是否存在的方法, 在Python3 文件操作中經常被用到, 因為,只有文件存在, 我們才可以對文件進行下一步處理, 那么,常用的檢查文件存在的方法有哪些呢?以下是Python3 檢查文件是否存在的幾種方法。

2020-10-26 17:08:14 14

14 當一個電路板焊接完后,在檢查電路板是否可以正常工作時,通常不直接給電路板供電,而是要按下面的步驟進行,確保每一步都沒有問題后再上電也不遲。 連線是否正確 檢查原理圖很關鍵,第一個檢查的重點是芯片

2022-11-16 18:26:29 2100

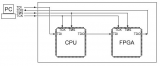

2100 JTAG可以控制(or hijack)所有IC的引腳。在圖片上,也許JTAG將使所有CPU引腳輸出,以及所有FPGA引腳輸入。然后,通過從CPU引腳發送一些數據,并從FPGA引腳讀取值,JTAG可以確保電路板連接良好。

2020-11-29 11:21:14 2280

2280

本文檔的主要內容詳細介紹的是FPGA JTAG工具設計的教程說明。

2020-12-31 17:30:55 18

18 賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協議所規定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[1:0] 的電平,都可用采用該配置模式。JTAG模式不需要額外的掉電

2020-12-31 17:30:55 13

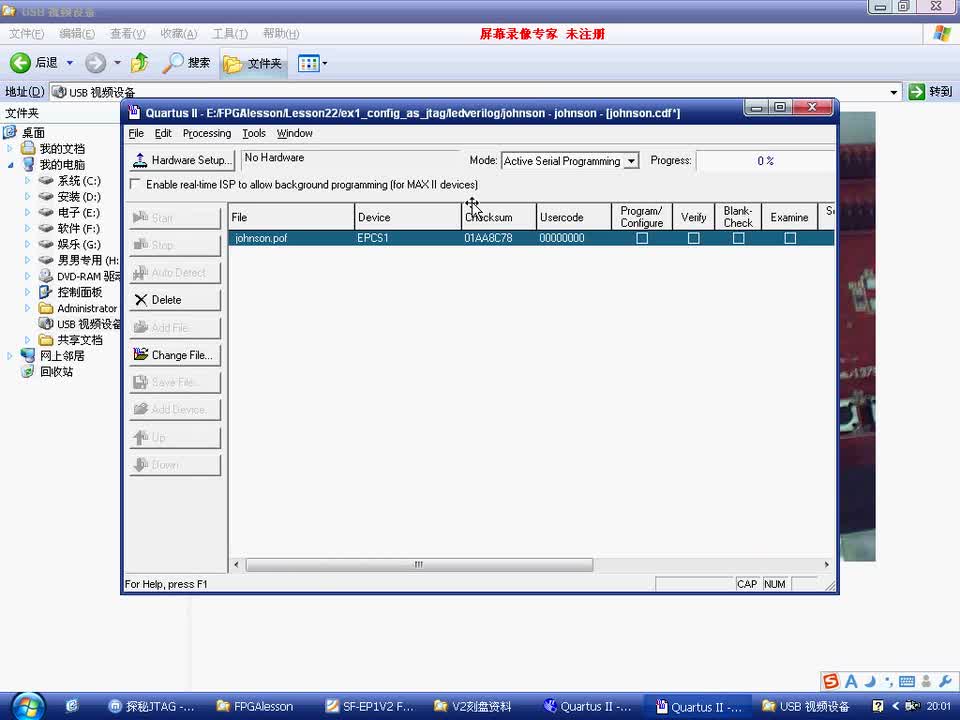

13 ? 學習了 FPGA 一段時間,簡單的設計仿真驗證以及有所熟悉,今天將學習通過 JTAG 固化程序。具體步驟以及截圖如下: 本教程使用的軟件是:Quartus II 13.0 芯片型號

2021-03-05 15:17:50 5248

5248 在FPGA研發及學習過程中,有一個關鍵步驟就是下板實現,做硬件“硬現”很重要,一般來說用JTAG口比較常見一些,因此相信肯定有些大俠遇到過JTAG口失靈或者損壞無法使用的事情。

2021-03-17 14:05:33 11336

11336

開發板(在本文中將其簡稱為“FPGA開發板”)和專用 JTAG 調試器(在本文中將其簡稱為“JTAG 調試器”)。

2021-03-23 10:00:28 41

41 在stm32 IAP例程中,跳轉到APP區的時候,都會檢查棧頂地址是否合法,以及reset地址是否正確等信息,那么這些判斷具體依據什么原理???以stm32H743為例說明↓↓↓↓檢查棧頂是否合法

2021-12-16 16:58:19 10

10 對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試

2022-02-16 16:21:36 1900

1900

根據查閱資料及本人的一些實踐經驗所得,在使用JTAG下載接口的過程中,請不要隨意帶電插拔,否則會損壞FPGA芯片的JTAG口信號管腳。那么如何去確認JTAG口已經損壞了呢。首先你要去排除基本的幾項因素

2022-07-26 09:29:34 884

884 檢查原理圖很關鍵,第一個檢查的重點是芯片的電源和網絡節點的標注是否正確,同時也要注意網絡節點是否有重疊的現象。另一個重點是原件的封裝,封裝的型號,封裝的引腳順序(切記:封裝不能采用頂視圖,特別是對于

2022-08-26 20:19:15 3192

3192

過壓擊穿是可控硅擊穿的主要原因之一,可控硅對過壓的承受能力幾乎是沒有時間的,即使在幾毫秒的短時間內過壓也會被擊穿的,因此實際應用電路中,在可控硅兩端一定要接入RC吸收回路,以避免各種無規則的干擾脈沖所引起的瞬間過壓。如果經常發生可控硅擊穿,請檢查一下吸收回路的各元件是否有燒壞或失效的。

2022-09-15 16:58:02 5158

5158 通過JTAG接口為FPGA下載程序時遇到了速度很慢甚至ISE上配置TCK時鐘最小的為250kHz時,依然無法保證下載成功。

2023-06-25 16:06:58 1130

1130

如何檢查消防應急燈是否正常工作? 檢查消防應急燈是否正常工作需要按照以下步驟進行: 一、查看外觀是否完整 首先,要檢查消防應急燈的外觀是否完整,有無破損或損壞的情況。消防應急燈的外觀應整潔,無裂紋

2023-11-08 16:41:32 2199

2199 如何判斷故障點是否擊穿放電?若故障點未擊穿能否長時間帶電測量? 判斷故障點是否擊穿放電的方法通常有以下幾種: 1. 視覺檢查:故障點周圍是否存在燒焦、熔化或濺融等現象。如果存在這些現象,說明故障

2023-12-26 16:01:51 160

160

電子發燒友App

電子發燒友App

評論