FPGA是電子器件中的萬能芯片,Xilinx FPGA處于行業龍頭地位更是非常靈活。FPGA管腳兼容性強,能跟絕大部分電子元器件直接對接。Xilinx SelectIO支持電平標準多,除MIPI

2022-08-02 09:31:28 4824

4824

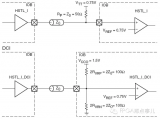

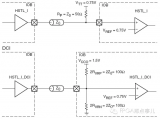

MIPI 接口現在非常流行,國產FPGA目前基本都帶MIPI接口,而AMD-Xilinx是從U+系列開始支持MIPI電平,從國內使用情況來看,7系列FPGA是使用最廣的器件,所以這次使用的FPGA是7系列FPGA使用電阻網絡實現MIPI電平的例子。

2023-04-24 09:30:06 3711

3711

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

標準。通過軟件的靈活配置,可適配不同的電氣標準與I/O物理特性,可以調整驅動電流的大小,可以改變上、下拉電阻。目前,I/O口的頻率也越來越高,一些高端的FPGA通過DDR寄存器技術可以支持高達

2023-05-30 20:53:24

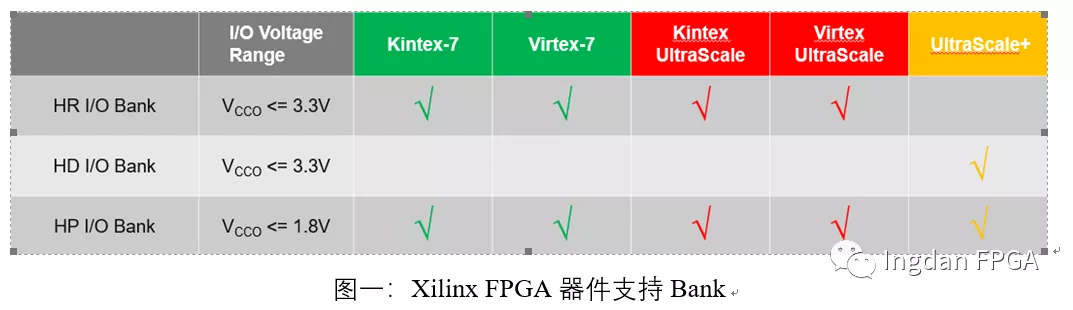

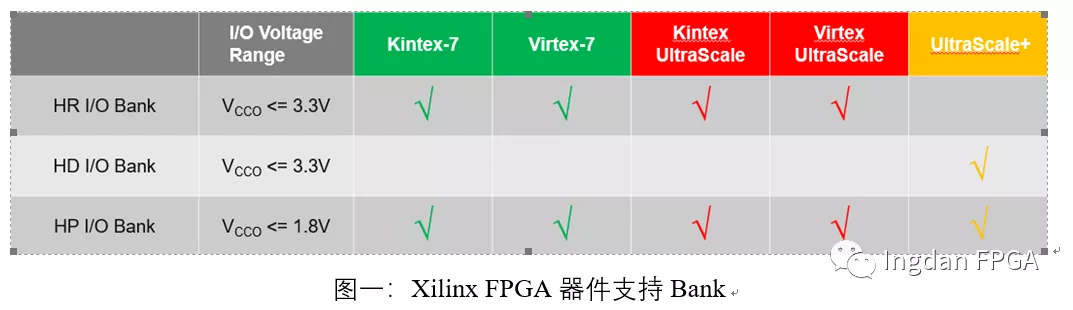

標準,因而為您的系統提供了理想的接口橋接。FPGA 內的 I/O 按 bank 分組 (見下圖) ,每個 bank 能獨立支持不同的 I/O 標準。 目前最先進的 FPGA 提供了十多個 I/O

2021-06-29 08:00:00

,我們不得不多提兩句,畢竟可以兼容非常多的I/O電壓標準是FPGA的一大優勢,尤其是各種高速差分信號的支持。圖3.15中列出了我們這款器件支持的各種I/O電平標準。(特權同學,版權所有)圖3.15

2019-01-10 09:34:18

外設電路(I/O應用)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA器件擁有著豐富的I/O資源,它

2019-04-12 06:35:33

FPGA的I/O結構的發展的怎么樣了?

2021-04-29 06:12:52

`作者:stark眾所周知FPGA的硬件資源被劃分為若干個不同的bank,Xilinx一些高端的FPGA器件由22個甚至更多個bank組成,這樣設計主要是為了提高靈活性。FPGA的I/O支持1.8V

2018-08-02 09:37:08

Specific Integrated Circuit,專用集成電路)之間的相互通信是通過I/O發出高低電平進行通信的,這些電平都要符合相應的電平標準。圖1 :傳輸模型現在數字通信系統中,I/O電壓標準包括早期

2023-02-14 15:58:28

有份作業要求查I/O標準有哪些,及其電平指標和使用場合,百度谷歌不到詳細介紹的,有可以推薦的地址或是書本么?感激不盡哈,或者直接回我下,拜托了

2013-09-13 20:58:44

我在使用xilinx芯片的許多電路板上遇到了一些奇怪的問題。在我們的3個I / O引腳上,我連接了施密特逆變器,驅動了一些LED。這一直有效,如果沒有加載xilinx程序,這些LED將保持開啟狀態

2019-05-16 14:05:51

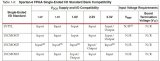

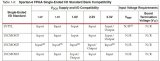

I/O接口標準1.單端信號接口標準LVTTL和LVCMOS(JESD8-5,JESD8-B)SSTL(JESD8-8,JESD8-9B,JESD8-15)HSTL(JESD8-6)LVTTL

2021-11-17 06:38:50

這里寫目錄標題I/O端口原理單片機知識點補充實戰1——閃爍LED指示燈I/O端口原理I/O英文全稱是 Input/Output,即輸入/輸出。單片機端口是標準雙向口,就是說,單片機的端口既可以

2022-01-20 07:55:51

XILINX FPGA/CPLD ISE下載教程 第一章 XILINX FPGA/CPLD ISE下載教程——下載.bit文件第二章 XILINX FPGA/CPLD ISE下載教程——燒錄Flash 圖文詳細資料!

2019-08-15 00:32:31

按照Bank進行劃分,每個Bank獨立供電,以使FPGA I/O適應不用電壓標準,增強I/O設計的靈活性。每個用戶Bank包括50個I/O管腳或者24對差分對管腳(48個差分信號),Top

2021-05-28 09:23:25

按照Bank進行劃分,每個Bank獨立供電,以使FPGA I/O適應不用電壓標準,增強I/O設計的靈活性。每個用戶Bank包括50個I/O管腳或者24對差分對管腳(48個差分信號),Top

2021-07-08 08:00:00

`Xilinx FPGA入門連載23:PLL實例之功能簡介特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 PLL概述PLL

2015-11-10 08:44:06

FPGA SF-SP6入門指南 -- 經典模式流水燈實驗Lesson25 特權Xilinx FPGA SF-SP6入門指南 -- PLL實例之功能簡介Lesson26 特權Xilinx FPGA

2015-07-22 11:49:20

你好,Xilinx Virtex 5 FPGA可以接受邏輯電平0 / 1.8V的輸入并提供邏輯電平0 / 3.3V的輸出嗎?謝謝。asenapati以上來自于谷歌翻譯以下為原文Hello, Can

2018-10-29 14:19:38

Xilinx 7系列FPGA簡介--選型參考

2021-02-01 06:10:55

,支持最大1.8V的I/O信號,HR主要為了支持更廣泛的I/O標準,支持最大3.3V的I/O信號。 Xilinx 7系列FPGA的HR和HP bank,每個bank有50個I/O管腳,每個I/O管腳

2020-12-23 17:17:47

FPGA最小系統說白了就是設計一個最小系統,其可以作為日后一系列產品的基礎,一是可以加快開發流程,二是可以降低開發難度,本次選用的芯片是Xilinx(賽靈思)的7系列(ARTIX)的FPGA

2021-11-11 07:39:20

嗎?我從xilinx的數據表中讀到,它說,'每個具有時鐘功能的輸入都可以配置為任何I / O標準,包括差分I / O標準'。這是否意味著無論vcco是什么,mrcc引腳都可以用于任何I / O標準

2020-08-14 09:22:43

本帖最后由 zht24kobe 于 2013-4-20 14:23 編輯

請教一下各位,fpga的引腳電平(I/O standard)應該設置為多少呢,當然和芯片連接的時候可以參考芯片的說明,其他時候,比如LED,外接晶振,按鍵啊,這些時候電平設為多少合適,是不是越低越好,這樣功耗少一些?

2013-04-20 14:21:33

=643031121063本套FPGA-Xilinx平臺視頻教程適合零基礎,基礎進階、工作者提高的課程。課程講解FPGA簡介,歷史,開發流程,Verilog語法,VIVADO平臺軟件使用。如果您是非計算機專業,想轉行FPGA開發,或者您想FPGA基礎更扎實,此課程將是你無二的選擇。

2021-12-17 15:38:53

確定: - 損壞的用戶I / O引腳的鉗位二極管運行良好(我測量過) - 為LVCMOS25和上拉設置了正確的FPGA配置 - 即使在損壞的用戶I / O引腳上將輸入電壓設置為邏輯電平“0”,我也始終

2020-04-07 12:26:15

嗨, 我想把晶體振蕩器的CLK帶到FPGA里面的數字設計。該CLK連接到FPGA的I / O引腳。如果我在映射中運行Impliment設計,我將得到錯誤。所以我將在UCF文件中將網名命名如下。NET

2019-01-29 10:05:43

嗨,我想為我的xc7k160t-1fbg676 Kintex-7制作.XDC文件,我想知道哪些I / O標準適用于FPGA的每個引腳。例如,我想在使用LVCMOS15和將LVCMOS25用于某些引腳

2020-08-11 06:56:00

STM32單片機---(二)I/O應用stm32I/O簡介GPIO的8種工作模式stm32I/O簡介在 STM32 中I/O 引腳,又稱為GPIO (General-Purpose I/O),可以被

2022-02-16 07:04:02

我想使用外部1K Hz時鐘或寫入遇到代碼將時鐘分配到K Hz電平,它會起作用嗎? 第二個問題是如何定義I / O類型,我想使用單個lvcmos3.3V作為I / O標準。我應該在哪里定義I / O標準?在代碼中我還是需要將供應跳線改為3.3位置?感謝您的幫助!

2020-04-29 09:22:03

的時鐘設計方案10.3.5 Rocket I/O的開發要素10.3.6 Rocket I/O IP Core的使用10.4 基于Xilinx FPGA的千兆以太網控制器的開發10.4.1 千兆以太網

2012-04-24 09:23:33

Xilinx Kintex-7 XC7K325T-2FFG676I嵌入式核心板簡介圖 1Xilinx Kintex-7核心板簡介創龍科技SOM-TLK7是一款基于Xilinx Kintex-7系列

2021-12-20 06:47:57

請問一下我在使用51最小系統板做流水燈的時候通過程序無法改變I/O輸出電平是怎么回事,I/O持續輸出5V高電平,但是把芯片換到另一個基座就可以改變,請問哪里可能出問題了

2023-09-27 07:38:20

I/O控制對于單片機而言是最基礎最核心的東西,其實單片機除了模/數轉換之外的事情。其他大部分的事情I/O口都能做的到。I/O控制簡單卻能千變萬化。單片機在大部分應用中做的事情,莫過于 輸入高低電平

2021-11-24 06:47:23

要使用FPGA實現150M的光纖通訊,使用XILINX XAPP244的串行數據恢復功能感覺有些麻煩。使用XILINX的ROCKET I/O 實現150M的光纖通信合適/可行嗎?

2013-03-26 16:06:30

我是一個學生,老師讓我們了解目前FPGA支持的單端I/O標準有哪些,以及具體參數。在網上搜了許久,都沒有找到,所以到這里希望高手指教。也希望路過的各位能推薦下平常查找資料的網站。小弟謝謝各位了!

2012-09-22 23:34:21

單片機I/O口如何檢測按鍵輸入電平?

2021-10-26 07:01:11

標準雙向輸入/輸出推挽輸出具有很強的推動能力高阻態輸入I/O接口寫入1或0不改變接口的電平,I/O接口只能用于輸入,引腳輸入高電平,對應的寄存器為1,引腳輸入低電平或者懸空,對應寄存器為0.開漏狀態

2022-02-18 06:11:02

元/片能夠承受。需要的I/O數量不多,100個足夠,不需要高速通信。怕研發過程中器件停產了 ,所以特來請教各位大俠,目前常用的FPGA系列,可有合適的推薦。謝謝!

2016-11-28 20:52:09

如何克服FPGA I/O引腳分配挑戰?

2021-05-06 08:57:22

操作PIC24 I/OPIC24是一款16位的單片機,它的I/O操作和STM32差不多,但是比STM32更簡單。操作PIC24的I/O輸出高低電平需要配置一下寄存器:1.TRISx,該寄存器控制I

2021-11-24 07:30:02

是相同的理論。但鍵盤不工作(工作電壓為5V)。如何選擇I / O標準以使5V鼠標或鍵盤工作?我希望別人可以幫我解決這個問題,謝謝。以上來自于谷歌翻譯以下為原文I can use the VGA

2019-07-02 07:49:05

嗨專家,我正在使用Spartan3AN(XC3S50AN)FPGA板和平臺線USB II。你能告訴我如何通過JTAG監控PC中FPGA I / O的狀態嗎?謝謝,V。Prakash以上來自于谷歌翻譯

2019-06-18 09:05:14

你好Xilinx收發器使用CML IOSTANDARD。在xilinx 7系列示例設計中,有固定的GTREFCLK位置,但其他引腳未配置(txdata / rxdata)在下面的I / O表中,txdata和rxdata引腳未配置CML I / O標準。我如何配置CML I / O標準?

2020-08-13 10:10:53

) / 數位類比轉換器 (DAC),還有數位緩沖記憶體 (Buffer),進而提供標準的 I/O功能集。但在 NI FlexRIO FPGA 模組上,FPGA 針腳是直接連至前端接頭;因此工程師不需特別

2019-04-28 10:04:14

數字系統中,經常會出現多種電氣接口標準。可是 FPGA 器件的每一個 I/O 并不支持所有的電氣接口標準,在選型時要特別注意電氣接口標準的適配情況。 封裝方式: 主要需要在兩個方面考量,第一個就是可用

2020-12-23 17:21:03

大家好,我想檢查FPGA功能和I / O引腳功能在我的主板上使用“Selftest application”。在我的Selftest應用程序中,我可以使用哪些方法來檢查這些?請提供一些想法。謝謝

2019-04-01 12:33:26

FPGA的I/O口如果作為input,輸入外部控制信號,電平還有其他設置等等,與作output時有什么區別?

2016-06-21 12:50:04

我有一個用于過時的Xilinx FPGA的加載文件。是否有機會將其轉換為Xilinx新FPGA的文件?例如斯巴達。以上來自于谷歌翻譯以下為原文I have a loading fille fora

2019-02-13 07:53:44

Verilog中還是內置于I / O端口的FPGA板中。干杯以上來自于谷歌翻譯以下為原文Hi,I'm new to FPGAs (and so to the Xilinx family of FPGAs), so

2019-06-04 12:36:34

我需要用 Xilinx FPGA 與 AD7626 接口,之間有 CNV、CLK、DCO、D 四對 LVDS 信號,請問 FPGA 里應該采用怎樣的 LVDS 電平標準與 AD7626 匹配?

2018-07-27 08:46:59

我需要用 Xilinx FPGA 與 AD7626 接口,之間有 CNV、CLK、DCO、D 四對 LVDS 信號,請問 FPGA 里應該采用怎樣的 LVDS 電平標準與 AD7626 匹配?

2023-12-08 07:24:25

Devkit I應該去的建議(10位通用1.2V I / O)?我搜索了很多Xilinx開發套件,但是大多數I / O電壓電平都是2.5V / 3.3V,如果開發套件中沒有可以改為1.2V,我可能需要在器件和開發套件之間使用電壓移位器。

2019-09-25 11:54:58

可以告訴我應該做什么,如果有可能讓ML507上的J6引腳2輸出1.8v的信號而不使用電平轉換器,只需將FPGA GPIO信號I / O標準設置為LVCMOS即可1.8V?最好的祝福,埃爾維斯·道森

2019-08-22 10:02:12

本帖最后由 一只耳朵怪 于 2018-6-11 17:19 編輯

復位28335時,默認狀態下,i/o口的狀態是高電平還是低電平?

2018-06-11 00:11:51

輕松實現高速串行I/OFPGA應用設計者指南輸入/輸出(I/O)在計算機和工業應用中一直扮演著關鍵角色。但是,隨著信號處理越來越復雜,I/O通信會變得不可靠。在早期的并行I/O總線中,接口的數據對齊

2020-01-02 12:12:28

嗨,能否建議我用Xilinx FPGA直接替代智能融合FPGA。目前我的參考設計客戶端正在使用智能融合(A2F200M3F-1FGG256I)FPGA。我想用Xilinx FPGA代替。在配置期間,FPGA引腳不應處于浮空狀態,FPGA引腳應處于已知狀態。這是我項目的嚴格要求。謝謝,C.一個雷迪。

2020-05-13 08:22:47

FPGA怎么選擇?針對功耗和I/O而優化的FPGA介紹

2021-05-06 09:20:34

品牌XILINX/賽靈思封裝240-PQFP批次08+數量3500濕氣敏感性等級 (MSL)3(168 小時)產品族嵌入式 - FPGA(現場可編程門陣列)系列Spartan?-XLLAB/CLB

2022-04-19 09:45:33

品牌XILINX封裝BGA批次新批次數量1300制造商Xilinx產品種類FPGA - 現場可編程門陣列發貨限制:此產品可能需要其他文件才能從美國RoHS是產品Zynq UltraScale+

2022-04-19 09:50:58

品牌XILINX封裝BGA1152批次1913+數量4480制造商Xilinx產品種類FPGA - 現場可編程門陣列系列XC2VP30邏輯元件數量30816 LE自適應邏輯模塊 - ALM13696

2022-04-19 09:52:28

產品概述產品型號 XC7K410T-2FFG900C描述IC FPGA 500 I/O 900FCBGA分類集成電路(IC),嵌入式-FPGA(現場可編程門陣列)制造商Xilinx公司系列

2022-08-04 11:20:31

FPGA建立在先進的高性能,低功耗(HPL),28 nm高k金屬柵極(HKMG)工藝技術之上,可實現I / O帶寬2.9 Tb / s,200萬邏輯單元容量和5.3 T

2022-11-10 15:11:11

FPGACPLD設計工具——Xilinx ISE使用詳解的主要內容:第1章 ISE系統簡介第2章 工程管理器與設計輸入工具第3章 ModelSim仿真工具第4章 ISE中集成的綜合工具第5章 約束第6章

2009-07-24 16:06:58 197

197 FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440單元, 950 mV至1.05 V, FBGA-484Xilinx Artix?-7 FPGA系列

2023-05-10 16:03:24

本書系統地論述了Xilinx FPGA開發方法、開發工具、實際案例及開發技巧,內容涵蓋Xilinx器件概述、Verilog HDL開發基礎與進階、Xilinx FPGA電路原理與系統設計

2012-07-31 16:20:42 11268

11268

本文是關于 xilinx公司的7系列FPGA應用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發環境

2016-01-18 15:30:32 45

45 作者:Player? FPGA那點事兒 一、GTLP(GunningTransceiver Logic Plus) GTL+電平標準即岡寧收發器邏輯電平標準加,是在Pentium Pro處理器中首先

2017-02-08 02:58:44 2356

2356

Xilinx FPGA的I/O兼容多種電平標準,包括LVTTL、LVCMOS、LVDS、LVPECL等,下面對各類電平標準做簡要介紹。 一、LVTTL(LowVoltage

2017-02-08 03:42:12 4800

4800

FPGA的IO支持多種電平標準,但是其中用幾點的概念比較模糊,在此特意記下: 最近在用xilinx的spartan 6 與ARM進行通信,但是FPGA的邏輯電平是3.3V的LVTTL標準,而ARM

2017-02-08 10:36:06 892

892

Xilinx FPGA的Maxim參考設計

2017-10-31 09:59:24 23

23 本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 我們在對FPGA項目進行約束的時候,常常看到這樣的電平標準,例如LVCOM18,LVCOS25,LVDS,LVDS25等等,其實這些都是一系列的電平標準,為了更加深刻地理解電平標準,下面摘選自《FPGA之道》這本書對于電平標準的講解來理解。

2020-08-24 17:32:39 4266

4266 PCI電平標準即外設器件互聯電平標準,該標準支持33MHz和66MHz的總線應用,包括PCI-X、PCI-33、PCI-66等各類電平標準,該標準的輸入輸出供電電壓(VCCO)為3.3V,不需要參考電壓(VREF)和終端電壓(VTT)。

2021-01-06 17:13:00 12

12 本文檔的主要內容詳細介紹的是Xilinx FPGA IO的GTLP和HSTL電平標準的詳細說明。

2021-01-06 17:13:53 23

23 Xilinx-7系列FPGA主要包括:Spartan?-7、Artix?-7、Kintex?-7、Virtex?-7。其性能、密度、價格也隨著系列的不同而提升。和前幾代FPGA產品不同的是,7系列

2021-01-30 06:00:11 16

16 Xilinx FPGA開發實用教程資料包免費下載。

2022-04-18 09:43:46 24

24 Xilinx FPGA pcb設計

2023-05-29 09:11:36 0

0 XILINX FPGA簡介-型號系列分類參考

FPGA(Field Programmable Gate Array)是在PAL (可編程陣列邏輯)、GAL(通用陣列邏輯)等可編程器件的基礎上

2023-03-10 16:27:57 5185

5185

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 215

215

電子發燒友App

電子發燒友App

評論