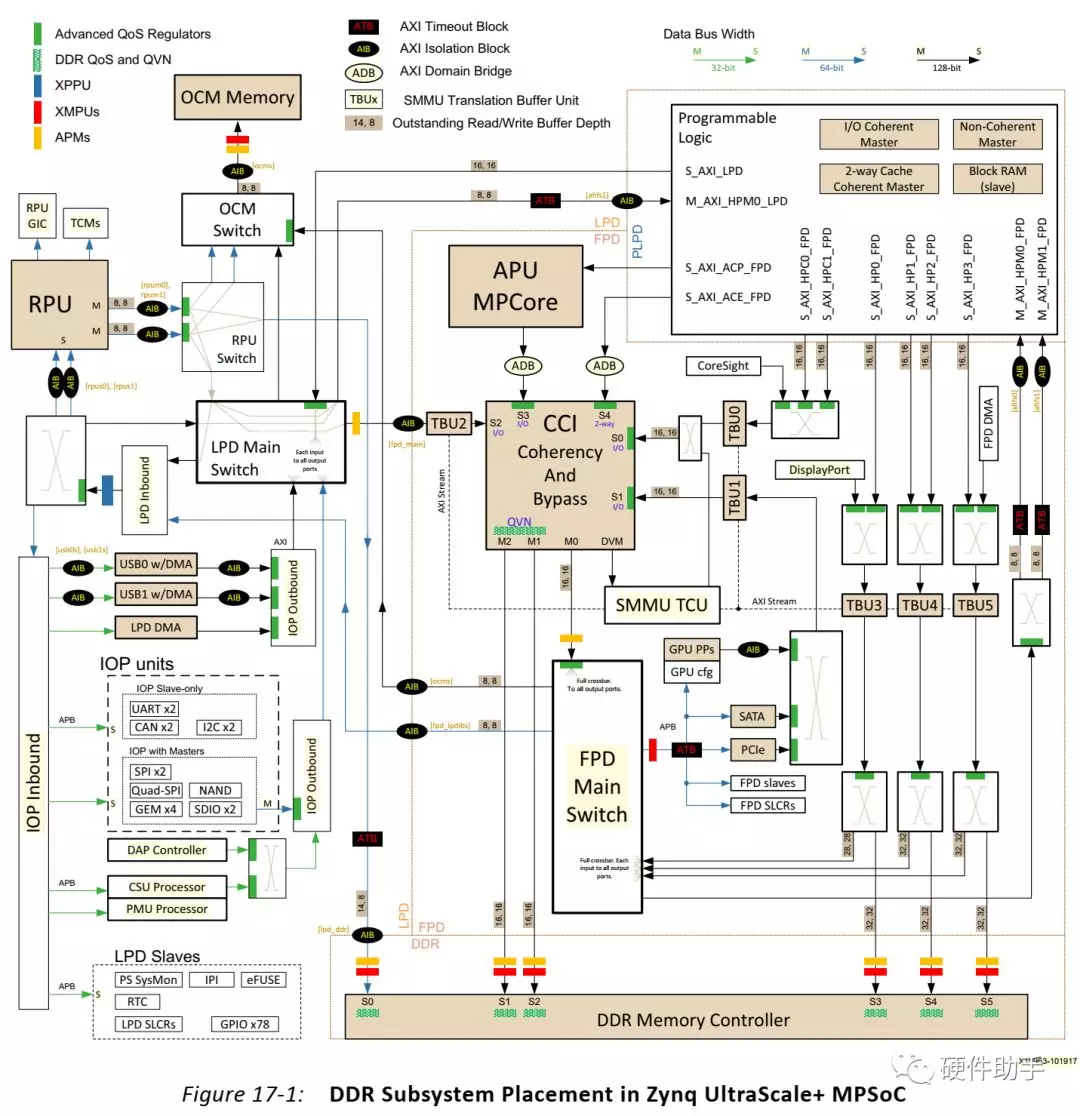

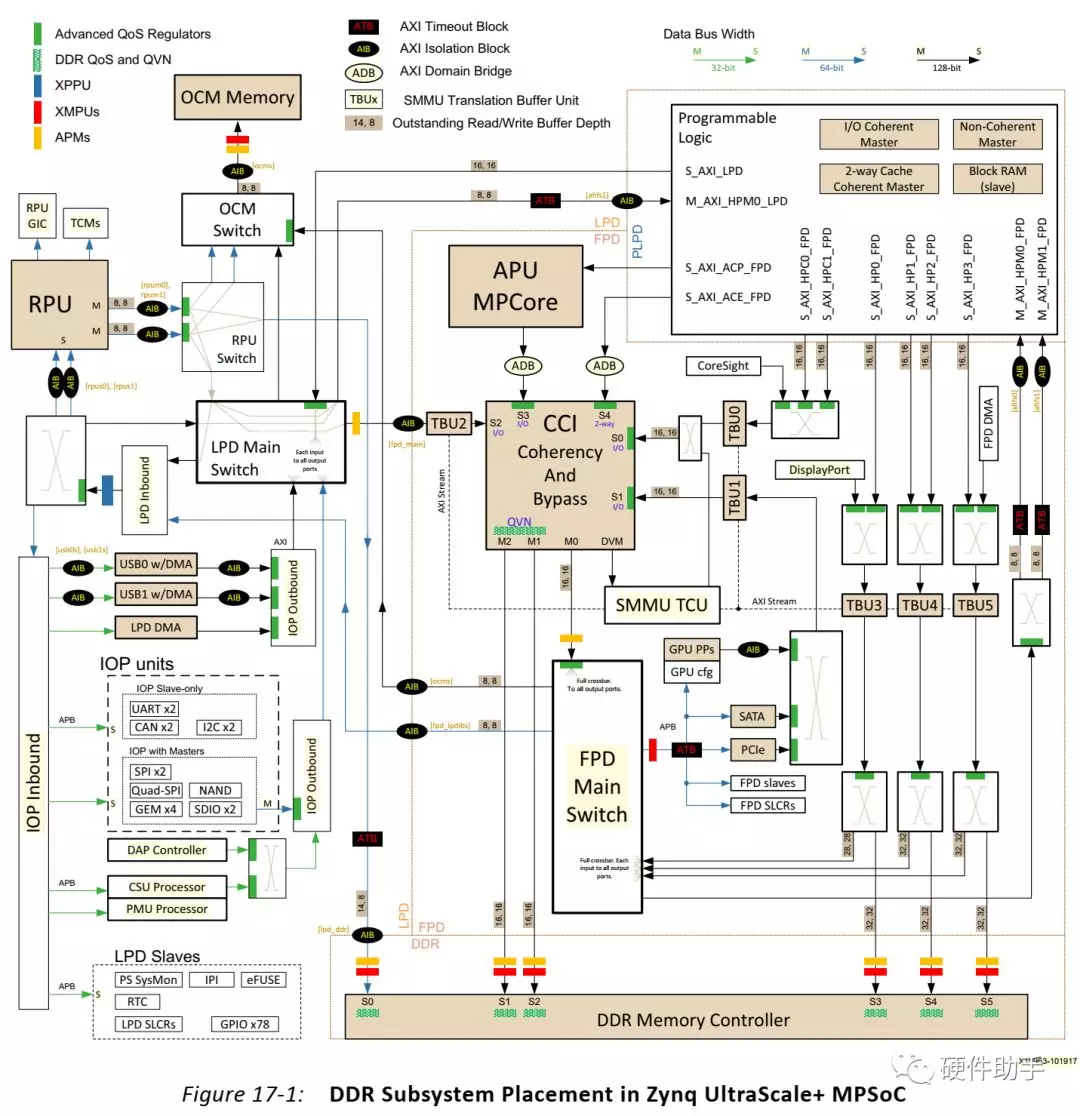

是DDR4和DDR3,其他系列相對使用較少一些,本文主要以DDR4進行介紹。 1、選型 根據(jù)ZU+系列芯片的數(shù)據(jù)手冊、TRM、pg150等文檔,DDR可以掛載在PS側(cè),也可以掛載在PL側(cè),也可同時掛載在PS

2020-12-21 14:04:36 7224

7224

用戶端使用的,框圖如圖1所示。 如圖1 所示的中間部分為我們調(diào)取的IP 核,user FPGA Logic 為用戶端邏輯,DDR2/DDR3 SDRAM 為存儲芯片。其中IP 核與存儲芯片之間的總線大部分

2020-12-31 11:17:02 5068

5068

2、512Mb-2Gb LP DDR2,以及?LP DDR4x、LP DDR3、LP DDR、SDRAM,適用于需配備4Gb 或以下容量DRAM 的應用,?如人工智能加速器、物聯(lián)網(wǎng)、汽車、工業(yè)用、電信、

2022-04-20 16:04:03 2554

2554

DDR內(nèi)存1代已經(jīng)淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 2871

2871

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內(nèi)存下部設(shè)計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設(shè)計可以保證金手指和內(nèi)存插槽有足夠的接觸面

2023-09-19 14:49:44 1485

1485

描述此參考設(shè)計展示了適用于 DDR3 和 DDR4 存儲器的通用電源解決方案。同步降壓轉(zhuǎn)換器為 DDR3L 配置中的 9A 負載提供 1.35V 輸出電壓。線性穩(wěn)壓器提供為 2A 負載提供

2018-12-24 15:08:56

外部內(nèi)存。3.使用DDR3內(nèi)存控制器3.1. 連接DDR3內(nèi)存控制器到DDR3 SDRAM圖11,圖12,圖13表示三種內(nèi)存拓撲圖。圖11 2個16MB*16*8BANK(4Gb)圖12 1個8MB

2018-01-18 22:04:33

嗨論壇社區(qū),我使用的是XC7K420T-2FFG1156 7系列FPGA,這里所有的銀行都是HR銀行。我想將4 GB DDR3連接到FPGA。我提到了xilinx EVM套件,其中DDR3與HP

2020-08-25 07:48:37

嗨,我是FPGA領(lǐng)域的新手。現(xiàn)在我正在使用Genesys2。我必須控制DDR3內(nèi)存。我在Digilent網(wǎng)站上找到了一些使用micrlaze處理器的DDR3示例。但是,在我的情況下,我不必

2019-05-05 15:29:38

還未接觸過DDR4,在LAYOUT顆粒設(shè)計中,布局布線上DDR3與DDR4有沒有區(qū)別?有哪些區(qū)別?

2019-03-07 10:11:39

DDR4 SDRAM的尋址方式有哪些?

2021-10-27 06:50:24

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

DDR4 SDRAM結(jié)構(gòu)和尋址DDR4 SDRAM的封裝和尋址新的改變功能快捷鍵合理的創(chuàng)建標題,有助于目錄的生成如何改變文本的樣式插入鏈接與圖片如何插入一段漂亮的代碼片生成一個適合你的列表創(chuàng)建一個

2021-07-29 06:58:22

(UG583)“UltraScale架構(gòu)PCB設(shè)計用戶指南”的V1.10表示(通常)DDR4接口信號reset_n不需要滿足適用于地址/命令/控制組中其他信號的偏移約束。但是,在專門引用DDR4

2020-08-27 17:10:06

DDR4就一定比DDR3好嗎?

2021-06-18 06:22:29

DDR4相比DDR3的相關(guān)變更點相比DDR3,DDR4存在諸多變更點,其中與硬件設(shè)計直接相關(guān)的變更點主要有:?增加Vpp電源;?VREFDQ刪除;?CMD、ADD、CTRL命令的端接變更為POD模式

2021-11-12 08:07:07

://blog.csdn.net/qq_42682826/article/details/102970701DDR4相比DDR3的相關(guān)變更點相比DDR3,DDR4存在諸多變更點,其中與硬件設(shè)計直接相關(guān)

2019-11-12 12:40:17

的新芯片-熊湖(Bear Lake),其將支持DDR3規(guī)格,而AMD也預計同時在K9平臺上支持DDR2及DDR3兩種規(guī)格。 DDR4 DDR4內(nèi)存峰會 據(jù)介紹美國JEDEC將會在不久之后啟動

2011-02-27 16:47:17

通過調(diào)整每byte的時序來補償走線擺率。目前的FPGA在連接雙倍速SDRAM內(nèi)存時都有很多功能,但是如何與最新的DDR3連接還需要一個新的調(diào)整方案。FPGA I/O結(jié)構(gòu)高性能的Altera

2019-04-22 07:00:08

如果沒有將均衡功能直接設(shè)計到FPGA I/O架構(gòu)中,那么任何設(shè)備連接到DDR3 SDRAM DIMM都將是復雜的,而且成本還高,需要大量的外部元器件,包括延時線和相關(guān)的控制。

2019-08-21 07:21:29

FPGA如何對引腳進行分塊?是由VCC的電壓不同進行自行設(shè)計分塊?還是每個塊的引腳都是固定的?在進行DDR3與FPGA的硬件連接時,由FPGA的芯片手冊得采用SSTL_15電壓標準,即VDDQ

2021-11-29 16:10:48

支持Xilinx FPGA中的32位 DDR4 SDRAM

2020-12-29 06:30:15

嗨,我正在嘗試在Kintex UltraScale(KCU105)中實現(xiàn)DDR4內(nèi)存,但是(DDR4 SDRAM(MIG))中的特定部分不可用。部分是:MT401G16HBA-083E:我應該為實現(xiàn)這個內(nèi)存做什么。?注意:我正在使用VIVADO 2016.1謝謝Luis。

2020-04-26 13:58:08

東莞專業(yè)收購DDR4東莞長期高價回收DDR4,專業(yè)收購DDR4,深圳帝歐電子長期現(xiàn)金高價回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-05-08 17:42:19

(CPU或FPGA)不停的發(fā)送不同時延的DQS 信號,DDR3 SDRAM 顆粒在DQS-DQS#的上升沿采樣CK 的狀態(tài),并通過DQ 線反饋給DDR3 控制器。控制器端反復的調(diào)整DQS-DQS#的延時

2022-12-16 17:01:46

仍不知道DDR3和DDR4這兩種規(guī)格的區(qū)別,以至于買回來的硬件并不兼容。下面和宏旺半導體一起來看一下DDR3和DDR4到底有哪些差別。DDR3是一種計算機內(nèi)存規(guī)格,它屬于SDRAM家族的內(nèi)存產(chǎn)品,提供

2019-07-25 14:08:13

SDRAM ):DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的頻寬,DDR4的傳輸速率目前可達2133~3200 MT/s。DDR4 新增了4 個Bank Group 資料組

2019-08-01 10:17:46

佛山回收DDR4高價回收DDR4,佛山專業(yè)收購DDR4,深圳帝歐電子長期現(xiàn)金高價回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-07-15 19:36:21

佛山回收DDR4高價回收DDR4,佛山專業(yè)收購DDR4,深圳帝歐電子長期現(xiàn)金高價回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-12-27 19:25:08

你好我正在使用新版ML605板當我測試DDR3時,它失敗了我在xilinx論壇上找到“ML605 - SO DIMM附帶更新的版本”并更改MHS文件和UCF文件,但是當我嘗試運行它時,會出現(xiàn)兩個錯誤

2019-09-17 11:15:30

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數(shù)據(jù)流緩存的實現(xiàn)提供便利。系統(tǒng)測試表明,該

2018-08-02 09:34:58

時,DDR2對信號完整性[4]的要求比較高,在很多地方都要求T型連接;而DDR3引入了write leveling的模塊[5],專門用于各個模塊間時鐘的對齊,因此可以采用菊花鏈的連接方式,大大方便了PCB

2018-08-30 09:59:01

本手冊以 DDR3 器件為例講解硬件設(shè)計方法,包括 FPGA I/O 分配、原理圖設(shè)計、電源網(wǎng)絡(luò)設(shè)計、PCB 走線、參考平面設(shè)計、仿真等,旨在協(xié)助用戶快速完成信號完整性好、低功耗、低噪聲的高速存儲

2022-09-29 06:15:25

均衡的定義和重要性是什么如何實現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設(shè)計?

2021-05-07 06:21:53

由于系統(tǒng)帶寬不斷的增加,因此針對更高的速度和性能,設(shè)計人員對存儲技術(shù)進行了優(yōu)化。下一代雙數(shù)據(jù)速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優(yōu)勢。這些

2019-08-09 07:42:01

嗨,我是jongbum。目前,MIG UltraScale DDR4支持最高2級。https://forums.xilinx.com/t5/Memory-Interfaces

2020-04-22 08:36:21

嗨,我正在尋找一款價格合理的Zynq Ultrascale +主板,其中DDR4接口連接到PL。我想使用一個軟核內(nèi)存控制器。問候,Mosfa

2019-10-17 08:45:37

嗨,任何1可以幫我寫一個代碼,用于連接DDR3 SDRAM內(nèi)存和Virtex6 fpga。實際上我有一個小疑問,通過MIG我可以為此生成代碼。如果不是如何繼續(xù)這個我對這個PLZ幫助我。謝謝以上

2019-02-15 06:36:48

嗨,我即將使用Virtex-4QV設(shè)備(XQR4VFX140)開始一個新項目。雖然我對使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些經(jīng)驗,但我發(fā)現(xiàn)MIG IP不支持VIRTEX-4QV器件。那可能是另類?如何將DDR2 SDRAM與此FPGA連接?彌敦道

2020-04-02 06:08:46

本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別文所有權(quán)歸作者Aircity所有1什么是DDRDDR是Double Data Rate的縮寫,即“雙比特翻轉(zhuǎn)”。DDR是一種技術(shù),中國大陸工程師

2021-09-14 09:04:30

深圳專業(yè)收購DDR4深圳長期高價回收DDR4,專業(yè)收購DDR4,深圳帝歐電子長期現(xiàn)金高價回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-01-30 17:36:35

怎么用FPGA檢測內(nèi)存條DDR4壞的單元數(shù)呢?1.我可以用一個僅支持DDR3的memory controllor的FPGA和作為一個平臺嗎?(有人說只需設(shè)置下FPGA就可以,不知道是不是這樣的)2.

2016-09-28 14:35:54

本帖最后由 dealicdz 于 2021-3-30 15:41 編輯

蘇州專業(yè)收購DDR4曉色又侵窗紙。窗外雞聲初起。蘇州長期高價回收DDR4,專業(yè)收購DDR4,深圳帝歐電子長期現(xiàn)金高價回收

2021-03-17 17:59:10

DDR4和DDR3的區(qū)別在哪里?DDR4內(nèi)存與DDR3內(nèi)存相比,有哪些優(yōu)勢呢?

2021-06-18 08:58:23

PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

適用于Xilinx Virtex-7 FPGA開發(fā)板的32位DDR4 SDRAM

2020-12-30 07:39:14

本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計思想,分析了各模塊功能與設(shè)計注意事項,并

2010-07-30 17:13:55 30

30 不只計算機存儲器系統(tǒng)一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統(tǒng)應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 DDR4,什么是DDR4

DDR 又稱雙倍速率SDRAM Dual Date Rate SDRSM DDR SDRAM 是一種高速CMOS動態(tài)隨即訪問的內(nèi)存美國JEDEC 的固態(tài)技術(shù)協(xié)會于2000 年6 月公

2010-03-24 16:08:39 3146

3146 從那時起,采用DDR2、甚至最新的DDR3 SDRAM的新設(shè)計讓DDR SDRAM技術(shù)黯然失色。DDR內(nèi)存主要以IC或模塊的形式出現(xiàn)。如今,DDR4雛形初現(xiàn)。但是在我們利用這些新技術(shù)前,設(shè)計人員必須了解如何

2011-07-11 11:17:14 5033

5033

SDRAM, DDR, DDR2, DDR3 是RAM 技術(shù)發(fā)展的不同階段, 對于嵌入式系統(tǒng)來說, SDRAM 常用在低端, 對速率要求不高的場合, 而在DDR/DDR2/DDR3 中,目前基本上已經(jīng)以DDR2 為主導,相信不久DDR3 將全面取代

2012-01-16 14:53:01 0

0 本內(nèi)容主要分析了基于FPGA的系統(tǒng)需求,賽靈思UltraScale FPGA DDR4和其他并行接口分析以及針對高性能高度靈活方案的PHY解決方案介紹。

2016-08-03 19:37:24 190

190 應用于賽靈思UltraScale All Programmable FPGA上。接口設(shè)計將DDR SDRAM提升至2400Mbps甚至以上,同時降低接口功耗。為了達到這個目標,賽靈思的工程師們必須

2017-02-08 14:03:01 608

608 ? 和 ?Xilinx Ehab Mohsen? 聊到了將 ?DDR4? 與 ?Xilinx UltraScale? FPGA? 相結(jié)合可實現(xiàn)的驚人性能優(yōu)勢和功能。 立即觀看在線座談 ??

2017-02-09 06:18:33 470

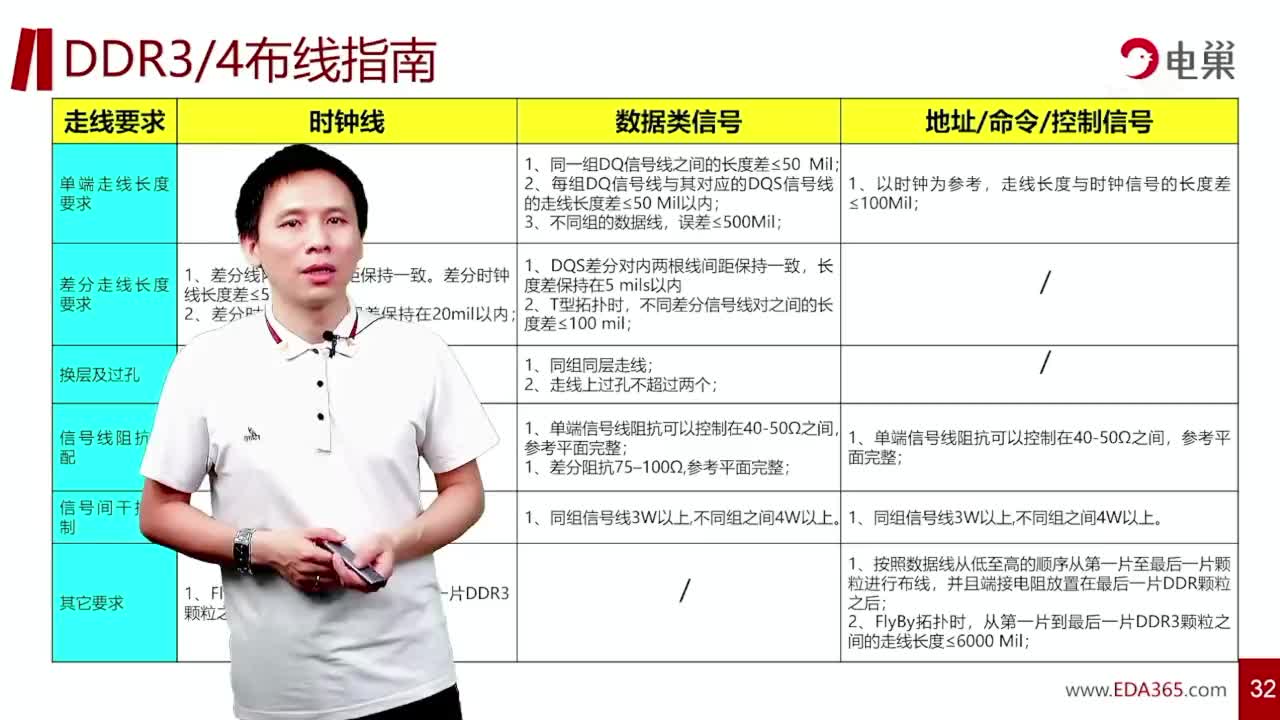

470 DDR2_DDR3_SDRAM,PCB布線規(guī)則指導

2017-10-31 10:06:48 78

78 DDR~DDR3的設(shè)計指導手冊

2017-11-02 17:02:11 0

0 DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達2133~3200MT/s。DDR4 新增了4 個Bank Group 數(shù)據(jù)組的設(shè)計,各個Bank

2017-11-07 10:48:51 52790

52790

雖然新一代電腦/智能手機用上了DDR4內(nèi)存,但以往的產(chǎn)品大多還是用的DDR3內(nèi)存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們再來看看DDR4和DDR3內(nèi)存都有哪些區(qū)別。相比上一代DDR3,新一代DDR4內(nèi)存主要有以下幾項核心改變:

2017-11-08 15:42:23 30896

30896 DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動態(tài)隨機存取內(nèi)存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 為了滿足高速圖像數(shù)據(jù)采集系統(tǒng)中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設(shè)計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

DRAM (動態(tài)隨機訪問存儲器)對設(shè)計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統(tǒng)的存儲系統(tǒng)設(shè)計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、DDR5 SDRAM、LPDDR、GDDR。

2018-12-19 08:00:00 76

76 DDR3 SDRAM是DDR3的全稱,它針對Intel新型芯片的一代內(nèi)存技術(shù)(但目前主要用于顯卡內(nèi)存),頻率在800M以上。DDR3是在DDR2基礎(chǔ)上采用的新型設(shè)計,與DDR2 SDRAM相比具有功耗和發(fā)熱量較小、工作頻率更高、降低顯卡整體成本、通用性好的優(yōu)勢。

2019-10-29 08:00:00 0

0 從成本的角度來看,DDR3也許的確要比DDR4低一些,所以從這個角度可以講通。

2020-09-08 16:28:23 4062

4062 本篇主要針對Zynq UltraScale + MPSoC的DDR接口,從硬件設(shè)計的角度進行詳細介紹,最后展示一下小編之前自己設(shè)計的基于ZU+的外掛8顆DDR4的設(shè)計。

2020-12-28 08:00:00 0

0 是DDR4和DDR3,其他系列相對使用較少一些,本文主要以DDR4進行介紹。 1、選型 根據(jù)ZU+系列芯片的數(shù)據(jù)手冊、TRM、pg150等文檔,DDR可以掛載在PS側(cè),也可以掛載在PL側(cè),也可同時掛載在PS

2021-09-16 10:17:02 4789

4789

DDR4相比DDR3的相關(guān)變更點相比DDR3,DDR4存在諸多變更點,其中與硬件設(shè)計直接相關(guān)的變更點主要有:? 增加Vpp電源;? VREFDQ刪除;? CMD、ADD、CTRL命令的端接變更為

2021-11-06 20:36:00 28

28 DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別作者:AirCity 2019.12.17Aircity007@sina.com 本文所有權(quán)歸作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 154

154 本文檔定義了DDR4 SDRAM規(guī)范,包括特性、功能、交流和直流特性、封裝和球/信號分配。本標準旨在定義符合JEDEC 2 Gb的最低要求x4、x8和x16 DDR4 SDRAM設(shè)備通過16 Gb

2022-11-29 10:00:17 20

20 8Gb DDR4 SDRAM B裸片組織為128Mbit x 4 I/O x16banks或64Mbit x8 I/O x 16banks設(shè)備。此同步設(shè)備實現(xiàn)高達2666Mb/sec的高速雙數(shù)

2022-12-05 11:54:24 11

11 DDR3 SDRAM使用雙倍數(shù)據(jù)速率架構(gòu)來實現(xiàn)高速操作。雙倍數(shù)據(jù)速率結(jié)構(gòu)是一種8n預取架構(gòu),其接口經(jīng)過設(shè)計,可在I/O引腳上每個時鐘周期傳輸兩個數(shù)據(jù)字。

DDR3 SDRAM的單個讀或?qū)懖僮饔行У匕?/div>

2023-02-06 10:12:00 3

3 電子發(fā)燒友網(wǎng)站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用.pdf》資料免費下載

2023-07-24 09:50:47 0

0 本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現(xiàn)讀寫操作。

2023-09-01 16:23:19 745

745

摘要:本文將對DDR3和DDR4兩種內(nèi)存技術(shù)進行詳細的比較,分析它們的技術(shù)特性、性能差異以及適用場景。通過對比這兩種內(nèi)存技術(shù),為讀者在購買和使用內(nèi)存產(chǎn)品時提供參考依據(jù)。

2023-09-27 17:42:10 1089

1089 是目前使用最為廣泛的計算機內(nèi)存標準,它已經(jīng)服務了計算機用戶多年。但是,DDR4內(nèi)存隨著技術(shù)的進步,成為了更好的內(nèi)存選擇。本文將詳細介紹DDR4和DDR3內(nèi)存的各種區(qū)別。 1. 工作頻率 DDR3內(nèi)存的標準工作頻率為1600MHz,而DDR4內(nèi)存標準則為2133MHz。這意味著DDR4內(nèi)存的傳輸速度

2023-10-30 09:22:00 3905

3905 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論