通過(guò)上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過(guò)以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 1032

1032

Xilinx7系列普及講座內(nèi)容請(qǐng)下載附件pdf,更多內(nèi)容請(qǐng)登錄www.rocetech.com

2013-03-31 14:09:45

Xilinx7系列普及講座內(nèi)容請(qǐng)下載附件pdf,更多內(nèi)容請(qǐng)登錄www.rocetech.com

2013-03-31 14:20:25

Xilinx7系列普及講座內(nèi)容請(qǐng)下載附件pdf,更多內(nèi)容請(qǐng)登錄www.rocetech.com

2013-03-31 14:27:04

7系列FPGA DSP48E1片的特點(diǎn)什么

2021-03-05 06:26:41

嗨論壇社區(qū),我使用的是XC7K420T-2FFG1156 7系列FPGA,這里所有的銀行都是HR銀行。我想將4 GB DDR3連接到FPGA。我提到了xilinx EVM套件,其中DDR3與HP

2020-08-25 07:48:37

我必須對(duì)7系列FPGA特別是Kintex 7封裝676提出一個(gè)愚蠢的問(wèn)題.DS182建議第6頁(yè)上的電源排序。沒(méi)問(wèn)題,謝謝。第7頁(yè)談到了坡道時(shí)間。但是我想用我的FPGA使用FMC夾層板,現(xiàn)在Vadj

2020-08-18 09:51:02

7系列FPGA數(shù)據(jù)手冊(cè):概述------中文版總體介紹7系列FPGA功能摘要Spartan-7系列FPGA功能摘要總體介紹Xilinx?7系列FPGA包括四個(gè)系列(Spartan?,Artix?-7

2021-07-26 08:06:53

走近Xilinx的FPGA 7系列芯片,從全新FPGA 7系列芯片的介紹、芯片優(yōu)點(diǎn)、芯片典型應(yīng)用以及芯片未來(lái)展望等方面,深入闡述工程師選擇Xilinx FPGA芯片的理由。 理由1 業(yè)界性價(jià)比之王

2012-09-21 13:46:16

,ALTERA,LATTICE,國(guó)產(chǎn) 。它們內(nèi)部架構(gòu)以及開(kāi)發(fā)軟件,其實(shí)都大同小異,一通則百通),講解硬件描述語(yǔ)言是如何與內(nèi)部單元和連線一一對(duì)應(yīng)的。一般而言,FPGA內(nèi)部(圖1 XILINX A7系列

2020-06-23 23:52:00

各路大神你們好!我想向各位咨詢下:當(dāng)采用BPI模式配置Xilinx V7系列FPGA時(shí),程序是如何下載到BPI FLASH中去的?我看了V7的配置技術(shù)手冊(cè),發(fā)現(xiàn)里面只介紹了一種間接編程方式:由

2015-08-26 15:34:44

Xilinx 7系列FPGA簡(jiǎn)介--選型參考

2021-02-01 06:10:55

,支持最大1.8V的I/O信號(hào),HR主要為了支持更廣泛的I/O標(biāo)準(zhǔn),支持最大3.3V的I/O信號(hào)。 Xilinx 7系列FPGA的HR和HP bank,每個(gè)bank有50個(gè)I/O管腳,每個(gè)I/O管腳

2020-12-23 17:17:47

引言: 我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開(kāi)發(fā)人員提供使用。通過(guò)本文,可以了解到

2021-05-28 09:23:25

引言: 我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開(kāi)發(fā)人員提供使用。通過(guò)本文,可以了解到

2021-07-08 08:00:00

Xilinx Artix-7 FPGA快速入門(mén)、技巧與實(shí)例連載7——FPGA開(kāi)發(fā)技能更多資料共享鏈接:https://share.weiyun.com/53UnQas在FPGA技術(shù)的應(yīng)用領(lǐng)域不斷擴(kuò)展

2019-04-10 14:58:20

前言TLK7-EVM是一款由廣州創(chuàng)龍基于Xilinx Kintex-7系列FPGA自主研發(fā)的核心板+底板方式的開(kāi)發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅80mm*58mm,底板采用沉金無(wú)鉛工藝的6

2020-09-24 14:39:36

描述PMP10601 參考設(shè)計(jì)提供為 Xilinx? Zynq? 7000 系列 (XC7Z015) FPGA供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、多個(gè) LDO 和一個(gè) DDR

2018-07-13 03:11:34

? Zynq? 7000 series (XC7Z045)FPGA.This design uses several LMZ3 series modules, LDOs, and a DDR

2018-11-05 16:42:31

`描述PMP10600.2 參考設(shè)計(jì)提供為 Xilinx? Zynq? 7000 系列 (XC7Z015) FPGA 供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、多個(gè) LDO 和一個(gè)

2015-05-08 16:17:26

`描述PMP10601 參考設(shè)計(jì)提供為 Xilinx? Zynq? 7000 系列 (XC7Z015) FPGA 供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、多個(gè) LDO 和一個(gè)

2015-05-08 16:08:58

描述 PMP10601 參考設(shè)計(jì)提供為 Xilinx? Zynq? 7000 系列 (XC7Z015) FPGA供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、多個(gè) LDO 和一個(gè)

2022-09-28 06:24:34

Xilinx_A7_K7_V7系列Cadence符號(hào)庫(kù)及PCB庫(kù)

2021-01-28 06:39:41

xilinx公司的7系列FPGA應(yīng)用指南

2012-08-14 12:17:40

嗨,我們的設(shè)計(jì)中有kintex 7系列芯片,顯示出“RX鎖定失敗”問(wèn)題。這種情況發(fā)生在20塊板上的3塊板上。由于這個(gè)錯(cuò)誤,從Xilinx到MAC的端口之一總是關(guān)閉,而其他鏈接很好。任何想到的原因是

2019-04-08 13:08:22

核心板簡(jiǎn)介基于Xilinx Kintex-7系列FPGA處理器;FPGA芯片型號(hào)為XC7K325T-2FFG676I,兼容XC7K160T/410T-2FFG676I,NOR FLASH

2020-09-18 09:57:03

1.開(kāi)發(fā)板簡(jiǎn)介基于Xilinx Artix-7系列FPGA處理器;FPGA芯片型號(hào)為XC7A100T-2FGG484I,NOR FLASH 256Mbit,DDR3 512M/1GByte可選,兼容

2020-09-04 11:33:24

前言TLK7-EVM是一款由廣州創(chuàng)龍基于Xilinx Kintex-7系列FPGA自主研發(fā)的核心板+底板方式的開(kāi)發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅80mm*58mm,底板采用沉金無(wú)鉛工藝的6

2020-09-24 16:46:18

TLK7-EVM是一款由廣州創(chuàng)龍基于Xilinx Kintex-7系列FPGA自主研發(fā)的核心板+底板方式的開(kāi)發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅80mm*58mm,底板采用沉金無(wú)鉛工藝的6層板

2020-09-16 10:40:31

在社區(qū),Zedboad(7系列)所需的電壓是多少,我的意思是整個(gè)芯片?或高級(jí)FPGA所需的最低電壓?謝謝你盡快回復(fù)問(wèn)候

2019-10-17 09:07:37

能夠符合Xilinx最新的工具軟件和器件系列,因此選擇7系列FPGA作為原型平臺(tái)。經(jīng)朋友推薦,本開(kāi)發(fā)板復(fù)雜度適中,學(xué)習(xí)開(kāi)發(fā),因此特申請(qǐng)使用該開(kāi)發(fā)板進(jìn)行學(xué)習(xí)開(kāi)發(fā)相應(yīng)的資料教程。本人擬從以下幾個(gè)方面展開(kāi)試用

2016-10-11 18:15:20

調(diào)研Xilinx推出的7系列產(chǎn)品,以及板卡的相關(guān)資源。2、簡(jiǎn)單介紹FPGA設(shè)計(jì)流程,以及相關(guān)Verilog HDL的語(yǔ)法。3、進(jìn)行相關(guān)實(shí)驗(yàn)設(shè)計(jì):數(shù)字邏輯->時(shí)序邏輯-&

2016-11-10 12:34:54

提供了工業(yè)最先進(jìn)的FPGA,而且還開(kāi)發(fā)了改變編程規(guī)則的完全可編程SoC和3D IC系列產(chǎn)品。NI在幫助定義Xilinx 7系列器件的要求上也發(fā)揮了關(guān)鍵作用。 Xilinx 7系列的一個(gè)主要

2016-12-21 10:56:25

引腳,該供電為該bank的輸入和輸出管腳供電。 收發(fā)器Artix-7系列FPGA有高達(dá)16個(gè)收發(fā)器,其速率為6.6G/s。同時(shí)片上集成一個(gè)PCIeGen2的硬核,可以配合收發(fā)器實(shí)現(xiàn)PCIE主機(jī)或從機(jī)

2016-11-01 15:52:18

Xilinx Kintex-7 XC7K325T-2FFG676I嵌入式核心板簡(jiǎn)介圖 1Xilinx Kintex-7核心板簡(jiǎn)介創(chuàng)龍科技SOM-TLK7是一款基于Xilinx Kintex-7系列

2021-12-20 06:47:57

引言:本文我們介紹Xilinx 7系列FPGA收發(fā)器硬件設(shè)計(jì)主要注意的一些問(wèn)題,指導(dǎo)硬件設(shè)計(jì)人員進(jìn)行原理圖及PCB設(shè)計(jì)。本文介紹以下內(nèi)容:GTX/GTH收發(fā)器管腳概述GTX/GTH收發(fā)器時(shí)鐘

2021-11-11 07:42:37

175MSPS*12Bit 高速高精度DAC,配備高性能的Xilinx Artix-7系列FPGA可進(jìn)行高速數(shù)據(jù)轉(zhuǎn)換和時(shí)序控制。TL-A7HSAD高速數(shù)據(jù)采集卡完全支持PCI Express 2.0標(biāo)準(zhǔn)

2016-08-24 15:01:21

Artix-7 FPGA,最高可支持配備雙核Arm Cortex-A9 處理器。由于其設(shè)計(jì)可擴(kuò)展且與 Xilinx 系列設(shè)備非常相似,所以該參考設(shè)計(jì)基于 Xilinx Zynq UltraScale+

2019-01-03 13:47:48

本文基于創(chuàng)龍科技TLK7-EVM評(píng)估板進(jìn)行SDI視頻輸入/輸出案例演示。TLK7-EVM是一款基于Xilinx Kintex-7系列FPGA設(shè)計(jì)的高端評(píng)估板,由核心板和評(píng)估底板組成。核心板經(jīng)過(guò)專業(yè)

2021-02-01 16:08:30

前言TLA7-EVM開(kāi)發(fā)板是一款由廣州創(chuàng)龍基于Xilinx Artix-7系列FPGA自主研發(fā)的核心板+底板方式的開(kāi)發(fā)板,可快速評(píng)估FPGA性能。核心板尺寸僅70mm*50mm,底板采用沉金無(wú)鉛工藝

2020-09-23 16:27:12

基于Xilinx Kintex-7 FPGA K7 XC7K325T PCIeX8 四路光纖卡1. 板卡概述 板卡主芯片采用Xilinx公司的XC7K325T-2FFG900 FPGA

2015-01-28 15:48:55

`基于Xilinx Kintex-7系列FPGA高端設(shè)計(jì)的TLK7-EVM評(píng)估板簡(jiǎn)介 TLK7-EVM評(píng)估板簡(jiǎn)介創(chuàng)龍科技TLK7-EVM是一款基于XilinxKintex-7系列FPGA設(shè)計(jì)的高端

2020-11-24 11:31:51

據(jù)我所知,Xilinx建議采用SEM來(lái)減輕SEU對(duì)7系列FPGA的影響。但Artix-7 FPGA不支持ISE 14.2中的SEM,這與Xilinx的建議(http://www.xilinx

2020-07-14 07:01:12

親愛(ài)的論壇,我們面臨著Xilinx Kinetix-7 FPGA非常奇怪的行為。所以問(wèn)題如下:我們合成了RTL并將其加載到FPGA中。當(dāng)我們打開(kāi)bord時(shí),FPGA工作正常!幾分鐘后(約5-7分鐘

2019-11-07 09:38:56

1.工藝節(jié)點(diǎn) 首先不管選擇什么廠家的產(chǎn)品,都建議在其主流產(chǎn)品中選擇合適的芯片。 以上是目前 Xilinx 主流的也是常用的幾個(gè) FPGA 產(chǎn)品系列,這里不談傳說(shuō)中的后兩個(gè)系列

2020-12-23 17:21:03

嗨!是否有可能不為7系列FPGA上的HP / HR庫(kù)供電? GTX怎么樣?

2020-03-18 07:46:17

7系列有多少BUFG?我從報(bào)告中讀到有128個(gè),這是正確答案嗎?

2020-08-25 15:49:16

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 編輯

你好!我目前正在實(shí)現(xiàn)6657DSP 評(píng)估板與xilinx kintex7 FPGA之間的PCIE連接,其中DSP作為Root

2018-06-25 05:14:40

嗨,我似乎無(wú)法在任何地方找到有關(guān)7系列硬件的目標(biāo)發(fā)布日期的信息(或者如果它們已經(jīng)發(fā)布)。特別是,當(dāng)我可以獲得Zynq或任何7系列fpgas的開(kāi)發(fā)板時(shí),我很想知道。謝謝。

2019-08-28 10:51:52

本帖最后由 一只耳朵怪 于 2018-6-21 09:55 編輯

誰(shuí)有FPGA 7系列的原理圖封裝

2018-06-21 02:14:39

賽靈思(XILINX)全新7系列FPGA詳述

2012-08-14 12:20:22

描述Xilinx chose TI as the power solution vendor to power Virtex 7 FPGA (along with other analog

2018-08-13 06:31:38

適用于Xilinx Virtex-7 FPGA開(kāi)發(fā)板的32位DDR4 SDRAM

2020-12-30 07:39:14

電子發(fā)燒友網(wǎng)訊:賽靈思FPGA 7系列芯片正以燎原之勢(shì)席卷整個(gè)行業(yè)。在本文,電子發(fā)燒友網(wǎng)小編將帶領(lǐng)大家一起走近Xilinx的FPGA 7系列芯片,從全新FPGA 7系列芯片的介紹、芯片優(yōu)點(diǎn)、芯片

2012-09-06 16:24:35

GX-FPGA-XC7A100T-SOM是北京革新創(chuàng)展科技有限公司開(kāi)發(fā)的一款基于XILINX ARTIX-7系列FGG484封裝類型的芯片而開(kāi)發(fā)的高性能核心板。核心板具有高速度、高帶寬、高容量等特點(diǎn)

2022-03-09 11:33:24

XC7A50T-1FGG484C FPGA可編程邏輯器件XILINX/賽靈思ALINX SoM AC7A50T,基于Artix-7 XC7A50T-1FGG484C,由FPGA + 2 DDR3

2022-06-17 17:53:59

XC7K160T-2FFG676I 一般說(shuō)明Xilinx?7系列FPGA由四個(gè)FPGA系列組成,它們滿足了從低成本、小尺寸到,成本敏感的高容量應(yīng)用程序,以超高端連接帶寬、邏輯容量和信號(hào)

2022-08-03 14:13:24

產(chǎn)品概述產(chǎn)品型號(hào) XC7K410T-2FFG900C描述IC FPGA 500 I/O 900FCBGA分類集成電路(IC),嵌入式-FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)制造商Xilinx公司系列

2022-08-04 11:20:31

Xilinx?7系列FPGA由四個(gè)FPGA系列組成,可滿足各種系統(tǒng)要求,從低成本、小尺寸、成本敏感的高容量應(yīng)用到超高端連接帶寬、邏輯容量和信號(hào)處理能力,以滿足最苛刻的高性能應(yīng)用

2022-08-30 17:04:09

Xilinx?7系列FPGA包括四個(gè)FPGA系列,可滿足整個(gè)系統(tǒng)要求,包括低成本,小尺寸,成本敏感的大批量應(yīng)用程序,可滿足最苛刻的超高端連接帶寬,邏輯容量和信號(hào)處理能力高性能的應(yīng)用程序。7系列

2022-11-10 15:11:11

FPGA, Artix-7, MMCM, PLL, 400 I/O, 628 MHz, 215360單元, 950 mV至1.05 V, FCBGA-676XILINX Artix?-7

2022-11-10 15:13:15

XC7K160T-2FFG676I 一般說(shuō)明Xilinx?7系列FPGA由四個(gè)FPGA系列組成,它們滿足了從低成本、小尺寸到,成本敏感的高容量應(yīng)用程序,以超高端連接帶寬、邏輯容量和信號(hào)處理能力滿足

2022-12-19 14:35:48

FPGA, Artix-7, MMCM, PLL, 285 I/O, 628 MHz, 101440單元, 950 mV至1.05 V, FBGA-484Xilinx Artix?-7 FPGA系列

2023-05-10 16:03:24

Xilinx擴(kuò)展Spartan-3A FPGA系列,降低大容量成本敏感應(yīng)用系統(tǒng)總成本

賽靈思公司宣布,作為Spartan-3A FPGA系列平臺(tái)延伸的小封裝FPGA正式量產(chǎn)。這些小封裝FPGA在提供突破性價(jià)位的同

2008-09-02 08:50:17 643

643 本文是關(guān)于 xilinx公司的7系列FPGA應(yīng)用指南。xilinx公司的7系列FPGA包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對(duì)這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對(duì)比表

2012-08-07 17:22:55 201

201 全新賽靈思(Xilinx)FPGA 7系列芯片精彩剖析:賽靈思的最新7系列FPGA芯片包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。在介紹芯片之前,先看看三個(gè)子系列芯片的介紹表,如下表1所示: 表

2012-08-08 15:04:04 395

395 Xilinx FPGA系列入門(mén)教程(二)——Xilinx FPAG開(kāi)發(fā)環(huán)境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入門(mén)教程(一)——如何搭建Xilinx FPGA開(kāi)發(fā)環(huán)境

2016-01-18 15:30:32 45

45 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 上圖中的FIR濾波器的結(jié)構(gòu)被叫做轉(zhuǎn)置型I的濾波器,并且使用了流水線。這種架構(gòu)使用了級(jí)聯(lián)的方式,充分利用了DSP Slice的結(jié)構(gòu)。 這個(gè)例子顯示了一個(gè)小的4抽頭濾波器。輸入數(shù)據(jù)通過(guò)左側(cè)流水線被送到的DSP Slice中,級(jí)聯(lián)后把數(shù)據(jù)延時(shí)送到下一級(jí)中。每個(gè)DSP slice里面的乘法器將數(shù)據(jù)和正確的系數(shù)進(jìn)行相乘,在加法器中相加后輸出,經(jīng)過(guò)流水線并最終級(jí)聯(lián)在最右端輸出最終的結(jié)果。從這個(gè)例子中,可以清晰的看到FIR濾波器的抽頭即使增加了,可以很簡(jiǎn)單的

2017-02-08 05:37:02 65

65

用戶必須要認(rèn)識(shí)到,學(xué)習(xí)一下技巧可以讓更多的邏輯放在更少的Slice中,使工具能夠達(dá)到既實(shí)現(xiàn)設(shè)計(jì)時(shí)序要求又滿足用戶對(duì)功耗的要求。而現(xiàn)在很多用戶缺乏代碼編寫(xiě)的想法,編寫(xiě)出一個(gè)有時(shí)序問(wèn)題的設(shè)計(jì)。為了滿足要求,就會(huì)不停修改,再綜合再布局布線來(lái)滿足自己的時(shí)序目標(biāo)。其實(shí),他們需要的是重新評(píng)估他們的HDL代碼技術(shù)以及他們的控制信號(hào)。 例如,如何使用這些D觸發(fā)器呢?首先說(shuō)明幾個(gè)概念: 所有觸發(fā)器為D類型,所有的觸發(fā)器具有一個(gè)時(shí)鐘

2017-02-08 06:32:06 100

100 下面這個(gè)例子說(shuō)明在用戶的Flip-Flops設(shè)置初始值。大多數(shù)設(shè)計(jì)師這樣寫(xiě)代碼為的是仿真能夠更加簡(jiǎn)便。否則當(dāng)用戶開(kāi)始運(yùn)行仿真的時(shí)候,用戶設(shè)計(jì)中使用的寄存器等都處于一個(gè)不確定態(tài)。可以,按照例子來(lái)寫(xiě)的代碼,可以讓寄存器等有一個(gè)確定的初始值,處于一個(gè)確定態(tài)。 reg Q =1’b1; always @ (posedge CLK or posedge RST ) begin if (RST) Q = 1’b0; else Q = D; end signal Q: std_logic:=‘1’; FF: process (CLK, RST) begin if (RST = ‘1’) then Q = ‘0’; elsif (rising_edge CLK) then Q = D; end if; en

2017-02-08 06:33:11 216

216

,這兩個(gè)寄存器可以被放置在同一個(gè)Slice里面。在VIVADO和ISE下面都有選項(xiàng)來(lái)幫助大家自動(dòng)實(shí)現(xiàn)該功能。大家在做設(shè)計(jì)的時(shí)候可以選用。 做設(shè)計(jì)的時(shí)候有些原則還應(yīng)該注意: 在控制信號(hào)的規(guī)劃的時(shí)候,XILINX的原語(yǔ)和IP的例化可能增加額外的控制信號(hào)到用

2017-02-08 06:35:36 146

146

Reset分為全局Reset和局部Reset。全局Reset可以讓所有存儲(chǔ)類的元素處于一個(gè)已知的狀態(tài)。全局的Reset一般是通過(guò)外部的引腳或者一個(gè)標(biāo)準(zhǔn)進(jìn)程的完成或者等待PLL/MMCM鎖定信號(hào)的有效來(lái)實(shí)現(xiàn)的。局部復(fù)位一般是有內(nèi)部信號(hào)產(chǎn)生,他是讓一些存儲(chǔ)類的元素處于一個(gè)已知的狀態(tài),如利用內(nèi)部的計(jì)數(shù)器。一般來(lái)說(shuō)局部復(fù)位都是同步信號(hào)。 Reset又分為同步復(fù)位和異步復(fù)位,一個(gè)同步的局部復(fù)位是一個(gè)標(biāo)準(zhǔn)設(shè)計(jì)里面的一部分,一般都是使用狀態(tài)機(jī)或者計(jì)數(shù)器讓一些信號(hào)

2017-02-08 06:38:10 98

98

DSP 資源的靈活性遠(yuǎn)遠(yuǎn)超過(guò)用戶認(rèn)知,加減乘除、累加、計(jì)數(shù)器、比較器,移位寄存器、復(fù)用器、模式匹配等等全部可以使用DSP實(shí)現(xiàn)。DSP如何使用復(fù)位呢?每一個(gè)DSP的Slice有超過(guò)250多個(gè)寄存器,但是沒(méi)有一個(gè)使用了異步復(fù)位。用戶使用同步復(fù)位可以令綜合工具更加容易的推斷出使用DSP資源。 這個(gè)事情的重要性,需要進(jìn)一步強(qiáng)調(diào)一下。同步復(fù)位可以令工具更容易的使用專用的硬件資源。特別對(duì)DSP資源來(lái)說(shuō),用戶特別喜歡DSP的輸出的寄存器,這樣可以增加

2017-02-08 06:42:08 95

95

3.最基本的DSP資源 3.1 由FIR濾波器談起 隨著各種應(yīng)用復(fù)雜度的不斷提升,傳統(tǒng)的DSP和處理器的架構(gòu)無(wú)法支持這么復(fù)雜的并行數(shù)據(jù)算法的需求。FPGA卻恰好能夠滿足這樣的需求。FPGA擁有大量

2017-02-08 06:44:04 132

132

使用, 而且從性能上講也比消耗邏輯資源的FIFO性能要好一點(diǎn)。XILINX 7系列中的FIFO是支持同步和異步讀寫(xiě)操作,不需要時(shí)鐘和數(shù)據(jù)之間有一個(gè)相位的便宜。空信號(hào),滿信號(hào),和可以編程的空滿信號(hào)都可以被用作控制FIFO的信號(hào),從而可以實(shí)現(xiàn)不同的功能。同步FIFO可以消除異步FIFO的固有的

2017-02-08 08:18:37 278

278

2.8 RAM資源的應(yīng)用 用戶做設(shè)計(jì)的時(shí)候發(fā)現(xiàn)自己的設(shè)計(jì)的代碼可能被識(shí)別為RAM資源,這個(gè)時(shí)候感覺(jué)很爽。有的時(shí)候啥也推斷不出來(lái),可能會(huì)影響設(shè)計(jì)的性能。 那么什么樣的資源才會(huì)被設(shè)計(jì)工具推斷出來(lái)呢? 單端口,真雙端口,簡(jiǎn)單雙端口塊RAM可以推斷. RTL代碼來(lái)描述希望RAM功能的,將會(huì)被工具推斷為RAM的資源。 RTL描述必須有如下特點(diǎn): 同步讀寫(xiě) 每個(gè)時(shí)鐘周期只有一個(gè)或兩個(gè)地址被訪問(wèn) 同步輸出復(fù)位 這就要求用戶必須對(duì)自己的代碼有一個(gè)非常清晰的認(rèn)識(shí)

2017-02-08 08:40:11 91

91

FPGA進(jìn)入到一個(gè)工藝越來(lái)越牛的境界,很多人在學(xué)習(xí)FPGA的時(shí)候還在墨守陳規(guī)的從Spartan3學(xué)起,還是在ISE開(kāi)始著手,總是覺(jué)得工藝是類似的,方法也是類似的。在和很多工程師一起討論的時(shí)候,就明確

2017-02-08 10:09:08 145

145 1. 最基本的CLB CLB是FPGA最最基本的單元,不能說(shuō)是類似于質(zhì)子和中子的概念,但也至少是原子和分子的概念了。如果是最根本的單元都無(wú)法能夠很好的理解,那么其實(shí)很多FPGA的原理還是停留在

2017-02-08 10:10:34 214

214

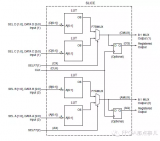

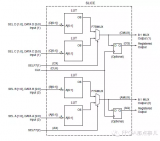

1.3再深入一點(diǎn)的了解CLB 這個(gè)圖有點(diǎn)大,但是太經(jīng)典了,搞得我不得不放棄扔掉它的想法。是不是有人已經(jīng)看迷糊了。那咱就慢慢的清晰唄。有時(shí)候也不一定要一開(kāi)始明白,如果一開(kāi)始明白,那么會(huì)越來(lái)越糊涂。 那么這個(gè)是啥?這個(gè)就是一個(gè)Slice,這個(gè)Slice由幾部分組成,4個(gè)六輸入查找表,很多的復(fù)用器(multiplexers),一條自下而上的進(jìn)位鏈(這個(gè)進(jìn)位鏈被連接到四個(gè)觸發(fā)器上的),8個(gè)FF的(4個(gè)的FF/Latches, 4個(gè)輔助的FF)。看看這個(gè)圖的好處就來(lái)了,我不

2017-02-08 10:14:29 104

104

1.3.3 聊一聊進(jìn)位鏈 進(jìn)位邏輯為了提高用戶的算術(shù)功能而專門(mén)設(shè)置的專用硬件資源,他可以改善加法器,累加器,減法器和比較器運(yùn)算速度。從圖中可以看到,左邊顯示的Slice被分組到同一個(gè)進(jìn)位鏈中。大家一定要注意,進(jìn)位鏈邏輯走向垂直向上。這是必須注意,因?yàn)榻^大多數(shù)設(shè)計(jì)都會(huì)廣泛的使用進(jìn)位鏈邏輯,那么用戶使用的時(shí)候,最起始的bit應(yīng)該被放置在進(jìn)位鏈的底部,這樣就可以節(jié)省很多的資源。當(dāng)然這個(gè)和大家設(shè)計(jì)的原理圖和Layout PCB的關(guān)系都很大

2017-02-08 10:18:34 209

209 的塊RAM實(shí)現(xiàn)的。所有7系列的FPGA都具有相同架構(gòu)的BlockRAM,每一塊BlockRAM是36KB大小的真正的雙端口存儲(chǔ)器,

2017-02-08 10:19:33 194

194 2.3 7 系列BlockRAM使用三種模式 2.3.1 簡(jiǎn)單單口BlockRAM 如上圖所示,簡(jiǎn)單的單口RAM的端口非常簡(jiǎn)單: 時(shí)鐘: CLKA, 地址: ADDRA 寫(xiě)使能: WEA, 寫(xiě)數(shù)據(jù)

2017-02-08 10:21:11 194

194 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個(gè)工藝級(jí)別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點(diǎn) 4.7系列

2020-11-13 18:03:30 14065

14065 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)-7系列是7系列產(chǎn)品中密度最低、成本最低的入門(mén)級(jí)產(chǎn)品

2020-12-10 14:20:00 18

18 本文檔的主要內(nèi)容詳細(xì)介紹的是Xilinx 7 系列FPGA中的Serdes總結(jié)。

2020-12-31 17:30:58 25

25 Xilinx-7系列FPGA主要包括:Spartan?-7、Artix?-7、Kintex?-7、Virtex?-7。其性能、密度、價(jià)格也隨著系列的不同而提升。和前幾代FPGA產(chǎn)品不同的是,7系列

2021-01-30 06:00:11 16

16 引言: 我們?cè)谶M(jìn)行FPGA原理圖和PCB設(shè)計(jì)時(shí),都會(huì)涉及到FPGA芯片管腳定義和封裝相關(guān)信息,本文就Xilinx 7系列FPGA給出相關(guān)參考,給FPGA硬件開(kāi)發(fā)人員提供使用。通過(guò)本文,可以了解到:

2021-05-01 09:47:00 10367

10367

XILINX是可編程邏輯芯片,由多個(gè)系列的性能可以滿足一般的邏輯設(shè)計(jì)要求,如賽靈思7系列,Xilinx?7系列FPGA由四個(gè)FPGA系列組成 7A 7V 7S 7K,可滿足各種系統(tǒng)要求,從低

2022-11-03 14:39:54 1446

1446 Xilinx是一家專業(yè)的可編程邏輯器件(PLD)廠商,其產(chǎn)品包括FPGA、CPLD、SOC等。Xilinx的FPGA產(chǎn)品線有多個(gè)系列,其中7系列和Ultrascale系列是比較常見(jiàn)的兩種。那么,這兩個(gè)系列有什么區(qū)別呢?

2023-09-15 14:44:54 1776

1776

Xilinx 7系列 芯片 應(yīng)用非常廣泛,具有成本低、性能強(qiáng)悍、成熟穩(wěn)定的特點(diǎn),目前Xilinx( AMD )已延長(zhǎng)該系列芯片的生命周期至少到2035年。 本文主要介紹Xilinx 7系列 FPGA

2023-11-28 10:20:02 392

392

Xilinx FPGA芯片擁有多個(gè)系列和型號(hào),以滿足不同應(yīng)用領(lǐng)域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點(diǎn)。

2024-03-14 16:24:41 215

215

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論