Xilinx Block Memory Generator(BMG)是一個(gè)先進(jìn)的內(nèi)存構(gòu)造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優(yōu)化的內(nèi)存。

2023-11-14 17:49:43 736

736

你好: 我是一個(gè)購(gòu)買(mǎi)的帳戶,所以我的許可證應(yīng)該允許訪問(wèn)所有內(nèi)容。但是當(dāng)我使用System Generator for DSP時(shí),系統(tǒng)說(shuō)我的SysGen簽出許可證失敗了。有人知道怎么解決嗎?謝謝

2019-01-28 07:16:36

錯(cuò)誤:System Generator for DSP(SysGen)的許可證簽出失敗。無(wú)法聯(lián)系Xilinx許可證管理器。請(qǐng)檢查以下內(nèi)容:(1)XILINX環(huán)境變量指向有效的ISE安裝(2

2018-12-29 10:35:12

FPGA中的數(shù)字控制器是什么?System Generator中的PID控制器是如何設(shè)計(jì)的?

2021-04-08 06:51:46

大家好,這是我第一次使用System Generator工具,如果有人能夠解決一個(gè)不讓我繼續(xù)參與我的硬件協(xié)同仿真項(xiàng)目的問(wèn)題,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根據(jù)我的理解,System Generator是MatLab到RTL的轉(zhuǎn)換,因此不包括Vivado的優(yōu)化過(guò)程。問(wèn)題1--是真的。確實(shí),Vivado中的優(yōu)化將大大改變系統(tǒng)描述,而系統(tǒng)描述不會(huì)向后兼容

2019-04-25 12:47:45

XILINX Core Generator的官方教學(xué)PPT

2012-08-15 18:44:59

design example.Just wondering Xilinx has any application notes and system generator design examples? Thanks,Will

2019-01-30 10:08:42

HI,我正在使用System Generator 2014.4 30天評(píng)估包,Matalb 2014B。簡(jiǎn)單地說(shuō)我想使用FIR編譯器,當(dāng)我嘗試編輯它的參數(shù)時(shí),我得到了兩個(gè)錯(cuò)誤: - 1.“來(lái)自MEX

2020-03-24 09:01:59

with FIR compiler 5.0 , in system generator. When i givea inputsinewave( amplitude of 1, 1 MHz

2019-02-12 11:20:48

嗨,我在系統(tǒng)生成器2014中使用黑盒子.4在模擬模式下選擇vivado模擬器。如果我運(yùn)行該項(xiàng)目它正常工作,但如果我在系統(tǒng)生成器或黑盒vhdl中更改某些內(nèi)容,則會(huì)出現(xiàn)此錯(cuò)誤:Xilinx模塊庫(kù)中發(fā)

2018-10-30 11:07:57

你好!我試圖通過(guò)系統(tǒng)生成器生成FFT的組件。我瀏覽了.mdl文件中的Stystem Generator塊,但是當(dāng)我嘗試生成時(shí),我收到以下錯(cuò)誤消息。我不明白為什么它無(wú)法連接到許可證管理器。我已經(jīng)通過(guò)

2018-11-27 14:22:40

, I have this basic doubt that why at all HDL coder is there in Matlab when we have system generator

2018-12-18 10:40:58

/fpga-design/simulink-with-xilinx-system-generator-for-dsp.htmlhttp://www.mathworks.cn/searchresults/?c%5B%5D

2013-10-05 11:59:34

USE和System Generator何時(shí)才能勝任64位Windows 7?以上來(lái)自于谷歌翻譯以下為原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

最近在搞system generator仿真,發(fā)現(xiàn)getway in這個(gè)模塊參數(shù)設(shè)置變化導(dǎo)致MATLAB閃退問(wèn)題,貼圖如下其中g(shù)etway in 這個(gè)模塊數(shù)據(jù)類型換成定點(diǎn)有符號(hào)或者無(wú)符號(hào)數(shù)都不得行,換成布爾值又會(huì)出現(xiàn)錯(cuò)誤,不知為何啊!求教。

2018-01-05 21:43:53

翻譯成verilog,在FPGA里面實(shí)現(xiàn),即system generator。altera有沒(méi)有類似的接口,與matlab可以互連,直接在matlab里設(shè)計(jì)我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

. But when it comes on selecting Matlab version for System generator 10.1 it displays both versions

2019-05-27 06:30:15

我的工程應(yīng)用中需用Xilinx10.1中的fifo核,具體步驟如下:1、在CORE generator下建立My232coregen.cgp文件,選擇以下功能: 圖1.2、進(jìn)入fifo

2012-05-15 19:02:08

我用system generator打開(kāi)matlab,simulink庫(kù)列表中跟多xilinx的庫(kù)什么模塊也沒(méi)有,還出來(lái)這個(gè)窗口,請(qǐng)問(wèn)怎樣把對(duì)應(yīng)的模塊顯示出來(lái),或從哪里找?謝謝

2018-01-19 10:37:50

組的FPGA實(shí)現(xiàn)7.7 本章小結(jié)第8章基于System Generator的DSP系統(tǒng)開(kāi)發(fā)技術(shù)8.1 System Generator的簡(jiǎn)介與安裝8.1.1 System Generator簡(jiǎn)介

2012-04-24 09:23:33

,使用System Generator有三大優(yōu)勢(shì):第一,圖形化操作,簡(jiǎn)單易用;第二,實(shí)現(xiàn)的算法能確保與仿真結(jié)果相符;第三,無(wú)需為仿真和實(shí)現(xiàn)建立不同的模型。因此,利用 System Generator可以大幅度減少用FPGA設(shè)計(jì)DSP的工作量,縮短開(kāi)發(fā)周期。

2019-06-21 06:25:23

各位好,最近在使用system generator 搭建一個(gè)ifft設(shè)計(jì)模塊,使用ise調(diào)用,但是在下載到板子后,示波器輸出波形去在沒(méi)有輸入的情況下仍然有波形,確定不是噪聲,波形還是很規(guī)律,求解釋呀!

2016-07-13 13:21:30

使用system generator導(dǎo)入xilinx模塊時(shí),只要連線兩個(gè)模塊,matlab就崩潰,有知道原因的大佬嗎?

2018-01-19 17:54:57

Xilinx system generator on Matlab with Vivado With ISE there is an application call System Generator

2018-12-27 10:57:02

Suite下。在我的PC上,Xilinx System Generator嵌套在Vivado下。可以使用基于Vivado的System Generator來(lái)開(kāi)發(fā)ISE系統(tǒng)嗎?或者是否有必須安裝

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在內(nèi)部,有一個(gè)基于VHDL的框架,它將定制板上的不同部分與“DSP內(nèi)核”連接,后者是在System Generator下開(kāi)發(fā)的。在這

2019-01-15 10:39:11

在system generator中,我把(-128~127),變?yōu)椋?1~1),但是下載到硬件中,使用chipscope抓取到的數(shù)據(jù)確實(shí)(-128~127),請(qǐng)問(wèn)是怎么回事

2016-08-10 15:32:38

有做System Generator處理圖像的嗎?遇到一些問(wèn)題,一起商量下

2020-09-28 19:04:58

嗨,我正在嘗試學(xué)習(xí)如何使用System Generator來(lái)創(chuàng)建自己的IP核。首先,我在DocNav中找到了一個(gè)ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“examples”文件夾中找不到完全相同的示例。提前致謝馬丁

2020-05-22 07:22:09

this system generator?Is this a part of xilinx ISE design tool.If so please give me idea how can I use it to generate the sinc signals?thank you

2019-01-28 06:37:12

您好,我被要求執(zhí)行序列生成器。我已經(jīng)用紙做過(guò)一切,但我不知道如何在Xilinx上正確創(chuàng)建它。我完成了轉(zhuǎn)換表和輸出表。我的輸出函數(shù)已經(jīng)用karnaugh等進(jìn)行了簡(jiǎn)化。但是當(dāng)我實(shí)現(xiàn)它時(shí),我認(rèn)為它在

2019-01-10 10:39:50

各位大佬,我在安裝System Generator時(shí),跟著教程走,發(fā)現(xiàn)在vivado中沒(méi)有出現(xiàn)System Generator for DSP這個(gè)選項(xiàng),請(qǐng)問(wèn)是我哪里安裝得不對(duì)嗎?

2023-09-26 21:54:58

當(dāng)我完成SDx 2017.2的安裝時(shí),沒(méi)有安裝System Generator的選項(xiàng)。我正在運(yùn)行從Xilinx下載的安裝程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator創(chuàng)建一個(gè)雙向(inout)端口。我正在嘗試為Xilinx的外部存儲(chǔ)器創(chuàng)建一個(gè)接口

2019-05-09 14:36:24

...以上來(lái)自于谷歌翻譯以下為原文Hi all!!! I am implementing ofdm using xilinx system generator.In the transmitter

2019-04-19 10:32:12

最近在使用system generator設(shè)計(jì)一個(gè)rs編碼譯碼的模型,總的思想是在rs編碼產(chǎn)生信號(hào)后,插入一個(gè)誤碼,然后作為信號(hào)源進(jìn)行解碼,看是否能夠正常的進(jìn)行解碼,求解是怎么才能把rs編碼后的信號(hào)存儲(chǔ)起來(lái)作為信號(hào)源

2016-07-20 20:13:59

嗨,我剛剛安裝了ISE 14.7系統(tǒng)版本,并將System Generator鏈接到MATLAB(2014a)。但是當(dāng)我嘗試打開(kāi)simulink以使用Xilinx System Generator

2018-12-12 10:54:08

2014.3.1) itself ? Couldn't find the RESOURCE ESTIMATOR block inthe system generator [xilinx

2019-04-02 14:32:18

有用Xilinx的system generator做圖像處理的嘛?求交流 。我正在用這個(gè)做圖像處理,已經(jīng)用了3個(gè)月了,在做一些算法,遇到一些困難,求一起交流學(xué)習(xí)。發(fā)現(xiàn)用這個(gè)開(kāi)發(fā)的人真不多啊。

2014-05-09 14:57:21

非常苦惱,剛開(kāi)始學(xué)習(xí)system generator,用帶光盤(pán)的書(shū)上的例子,想要學(xué)習(xí)一下設(shè)計(jì)流程,結(jié)果屢屢碰壁。在搭建好系統(tǒng),點(diǎn)擊開(kāi)始仿真之后,總是會(huì)出錯(cuò)。在別人的電腦上就能仿真成功,一開(kāi)始認(rèn)為是

2016-07-13 23:12:36

xilinx公司的網(wǎng)絡(luò)教程“利用 System Generator 進(jìn)行 DSP 設(shè)計(jì)”誰(shuí)有?上傳一份給小弟吧

2013-03-14 12:17:03

解決方案以上來(lái)自于谷歌翻譯以下為原文hi,i have used xilinx 14.1 and matlab2012awhen i opened a system generator it shows

2019-03-11 14:17:09

System Generator。我已使用下載站點(diǎn)上提供的WebPACK_82i_SFD.exe重新安裝了ISE 8.2i。但是,系統(tǒng)生成器仍然不可用。我需要做什么才能將系統(tǒng)生成器“重新安裝”到Matlab中

2018-11-19 14:42:56

簡(jiǎn)化Xilinx和Altera FPGA調(diào)試過(guò)程:通過(guò)FPGAViewTM 解決方案,如混合信號(hào)示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動(dòng)探點(diǎn),而無(wú)需重新編譯設(shè)計(jì)方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 26

26

采用Gardner算法,對(duì)QPSK調(diào)制解調(diào)系統(tǒng)中的位同步系統(tǒng)進(jìn)行設(shè)計(jì)與實(shí)現(xiàn),大大提高了系統(tǒng)性能和資源利用率。重點(diǎn)闡述采用FPGA開(kāi)發(fā)環(huán)境System Generator系統(tǒng)設(shè)計(jì)工具進(jìn)行位同

2010-07-21 16:12:40 26

26 深入了解賽靈思System Generator中的時(shí)間參數(shù)

基于模型的設(shè)計(jì)(MBD)因其在縮小實(shí)時(shí)系統(tǒng)抽象的數(shù)學(xué)建模和物理實(shí)現(xiàn)之間差距方面的光明前景而備受關(guān)注。通過(guò)使用相同的

2009-12-29 11:40:30 1300

1300

HDL設(shè)計(jì)和驗(yàn)證與System Generator相結(jié)合

Xilinx®SystemGeneratoRForDSP是用來(lái)協(xié)助系統(tǒng)設(shè)計(jì)的MATLABSimulink模塊集。SystemGeneratorforDSP在熟悉的MATLAB環(huán)境中引入XilinxFPGA對(duì)象,讓您能夠

2010-01-06 14:39:30 1181

1181

基于軟件無(wú)線電的思想,闡述了第四代移動(dòng)通信核心技術(shù)OFDM的原理及其IFFT/FFT實(shí)現(xiàn)的數(shù)學(xué)模型,并且提出了OFDM調(diào)制的核心部分IFFT的軟件實(shí)現(xiàn)方法,即采用XILINX公司的System Generator這一高

2011-05-05 17:02:59 91

91 該設(shè)計(jì)是基于System Generator設(shè)計(jì)平臺(tái),在Matlab/Simulink環(huán)境下搭建系統(tǒng)模型,再進(jìn)行功能仿真和驗(yàn)證,完成QPSK調(diào)制器的設(shè)計(jì)。仿真結(jié)果表明,所設(shè)計(jì)的調(diào)制器能產(chǎn)生正確QPSK波形,達(dá)到了預(yù)期效果

2011-10-17 16:10:51 65

65 Xilinx公司推出的DSP設(shè)計(jì)開(kāi)發(fā)工具System Generator是在Matlab環(huán)境中進(jìn)行建模,是DSP高層系統(tǒng)設(shè)計(jì)與Xilinx FPGA之間實(shí)現(xiàn)的橋梁。在分析了FPGA傳統(tǒng)級(jí)設(shè)計(jì)方法的基礎(chǔ)上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 Xilinx FPGA工程例子源碼:System Generator的設(shè)計(jì)實(shí)例

2016-06-07 14:41:57 22

22 、乘加(MACC, ),乘加,三輸入加法等等。該架構(gòu)還支持串聯(lián)多個(gè)DSP48E1 slice,避免使用fpga邏輯功能的繁瑣。 System generator DSP48E1 模塊參數(shù) 雙擊dsp48e1模塊

2017-02-08 01:07:12 595

595

環(huán)境 ?Matlab 2014 a ?Vivado 2014.4 ?System generator 2014.4 實(shí)現(xiàn)步驟 1、模型搭建與仿真 在simulink環(huán)境下工程搭建如下 圖3 四路加

2017-02-08 01:10:08 473

473

賽靈思(Xilinx)近期宣布推出高階設(shè)計(jì)工具2015.3版DSP系統(tǒng)產(chǎn)生器(System Generator),可讓系統(tǒng)工程師運(yùn)用Xilinx All Programmable組件設(shè)計(jì)高效能DSP系統(tǒng)。

2019-10-06 18:00:00 283

283 最新版 ?DSP? 系統(tǒng)生成器 ? ( System Generator for DSP ),是設(shè)計(jì)高性能 ?DSP? 系統(tǒng)的業(yè)界領(lǐng)先高級(jí)工具,不僅可實(shí)現(xiàn)較高層次的設(shè)計(jì)抽象性,而且還可可通過(guò)整合

2017-02-08 20:41:18 254

254 一直都在System Generator下做圖像處理相關(guān)的算法,感覺(jué)SysGen挺強(qiáng)大的,前幾天突發(fā)奇想,能否直接用SysGen實(shí)現(xiàn)數(shù)據(jù)的通信呢,畢竟一句HDL代碼都不寫(xiě)對(duì)于做FPGA的人來(lái)說(shuō)卻是很有吸引力的。

2017-02-10 19:51:11 2618

2618

前一陣一直在忙,所以沒(méi)有來(lái)得及寫(xiě)博文。弄完雜七雜八的事情,又繼續(xù)FPGA的研究。使用Verilog HDL語(yǔ)言和原理圖輸入來(lái)完成FPGA設(shè)計(jì)的方法都試驗(yàn)過(guò)了,更高級(jí)的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

System Generator是Xilinx公司進(jìn)行數(shù)字信號(hào)處理開(kāi)發(fā)的一種設(shè)計(jì)工具,它通過(guò)將Xilinx開(kāi)發(fā)的一些模塊嵌入到Simulink的庫(kù)中,可以在Simulink中進(jìn)行定點(diǎn)仿真,可是設(shè)置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系統(tǒng)級(jí)建模工具,它是擴(kuò)展mathworks公司的MATLAB下面的simulink平臺(tái),添加了XILINX FPGA專用的一些模塊。加速簡(jiǎn)化了FPGA的DSP系統(tǒng)級(jí)硬件設(shè)計(jì)。

2017-02-11 19:21:33 7386

7386

利用System Generator軟件平臺(tái),實(shí)現(xiàn)基于模塊化建模方法的變換器建模,并簡(jiǎn)化語(yǔ)言編寫(xiě)控制系統(tǒng)的復(fù)雜過(guò)程。研究了從MATLAB-Xilinx環(huán)境中導(dǎo)出使用模塊化建模方法搭建的控制算法。通過(guò)

2017-11-15 14:31:34 4985

4985

的對(duì)應(yīng)關(guān)系: System generator 安裝之后會(huì)在Simulin模塊庫(kù)中添加一些Xilinx FPGA專用的模塊庫(kù),包括Basic Element,Communication,Control

2017-11-17 14:29:06 7298

7298 在FPGA平臺(tái)上應(yīng)用System Generator工具實(shí)現(xiàn)了高精度頻率估計(jì)Rife算法。不同于傳統(tǒng)的基于HDL代碼和IP核的設(shè)計(jì)方法,采用System Generator工具可以使復(fù)雜算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是專門(mén)為數(shù)字信號(hào)算法處理而推出的模型化設(shè)計(jì)平臺(tái),可以快速、簡(jiǎn)單地將DSP系統(tǒng)的抽象算法轉(zhuǎn)換成可綜合的、可靠的硬件系統(tǒng),彌補(bǔ)了大部分對(duì)C語(yǔ)言以及Matlab工具很熟悉的DSP工程師對(duì)于硬件描述語(yǔ)言VHDL和Verilog HDL認(rèn)識(shí)不足的缺陷。

2018-07-19 09:32:00 3716

3716

PLD/FPGA 常用開(kāi)發(fā)軟件System Generator 9.10。 業(yè)內(nèi)領(lǐng)先的高級(jí)系統(tǒng)級(jí)FPGA開(kāi)發(fā)高度并行系統(tǒng)。

2017-11-26 11:34:56 12

12 本視頻產(chǎn)品演示介紹了 Xilinx 系統(tǒng)生成器(System Generator)和 Xilinx ISE? 項(xiàng)目瀏覽器(Project Navigator)設(shè)計(jì)環(huán)境之間的新整合。

2018-06-06 13:46:00 3024

3024

新的System Generator,算法開(kāi)發(fā)人員可在其熟悉的MATLAB和Simulink模型化設(shè)計(jì)環(huán)境中創(chuàng)建生產(chǎn)質(zhì)量級(jí)的DSP實(shí)現(xiàn)方案,而且相校傳統(tǒng) RTL 可大幅縮短設(shè)計(jì)時(shí)間。最新版提供了更高級(jí)的設(shè)計(jì)抽象,并可通過(guò)新型的模塊集中、更快的仿真和編譯運(yùn)行時(shí)間,將無(wú)線電算法的設(shè)計(jì)生產(chǎn)力提高7倍。

2018-08-20 10:13:00 763

763 了解如何將Vivado HLS設(shè)計(jì)作為IP模塊整合到System Generator for DSP中。

了解如何將Vivado HLS設(shè)計(jì)保存為IP模塊,并了解如何將此IP輕松整合到System Generator for DSP的設(shè)計(jì)中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多個(gè)時(shí)鐘域,從而可以實(shí)現(xiàn)復(fù)雜的DSP系統(tǒng)。

2018-11-27 06:42:00 3450

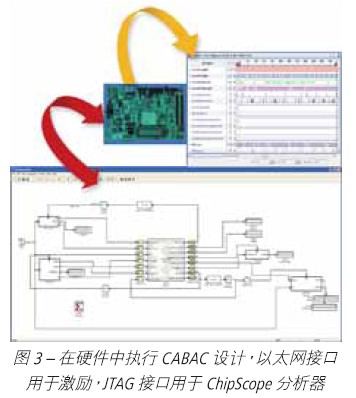

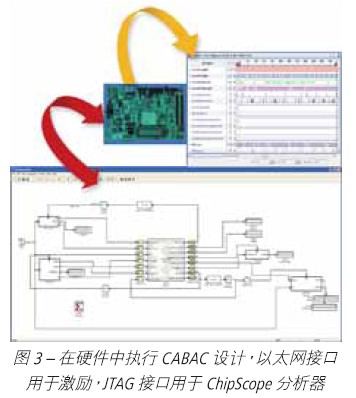

3450 了解如何使用Vivado System Generator for DSP進(jìn)行點(diǎn)對(duì)點(diǎn)以太網(wǎng)硬件協(xié)同仿真。

System Generator提供硬件協(xié)同仿真,可以將FPGA中運(yùn)行的設(shè)計(jì)直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 System Generator 數(shù)字上下變頻 (DUC/DDC)模塊集的易用性大幅提升,使得更加便于無(wú)線算法開(kāi)發(fā)。這些新型模塊還添加了有助于加速驗(yàn)證和編譯運(yùn)行時(shí)間的增強(qiáng)功能,所有這些模塊提供了七八種參數(shù)設(shè)置。

2019-07-31 09:22:49 2293

2293 根據(jù)橢圓曲線密碼體制的幾種關(guān)鍵算法,采用Modelsim仿真工具設(shè)計(jì)相應(yīng)的算法模塊。然后將各模塊代碼通過(guò)System Gene

2021-06-12 10:17:00 1294

1294

本篇博文是面向希望學(xué)習(xí) Xilinx System Generator for DSP 入門(mén)知識(shí)的新手的系列博文第一講。其中提供了有關(guān)執(zhí)行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

上文XILINX FPGA IP之FIFO對(duì)XILINX FIFO Generator IP的特性和內(nèi)部處理流程進(jìn)行了簡(jiǎn)要的說(shuō)明,本文通過(guò)實(shí)際例子對(duì)該IP的使用進(jìn)行進(jìn)一步的說(shuō)明。本例子例化一個(gè)讀數(shù)據(jù)位寬是寫(xiě)數(shù)據(jù)位寬兩倍的FIFO,然后使用讀時(shí)鐘頻率:寫(xiě)時(shí)鐘頻率=2:3,進(jìn)行簡(jiǎn)單的FIFO跨時(shí)鐘域操作。

2023-09-07 18:31:35 759

759

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論