Altera推出業界唯一投產的低功耗28 nm Cyclone? V GT FPGA,幫助開發人員降低了PCIe Gen2應用的系統總成本,并全面通過了PCI Express? (PCIe?) 2.0規范的兼容性測試。

2013-03-19 12:37:39 2139

2139 6678的pcie和fpga的pcie? TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

?

2018-06-21 15:49:12

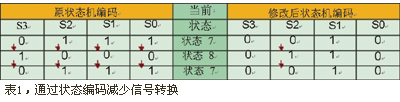

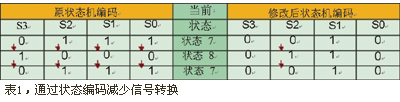

系列子系列介紹表 (1) Artix-7 FPGA系列——業界最低功耗和最低成本 通過表1我們不難得出以下結論: 與上一代 FPGA相比,其功耗降低了50%,成本削減了35%,性能提高30%,占用

2012-09-21 13:46:16

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能夠做到如此低的功耗是因為什么?

2021-04-30 06:08:49

FPGA已經被廣泛用于實現大規模的數字電路和系統,隨著CMOS工藝發展到深亞微米,芯片的靜態功耗已成為關鍵挑戰之一。文章首先對FPGA的結構和靜態功耗在FPGA中的分布進行了介紹。接下來提出了晶體管

2020-04-28 08:00:00

是90nm的1.2 V器件,與先前產品相比可降低靜態和動態功耗,且FPGA制造商采用不同的設計技術進一步降低了功耗,平衡了成本和性能。這些90nm器件都改變了門和擴散長度,優化了所需晶體管的開關速率

2015-02-09 14:58:01

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-11-05 07:54:43

對于各種不同的數據中心工作負載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-08-13 08:03:44

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-08-29 07:52:29

電源引腳布局減小了22%,功耗降低了35%。圖1 2.有效應對噪聲敏感輸入 因為FPGA中許多模塊對供電電源噪聲非常敏感,而噪聲會導致產生抖動,隨之帶來很高的誤碼率(BER),降低了電路性能,而

2018-10-23 16:33:09

目前許多終端市場對可編程邏輯器件設計的低功耗要求越來越苛刻。工程師們在設計如路由器、交換機、基站及存儲服務器等通信產品時,需要密度更大、性能更好的FPGA,但滿足功耗要求已成為非常緊迫的任務。而在

2019-07-15 08:16:56

。除此之外,設計中采用一些低功耗技巧,也可以降低靜態功耗。IGLOO具有功耗友好的器件架構,能提供靜態、睡眠、Flash*Freeze功耗模式,允許采用動態電壓和頻率調節技術來降低系統整體實際功耗。提供可選擇

2019-07-05 07:19:19

PCIe設備的低功耗狀態要求系統驅動程序顯式地將設備置于低功耗狀態,從而PCIe鏈路則可以依次變為低功耗鏈路狀態。PCIe規范允許PCIe鏈路在沒有系統驅動的情況下進入低功耗狀態。這個特性就是所謂

2021-12-28 06:18:35

PCIe設備的低功耗狀態要求系統驅動程序顯式地將設備置于低功耗狀態,從而PCIe鏈路則可以依次變為低功耗鏈路狀態。PCIe規范允許PCIe鏈路在沒有系統驅動的情況下進入低功耗狀態。這個特性就是所謂

2022-01-03 08:00:09

設計技巧為什么能夠節省功耗?降低FPGA功耗的設計技巧有哪些?

2021-04-30 06:04:19

降低FPGA功耗的設計技術 Design Techniques to Reduce Power Consumption Each generation of FPGAs gets

2009-12-18 16:49:59

”,這個系統大到宇宙空間,小到微觀空間個體。在電子領域更可以直接指不同的工作系統,不同的單個器件。簡化模型如圖1。橋接的目的是什么?是為了兩個系統之間產生物理或者電氣連接,為了傳輸特定的媒介。在電子領域

2022-02-20 07:00:00

LT4320IN8-1理想二極管橋控制器的典型應用電路。 LT4320-1是理想的二極管橋控制器,可驅動四個N溝道MOSFET,支持典型的DC至600Hz的電壓整流。通過最大化可用電壓并降低功耗,理想的二極管橋簡化了電源設計并降低了電源成本,特別是在低壓應用中

2019-03-29 07:58:55

通過最大化可用的電壓和降低功耗(請參閱下面的溫度計比較),理想二極管橋簡化了電源設計和降低供電成本,尤其是在低電壓應用。一個理想二極管橋也消除了熱設計問題,昂貴的散熱片,并大大降低了印刷電路板面積。

2019-10-23 09:10:25

Virtex 7 PCIe硬IP是否意味著FPGA內部的ASIC?或者像Tandem方法一樣,在第一階段,CPLD將PCIe初始配置加載到FPGA? (http://www.em.avnet.com

2020-05-29 12:52:09

層板設計,專業的PCB Layout保證信號完整性的同時,經過嚴格的質量控制,滿足工業環境應用。SOM-TLK7核心板引出FPGA豐富的資源信號引腳,二次開發極其容易,客戶只需要專注上層應用,大大降低了

2020-09-24 14:39:36

項目名稱:FPGA PCIe信號拆分應用領域:計算機參賽計劃:利用FPGA的并行資源,實現在不使用plx硬核芯片的情況下對PCIe信號的拆分。具體有效帶寬視開發板資源而定。使用FPGA相較于使用硬核

2021-05-12 18:05:46

1688Mb/s的DDR3存儲器。可以被配置為三態用于降低功耗和高速IO操作。除了供電引腳和一些專用的配置引腳,每個BANK里的IO有相同的IO能力。7系列的FPGA,其IO可以分為寬電壓IO標準和高性能兩種

2016-11-01 15:52:18

。上次介紹了該開發板所采用的PCIE傳輸框架RIFF,今天進一步分析其ARM端的測試例程pcie2screen并介紹一下FPGA端程序的修改。一、測試例程pcie2screen例程pcie

2023-02-13 17:57:47

了DMA 讀寫功能的模塊,而且 RIFFA 模塊提供了TX 和 RX 讀寫接口,因此用可以直接操作 RIFFA 的讀寫接口,從而來控制 PCIE 模塊的讀寫,有了 RIFFA 模塊大大降低了 FPGA

2023-01-30 14:14:25

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰。為什么要設計優化FPGA功耗?

2019-08-08 07:39:45

客戶關注的問題。降低FPGA功耗是降低封裝和散熱成本、提高器件可靠性以及打開移動電子設備等新興市場之門的關鍵。

2019-09-20 06:33:32

基于V7的高性能PCIe信號處理板是什么?基于V7的高性能PCIe信號處理板有哪些主要功能?基于V7的高性能PCIe信號處理板有哪些應用?

2021-06-25 06:21:15

進行原型開發,把設計移植到低風險、低成本HardCopy V ASIC,性能將大大提高,功耗能夠降低50%。Stratix V FPGA具有以下優點: (1)高功效收發器突破了帶寬 a.集成

2012-09-21 13:49:05

案例中,這樣的平臺需要進行一定的調整以滿足汽車制造商的需求。而使用FPGA可以快速實現低成本橋接解決方案,使得現有平臺能夠完美應用于汽車領域。

2019-07-23 07:57:39

總諧波失真 (THD) 低于一定百分比,而且還需要每個諧波都不超過 IEC 61000-3-2 合規性標準中規定的特定限值。在這篇共分兩部分的博客中,我將介紹用于降低 PFC 諧波和改善 THD

2018-09-12 09:47:28

最新器件 Virtex-4 FPGA 提供了 90 nm 工藝技術的高性能,卻避免了預想中靜態功耗的顯著增大。使用賽靈思功耗估算工具并遵循低功耗設計考慮事項,滿足您的功耗目標將比以往任何時候都更加容易。

2012-01-11 11:59:44

有著嚴格的浪涌電流和穩態工作電流限值要求,因此由總線供電的器件應用經常忽視FPGA,而是更愿意采用性能和靈活性都不及 FPGA 的微控制器解決方案。隨著賽靈思低功耗系列器件中最新成員Artix-7

2016-07-27 17:14:50

事件被捕獲使用硬件UART克服軟件實現的性能限制LCMXO2-640HC-4TG100C可編程邏輯器件FPGA芯片通過硬件性能加速提升系統性能基于邏輯的信號過濾降低了處理器負荷以最小的處理器開銷實現

2019-09-20 15:13:30

處理器的設計正在從提高頻率向降低功耗的方向轉變,為滿足更高性能的要求并使功耗不超過許多應用所能承受的范圍,微處理器的一個明顯變化是從頻率越來越高向多內核架構轉變。

2019-11-08 06:21:20

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-08-15 08:28:42

如何降低可重構系統的整體功耗?有什么方法能使可重構系統的性能和功耗需求之間達到平衡?

2021-04-08 07:09:23

現在需要一反向耐壓值為600V,電流為3A的整流橋作為開關電源的整流器,但是,這個高壓整流橋的壓降大,這樣引起的功耗就大,由于對開關電源的效率有要求,請問有什么辦法可以降低整流橋的功耗嗎?或者,有低壓降的高壓整流橋推薦嗎?

2014-05-13 19:53:40

/latest_fpgas_show_big_gains_in_floating_point_performance/我對SP Add的Virtex 7 - 690T的計算如下:1-將頻率降低15% - 對于

2020-08-13 09:56:00

嗨,我能夠在我們的定制板上連接到virtex 7 fpga。我的塊級設計具有用于pcie的軸橋作為終點和axi bram。但我無法使用pcie鏈接從外部處理器訪問bram。任何人都可以幫忙解決這個問題嗎?大多數情況下,我猜這與地址翻譯有關,我無法弄清楚。謝謝

2020-04-22 09:31:47

嗨,我正在使用AXI-PCIe橋接IP與我的邏輯進行通信。我的poroject要求有128K內存。我不知道如何配置AXI BAR地址來擴展內存。我閱讀了IP文檔,但沒有任何意義。目前我能夠從具有32K PCIe BAR空間的PC讀寫。

2020-06-19 10:14:32

針對互連功能以及高性能和低功耗進行了優化。ECP5 FPGA系列提供業界最小尺寸封裝(10x10 mm),并具備高達85K查找表(LUT),功能密度相比競品高出近2倍,同時成本和功耗也大幅降低

2020-10-21 11:53:02

從工藝選擇到設計直至投產,設計人員關注的重點是以盡可能低的功耗獲得最佳性能。Altera在功耗和性能上的不斷創新,那其28nm高端FPGA如何實現功耗和性能的平衡?具體有何優勢?

2019-09-17 08:18:19

如何利用FPGA實現低成本汽車多總線橋接?

2021-04-29 06:51:23

復雜器件專業技術相結合,將為系統供應商提供低功耗的芯片方案,供他們在此基礎上持續提高帶寬容量,并完成更智能的處理。此外,TPACK提供的芯片解決方案可以導入到最新的FPGA中,進一步降低功耗。最終實現

2019-07-31 07:13:26

對于各種不同的數據中心工作負載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-10-10 07:46:05

如何才能實現降低FPGA設計的功耗?

2021-04-29 06:47:38

相關的影響和設計問題,并介紹一些可行的解決方案和應用方法。橋接新舊視頻接口人們對創新的低成本視頻橋接解決方案的需求正與日俱增。 例如,構建監控系統、無人機或 DSLR 攝像頭的設計人員想要利用上熱門移動

2017-04-06 13:48:17

我的項目是為安全關鍵應用開發基于VMEbus的LCD模塊。我只會使用VMEbus的連接器P1到背板。要使用的模塊是:人機界面(LCD模塊)數據輸入(例如,通過鍵)數據輸出(LED)地址選擇邏輯 16

2019-05-23 08:52:42

嗨,我正在使用超大規模的FPGA板。我可以通過DMA子系統IP和DDR控制器IP將數據從PC傳輸到DDR。我打算在FPGA中進行一些處理,然后更新數據,以便PC可以讀取。如何通過PCIe指示PC處理

2020-05-08 09:40:04

,允許采用動態電壓和頻率調節技術來降低系統整體實際功耗。提供可選擇的1.2V和1.5V的I/O和核電壓,以方便用戶平衡設計的性能和功耗之間的關系。IGLOO的時鐘結構可以沒有副作用的對全局信號和局部信號進行門控制。另外IGLOO的RAM模塊具有LP和F*F端口來控制RAM本身的靜態功耗。

2020-05-13 08:00:00

我有一個問題,我必須在使用JTAG將位文件下載到FPGA后重新啟動計算機。否則,我無法使用PCIE讀取寄存器或與PCIE接口有關的任何內容。我該怎么做才能改善我的情況?謝謝。

2020-06-02 15:56:26

。電池通過PIC用來sh的PMOSfet直接連接到GSM模塊。關閉GSM模塊并降低功耗。我與LDO有一些問題,只提供PIC和一些上拉,當GSM模塊注冊或發送GPRS分組時,我每4mS獲得大約500S

2019-09-19 14:05:22

究竟怎樣才算低功耗?小于5mA?小于1ms?小于100uA?怎樣通過軟件控制的方式來優化并降低單片機的功耗?低功耗的范圍大概在哪?

2021-07-08 06:25:55

脈寬調制器 (DPWM)、低功耗微控制器等。它們是如無橋接 PFC 等復雜高性能電源設計的較好選擇。數字控制無橋接 PFC在其他一些無橋接 PFC 拓撲結構中[1] [2],圖 1 是一個已經為業界所廣泛

2018-09-26 10:52:03

的功耗取決于FPGA芯片及硬件設計本身,很難有較大的改善。可以優化是第3部分功耗:設計動態功耗,而且這部分功耗占總功耗的90%左右,因此所以降低設計動態功耗是降低整個系統功耗的關鍵因素。上面也提到過功耗

2014-08-21 15:31:23

的視頻放大器只需要2V/V增益(圖9),從而降低了對最后一級視頻放大器的要求,并降低功耗。同時也降低了兩個放大器的總功耗,實現最佳性能。

2020-12-17 09:52:10

嗨,我將從一個新項目開始。它涉及使用FPGA和GP / GPU加速PCIe板,這些板將被添加到常規計算機或服務器中。 GPU將是NVIDIA特斯拉。 FPGA板......還有待選擇。我確實看到了

2019-01-24 10:55:48

如何利用FPGA設計技術降低功耗?

2021-04-13 06:16:21

本帖最后由 一只耳朵怪 于 2018-6-25 11:01 編輯

你好!我目前正在實現6657DSP 評估板與xilinx kintex7 FPGA之間的PCIE連接,其中DSP作為Root

2018-06-25 05:14:40

成本 通過表1我們不難得出以下結論: 與上一代 FPGA相比,其功耗降低了50%,成本削減了35%,性能提高30%,占用面積縮減了50%,賽靈思FPGA芯片在升級中,功耗和性能平衡得非常好。 (2

2012-09-06 16:24:35

PCI Express是一種高性能互連協議,被廣泛應用于網絡適配、圖形加速器、網絡存儲、大數據傳輸以及嵌入式系統等領域。文中介紹了PCIe的體系結構,以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

ARM處理器),釋放寶貴的可編程邏輯資源,用于實現其他邏輯功能,從而提高了性能,降低了功耗和成本。作為一個例子,PCI Express(PCIe)協議堆棧需要大約150K LE作為軟核實現,在硬核模塊中則

2015-02-09 15:02:06

描述 Kintex?-7 FPGA 為您的設計在 28nm 節點實現最佳成本/性能/功耗平衡,同時提供高 DSP 率、高性價比封裝,并支持 PCIe? Gen3 和 10 Gigabit

2023-11-10 14:22:14

新一代 FPGA的速度變得越來越快,密度變得越來越高,邏輯資源也越來越多。那么如何才能確保功耗不隨這些一起增加呢?很多設計抉擇可以影響系統的功耗,這些抉擇包括從顯見的

2009-06-20 10:37:12 2321

2321

本白皮書介紹了有關賽靈思 28 nm 7 系列 FPGA 功耗的幾個方面,其中包括臺積電 28nm高介電層金屬閘 (HKMG) 高性能低功耗(28nm HPL 或 28 HPL)工藝的選擇。 本白皮書還介紹了 28 HPL 工藝提供

2012-03-07 14:43:44 41

41 白皮書 :采用低成本FPGA實現高效的低功耗PCIe接口 了解一個基于DDR3存儲器控制器的真實PCI Express (PCIe) Gen1x4參考設計演示高效的Cyclone V FPGA怎樣降低系統總成本,同時實現性能和功耗

2013-02-26 10:04:25 72

72 商湯科技算法平臺團隊和北京大學高能效實驗室聯合提出一種基于 FPGA 的快速Winograd算法,可以大幅降低算法復雜度,改善 FPGA 上的 CNN 性能。

2018-02-07 11:52:06 8687

8687

賽靈思7系列FPGA產品通過采用新的工藝和新的架構方式,成功將產品的功耗顯著降低。7系列FPGA產品的實測功耗與上一代產品相比,降低了約一半。采用臺積電全新28HPL工藝,賽靈思7系列28nm FPGA產品同時實現了高性能和低功耗。

2018-06-05 13:45:00 4086

4086 查看UltraScale FPGA中集成的PCIe Gen3模塊的性能演示。

第一個演示顯示了PCIe鏈路上的最大數據吞吐量;

demo#2利用現成的DMA引擎和軟件驅動程序來代表典型的用例。

2018-11-28 06:22:00 3464

3464 與傳統FPGA架構相比,UltraScale架構引入了許多創新,可提高性能并降低功耗。

在本視頻中,我們將重點介紹路由,邏輯和實現軟件的增強功能......

2018-11-22 06:45:00 3056

3056 reconfigure.io的Rob Taylor在法蘭克福的XDF 2018云軌道中展示了一個用例。

Rob討論了FPGA在FPGA中的可訪問性,降低了評估和利用FPGA的成本。

2018-11-22 06:08:00 3402

3402 高線性度下變頻混頻器使 3G 和 4G 無線基站的性能提高并降低了功耗

2021-03-21 10:18:10 3

3 本文介紹一個FPGA 開源項目:PCIE I/O控制卡。上一篇文章《FPGA優質開源項目– PCIE通信》開源了基于FPGA的PCIE通信Vivado工程,用于實現上位機通過PCIE接口訪問FPGA的DDR3以及RAM內存數據。PCIE I/O控制卡工程是在上一個工程的基礎上進行了部分模塊和參數的修改。

2023-09-01 16:18:36 1296

1296

V不僅對之前Arora家族進行了補充,還在降低功耗的同時顯著提升了性能。與Arora家族GW2A系列相比,Arora V器件的性能提高了30%,功耗降低了60%。Arora V編程配置為設計人員提供

2023-11-02 09:45:04 638

638 性能提升,功耗降低!,這樣的MOSFET是你的最愛么?

2023-12-04 15:09:36 114

114

電子發燒友App

電子發燒友App

評論