Xilinx ISE Design Suite 12.3 – 現已面市!

2010-10-09 15:22:09 1235

1235 電子發燒友網核心提示 :Xilinx ISE 14.2安裝指南,包括Xilinx ISE 14.2軟件下載、Xilinx ISE 14.2軟件安裝、Xilinx ISE 14.2相關產品介紹、Xilinx ISE軟件激活、Xilinx ISE14.2軟件啟動和Xilinx ISE 14.2新建工

2012-10-31 11:59:13 61264

61264

7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 。Xilinx FPGA7系列分為全局時鐘(Global clock)和局部時鐘(Regional clock)資源。目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

16500C邏輯分析系統的狀態和時序分析器

2019-02-28 13:26:11

軟件化廣播接收機使用XILINX的xc7k325t,PLL出400MHZ時鐘作為時分5個頻道的clk;每個頻道80MHZ采樣;編譯后slack為-2.702;DATAPATH DELAY (FF

2018-10-11 22:49:10

我是Xilinx和FPGA的新手。 我有一個Spartan3A入門套件。我的困惑在于ISE Project Navigator和Xilinx Platform Studio。有什么不同? 我知道

2019-01-14 12:39:27

“TS_ADC2_CLK_N”= PERIOD“ADC2_CLK_N”“TS_ADC1_CLK_N”PHASE +2 ns;在某一點上,一個時鐘源的一些數據到達一個由另一個的+時鐘計時的寄存器。時序分析器在這里報告

2019-07-29 12:51:47

有沒有哪位大神對ISE的時序約束比較熟悉,尤其是多周期約束這一塊。在Quartus中使用比較簡單,而且相關資料也比較多,但是ISE中的資料好像不是那么多,而且也沒有針對具體例子進行分析。官網上給出

2015-04-30 09:52:05

我使用ISE 13.4對設計的代碼進行邏輯綜合和布局布線等。寫的測試文件調用了一個RAM IP核,見圖1。其中test_HRV_top為測試文件,調用了RAM_fangzhen這個IP核和設計頂層

2015-08-29 16:55:16

XILINX ise打不開程序請問是什么原因?

2019-02-28 06:02:50

XILINX FPGA/CPLD ISE下載教程 第一章 XILINX FPGA/CPLD ISE下載教程——下載.bit文件第二章 XILINX FPGA/CPLD ISE下載教程——燒錄Flash 圖文詳細資料!

2019-08-15 00:32:31

《FPGACPLD設計工具──Xilinx+ISE使用詳解》

2018-01-12 15:04:43

Xilinx ISE 13.2 licenses 直接覆蓋.

2011-09-30 16:08:01

我在實驗室計算機上安裝Xilinx 11.2版時遇到問題。我從Xilinx設計工具網站下載了用于32位Windows系統的11.2 ISE設計套件,我下載的名為

2018-11-21 14:31:55

這些輸入外,還需要一個外部時鐘來鎖存此RGB數據。將此時鐘信號運行到PMOD上的通用I / O引腳會在Xilinx ISE中產生Place:1018錯誤。將錯誤覆蓋到Place:1019警告允許設計實現

2019-05-29 12:35:08

大家好,我正在使用Xilinx ISE 14.7(針對Virtex5,因此沒有Vivado),并且遇到了工具的問題,因此更改設計中的信號名稱會影響實現,從而影響時序,在某些情況下會略有變化比如說,一

2018-11-02 11:14:38

有人用Xilinx ISE的mig生成ddr2,然后進行調試的嗎?如果選擇了內含pll,頂層時鐘怎么連接

2014-09-15 19:14:41

約束設計與時序分析6.1 概述6.2 時序約束6.3 約束編輯器6.4 時序分析器6.5 本章小結第7章 可編程邏輯器件的高級設計7.1 概述7.2 宏生成器7.3 增量設計7.4 模塊化設計7.5

2012-02-27 14:43:30

喜我試圖在Xilinx ISE 14.1中使用Xpower Analyzer分析我的設計的功能,以實現vi??rtex6設計我的設計中有一個PLL,它提供20,80,100M o / p頻率

2019-04-16 15:25:00

本帖最后由 jzc1610 于 2016-6-15 17:56 編輯

附:xilinx ise 14.7 安裝包下載地址(直接打開迅雷,新建任務,復制粘貼鏈接即可):https

2016-06-15 09:13:23

xilinx ise 14.4套件在安裝過程中出現select a MATLAB,,怎么解決啊?

2013-03-20 23:17:04

請問下 現在的 xilinx ise哪個版本好用?謝了!

2012-06-19 10:15:45

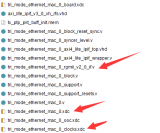

嗨,我安裝xilinx ise online(網絡安裝客戶端88.8MB)并使用正確的許可證注冊。但是,項目顯示為附件中的黃線列表。是因為我還是忘了安裝一些軟件嗎?謝謝,Deritha以上來自于谷歌

2018-11-19 14:25:54

大部分的時序分析和約束都寫在這里了。 一、基本時序路徑1、clock-to-setup周期約束跨時鐘域約束: (1)當源觸發器和目標觸發器的驅動時鐘不同,且時鐘的占空比不是50

2017-03-09 14:43:24

先生,我想產生一系列連續時間脈沖,將樣品轉化為沖動,如何在xilinx ise 13,.4中實現。

2020-04-17 07:23:48

分析器是否只假設中間數據是有規律的間隔?或者我該如何以不同的方式表達約束?以上來自于谷歌翻譯以下為原文I'm using a deserialization factor of 4 (4 data

2019-06-06 11:49:21

專家好,

CCS調試程序過程中,需要分析下各函數的執行時間,CCS中提供了性能分析器profile

Q1:性能分析器profile是否只能在Simulator下才能使用,Emulator下沒有這個功能?

Q2:性能分析器profile的使用方法是否有相應的教程參考?

謝謝

NanShan

2018-06-21 19:20:12

知道“時間分析器”和“planahead”可以幫助我,但我無法理解它的報告。我該怎么做才能解決時間問題。我找不到一些材料來幫助我理解“時序分析”,“代碼風格”,“如何糾正時間問題” ','時序收斂'等等

2019-03-18 13:37:27

約束文件(XDC文件),它包含用于時序分析的“create_clock”和“set_input_jitter”約束。在ISE 14.7和Spartan-3 FPGA中,我可以使用稱為“時鐘向導”的IP來

2019-08-02 09:54:40

的。來獲取關于原始的 ISE 設計套件以及 Xilinx 在 Vivado 中對這些開發工具做改進的理由的討論。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的設備,但是

2021-01-08 17:07:20

1818.8.1 布局布線流程1818.8.2 布局布線的實現1828.8.3 布局布線驗證1838.8.4 布局后時序評估1848.8.5 改變分區HDL1858.9 功耗分析1868.9.1 啟動功耗分析器

2012-04-24 09:18:46

技術10.4.2 基于FPGA的千兆以太網MAC控制器實現方案10.4.3 Xilinx 千兆以太網MAC IP Core10.5 本章小結第11章時序分析原理以及時序分析器的使用11.1 時序分析的作用

2012-04-24 09:23:33

功能完整,使用方便外,它的設計性能也非常好,拿ISE 9.x來說,其設計性能比其他解決方案平均快30%,它集成的時序收斂流程整合了增強性物理綜合優化,提供最佳的時鐘布局、更好的封裝和時序收斂映射,從而

2009-11-23 16:13:52

IP核使用: 1、用ISE生成一個PCIE IP核 2、快速使用IP核讓電腦識別 3、分析PCIE 接收數據時序,從無到有寫一個接收模塊 4、分析PCIE發送時序,從無到有寫一個發送模塊 學習目標

2022-02-14 09:50:22

剛剛接觸antlr詞法分析器只略看了些基本理論知識,關于做實例就完全不懂了,我想知道他需要什么樣的環境和軟件,以及軟件的下載地址.多謝各位了

2014-11-12 16:29:39

嗨,我們正在嘗試使用Vivado工具鏈手動路由FPGA,并想知道應該使用什么工具來手動路由Virtex 7 FPGA。還可以在Vivado時序分析器工具中指定溫度和電壓值來估算設計時序嗎?我們將如

2018-10-25 15:20:50

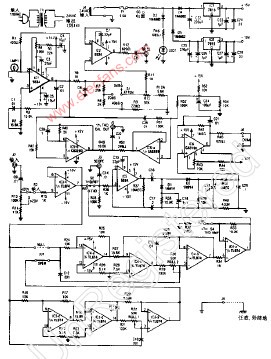

描述圖形音頻分析器 16x32

2022-08-24 06:38:03

我正在研究一種適用于Vedic Maths算法的乘法器。我想對傳統乘法器和vedic乘法器的時序延遲進行比較分析。我有spartan 3e和Xilinx 12.1時序分析器。請任何人都可以指導我

2019-07-04 06:36:45

新人請教如何從xilinx官網下載xilinx ise 10.1萬分感謝

2013-03-29 16:23:41

我是7系列FPGA的新手。最近開始使用Xilinx VC707板。在此之前,我曾經在Virtex 5上工作。我有一個ISE項目,使用Xilinx ISE和Chipscope使用Vitex 5板進行

2020-07-28 10:18:04

嗨,是否有任何文檔可以解釋如何使用Xilinx PlanAhead合并EDK和ISE系統? (我閱讀了Xilinx EDK概念,工具和技術指南......)關于Zynq-7000 SoC(在

2019-02-22 09:03:57

嗨,我是FPGA編程的新手。我在Xilinx ISE中使用VHDL進行設計。我的綜合結果包括:FF,LUT,內存LUT,I / O,BRAM,DSP48,BUFG。我非常感謝能夠幫助我解釋每個資源

2020-03-24 10:14:15

嗨,我剛剛安裝了ISE 14.7系統版本,并將System Generator鏈接到MATLAB(2014a)。但是當我嘗試打開simulink以使用Xilinx System Generator

2018-12-12 10:54:08

我們目前在計算機上安裝了Xilinx ISE 10.1,但我們需要CORDIC v4.0,它是新型Xilinx ISE 11.1的一部分。是否可以從Xilinx ISE 10.1升級到Xilinx

2018-11-16 11:48:15

嗨,我在級聯模式下使用Xilinx DCM(數字時鐘管理器),使用6.144 MHz時鐘生成48 kHz時鐘。但是,由于我的設計相當大(在區域內),這種配置無法滿足時序約束并對整個設計產生影響。因此

2019-03-25 14:09:18

最近在學習FPGA,因為Xilinx家的芯片國內用的最多,故使用了XC6SLX16。但在安裝Xilinx ISE時發現無法導入license,網絡上尋找了下方法,實測可行,故在這分享給大家。以下

2021-05-17 08:00:00

的寫法是一致的,后文將詳細明。3.寄存器-寄存器的時序約束寄存器-寄存器的約束,在同步時序電路中,就是周期的約束。對于完全采用一個時鐘的電路而言,對這一個clk指定周期約束即可。但是如果采用了多個時鐘

2019-07-09 09:14:48

多道脈沖幅度分析器的結構是怎樣設計的?多道脈沖幅度分析器的硬件是如何設計的?怎樣去設計多道脈沖幅度分析器的相關軟件?怎樣對多道脈沖幅度分析器的硬件電路進行仿真測試?

2021-04-14 06:31:11

求賜xilinx ise軟件!!!

2019-03-19 05:59:29

能,識別可靠的蹤跡,檢測建立和保持時間的配合,時序分析器不要求用戶產生輸入激勵或測試矢量。雖然Xilinx與Altera在FPGA開發套件上擁有時序分析工具,但在擁有第三方專門時序分析工具的情況下,僅利用

2021-06-24 08:00:01

鍵盤掃描程序,xilinx提供,設計文件用ISE打開 設計文件

Project Navigator Auto-Make Log File

2009-06-14 09:26:28 37

37 FPGACPLD設計工具——Xilinx ISE使用詳解的主要內容:第1章 ISE系統簡介第2章 工程管理器與設計輸入工具第3章 ModelSim仿真工具第4章 ISE中集成的綜合工具第5章 約束第6章

2009-07-24 16:06:58 197

197 可編程邏輯器件cpld 和fpga 以及xilinx webpack 4.2 ISE 的介紹;用xilinxwebpack 4.2 ISE 設計七段譯碼器的顯示.關鍵詞 ASIC Xinlinx

2009-08-15 09:21:52 22

22 ISE時序約束:What effects do timing constraints have on your project?• The implementation tools do

2010-01-11 08:54:06 87

87 轉換到TimeQuest時序分析器教程(電子書)

2010-03-23 16:49:43 0

0 xilinx ISE設計套裝10.1下載

2010-04-17 16:15:18 1915

1915 使用時鐘PLL的源同步系統時序分析一)回顧源同步時序計算Setup Margin = Min Clock Etch Delay – Max Data Etch Delay – Max Delay

2010-10-05 09:47:48 31

31 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2010-11-03 16:24:44 121

121 Xilinx ISE Design Suite 12.4 現在將更好地幫助您全面提升和改進設計。

Spartan-6 FPGA 將靜態功耗削減 30%,性能提升 12%

AMBA 4 AXI4 工具和 IP 支持現已開始投產,可滿足即插即用

2010-12-23 21:55:07 1294

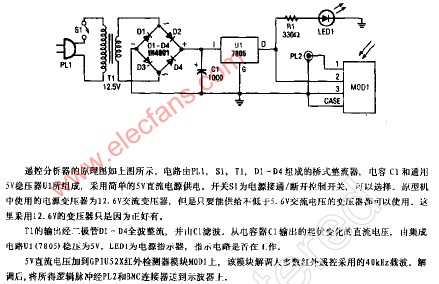

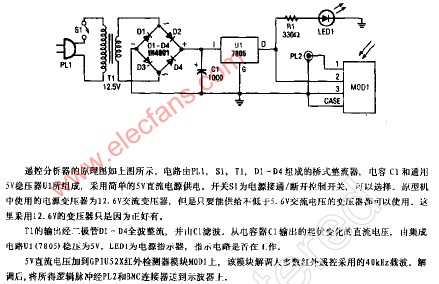

1294 遙控分析器

2009-09-18 14:14:38 456

456

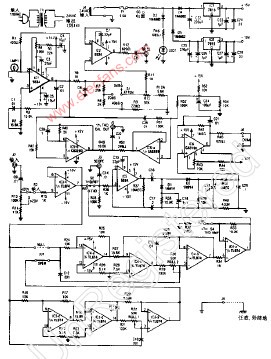

諧波失真分析器

電路包括一個1KHZ的低失真

2009-09-23 14:34:24 757

757

網絡分析器,網絡分析器原理是什么?

網絡分析器

具有發現并解決各種故障特性的硬件或軟件設備

2010-03-22 11:25:21 993

993 協議分析器在WLAN中的應用

協議分析器廣泛應用于有線網絡,成為一類極有用的測試和維護工具。然而,在WLAN領域,這個問題很有可

2010-03-29 17:11:30 483

483 為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。 FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時

2011-01-04 11:26:35 1991

1991 Fortify的靜態代碼分析器(Static Code Analyzer,SCA)是組成Fortify 360的三個分析器之一。SCA工作在開發階段,以用于分析應用程序的源代碼是否存在安全漏洞。這種類型的分析與程序跟蹤分析

2011-04-07 20:32:46 22

22 XILINX推出ISE Design Suite 13.2最新版.

2011-07-11 18:22:11 3385

3385

本教程主要是向ISE的初學者描述和演示, 在XILINX的ISE集成軟件環境中如何用VHDL和原理圖的方式進行設計輸入如何用 ModelSim 仿真工具對設計進行功能仿真和時序仿真如何實現設計.

2011-11-01 14:44:07 0

0 基于Xilinx ISE的modelsim仿真教程

2015-11-30 15:52:56 8

8 Xilinx ISE9.1使用全流程中文書

2016-01-18 15:30:43 0

0 xilinx_ise9.01中文教程 xilinx_ise9.01中文教程

2016-02-18 18:16:58 0

0 Xilinx時序約束設計,有需要的下來看看

2016-05-10 11:24:33 18

18 Xilinx-ISE9.x-FPGA-CPLD設計指南合集

2022-03-22 18:03:09 76

76 xilinx-ise 新手教程VHDL的,感興趣的可以看看。

2016-09-27 15:19:03 77

77 談到數字邏輯,談到FPGA設計,每位工程師都離不開時鐘。這里我們簡單介紹一下xilinx 7 系列中的時鐘資源。時鐘設計的好壞,直接影響到布局布線時間、timing的收斂情況,FPGA的時鐘

2017-02-08 05:33:31 561

561

Xilinx ISE使用錯誤和警告匯總,具體的跟隨小編一起來了解一下。

2018-07-13 06:10:00 5848

5848 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 4223

4223 在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 8891

8891

目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-11-25 01:43:01 1411

1411 員帶來了更高的設計生產力。 2)新版 ISE 設計套件與前版有什么區別? ISE設計套件首次提供了“智能”時鐘門控技術,可將動態功耗降低多達 30%。針對加密、數據路徑和計算密集型設計,甚至還能進一步降低功耗。新套件還提供了基于時序的高級設計保存功能、符合

2018-07-02 06:20:00 897

897 詳細講解了xilinx的時序約束實現方法和意義。包括:初級時鐘,衍生時鐘,異步時終域,多時終周期的講解

2018-01-25 09:53:12 6

6 這一次給大家分享的內容主要涉及Xilinx FPGA內的CLBs,SelectIO和Clocking資源,適合對FPGA設計有時序要求,卻還沒有足夠了解的朋友。

2018-03-21 14:48:00 4672

4672

xilinx的ise的使用流程,簡單介紹

2018-06-06 13:46:00 3432

3432 了解有關作為英特爾?圖形性能分析器一部分的資源歷史記錄功能的更多信息

2018-11-12 06:40:00 2241

2241 FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 1894

1894

本文檔的主要內容詳細介紹的是xilinx ISE的視頻教程免費下載。

2020-03-23 08:00:00 8

8 全局時鐘資源是一種專用互連網絡,它可以降低時鐘歪斜、占空比失真和功耗,提高抖動容限。Xilinx的全局時鐘資源設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達CLB、IOB和BRAM的延時最小。

2020-12-29 16:59:35 8

8 這個命令指定clock之間是異步關系,時序分析時會完全ignore這些clock之間的path。

2022-12-12 09:49:11 1725

1725 時序約束是我們對FPGA設計的要求和期望,例如,我們希望FPGA設計可以工作在多快的時鐘頻率下等等。因此,在時序分析工具開始對我們的FPGA設計進行時序分析前,我們必須為其提供相關的時序約束信息

2022-12-28 15:18:38 1893

1893 FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 768

768 很多人詢問關于約束、時序分析的問題,比如:如何設置setup,hold時間?如何使用全局時鐘和第二全局時鐘(長線資源)?如何進行分組約束?如何約束某部分組合邏輯?如何通過約束保證異步時鐘域之間

2023-05-29 10:06:56 372

372

基于RGMII時序廣泛應用于以太網通信中,基于Xilinx的三速以太網時序分析,不同的Xilinx系列方法不一樣

2023-07-07 14:15:01 2952

2952

為什么異步fifo中讀地址同步在寫時鐘域時序分析不通過? 異步FIFO中讀地址同步在寫時鐘域時序分析不通過的原因可能有以下幾個方面: 1. 讀地址同步在寫時鐘域時序分析未覆蓋完全 在時序分析時,可能

2023-10-18 15:23:55 312

312

電子發燒友App

電子發燒友App

評論