1 UART原理

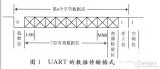

串行通信是指外部設備和計算機間使用一根數據線(另外需要地線,可能還需要控制線)進行數據傳輸的方式。數據在一根數據線上一位一位傳輸,每一位數

2010-08-02 09:37:50 2476

2476

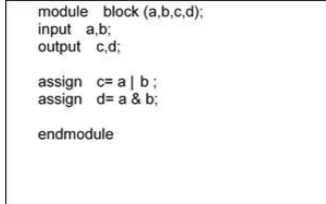

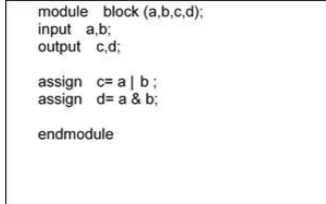

Verilog的基本設計單元是“模塊”(block)。一個模塊是由兩部分組成的,一部分描述接口,另一部分描述邏輯功能,即定義輸入是如何影響輸出的。

2019-06-26 15:30:40 11375

11375

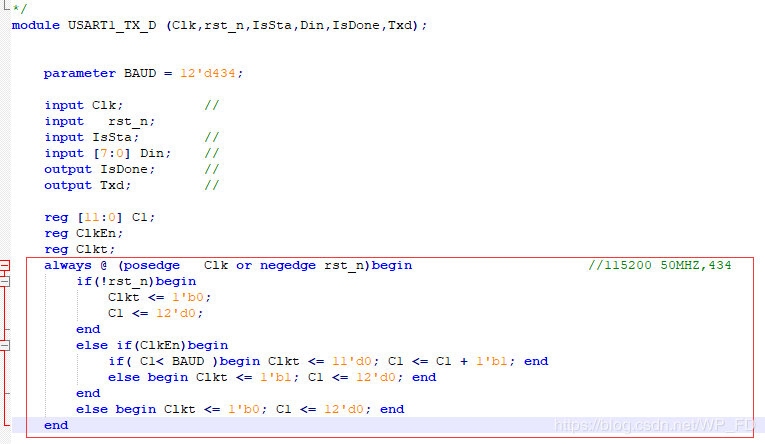

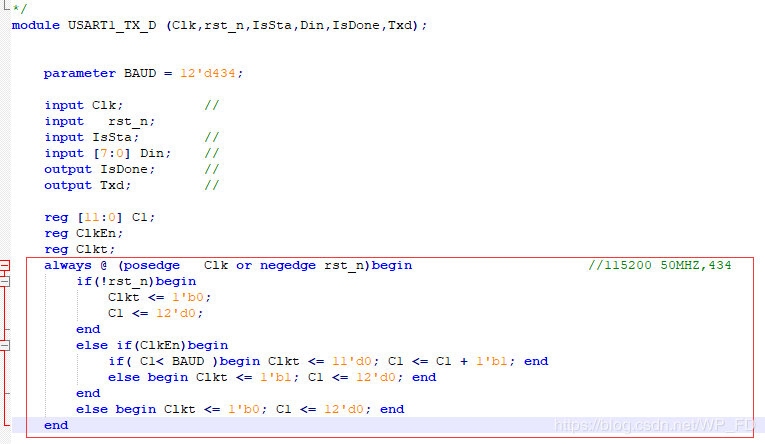

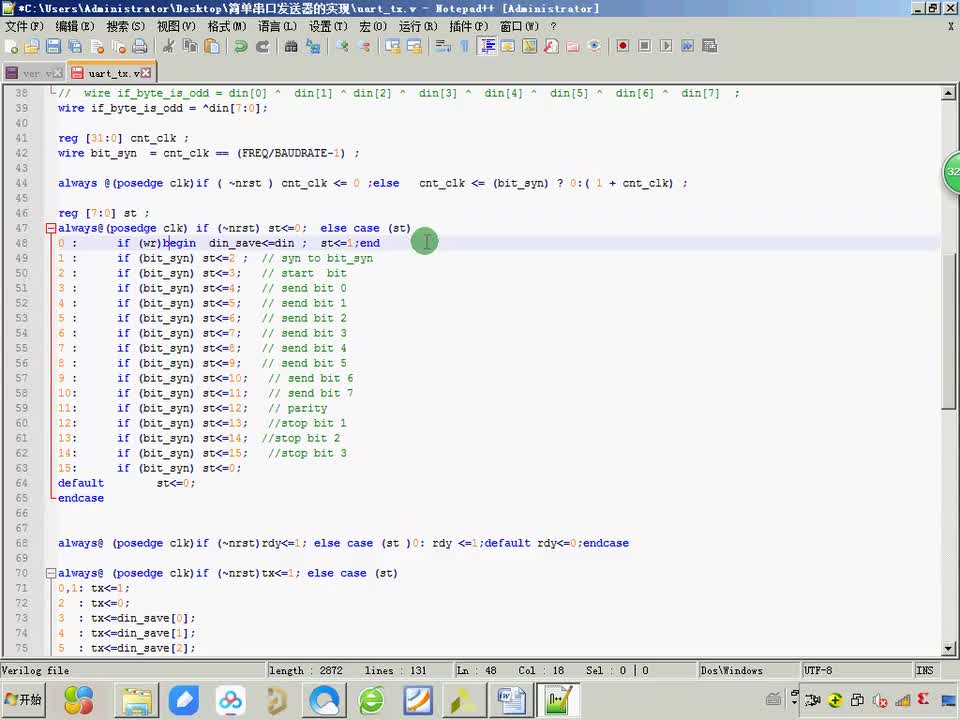

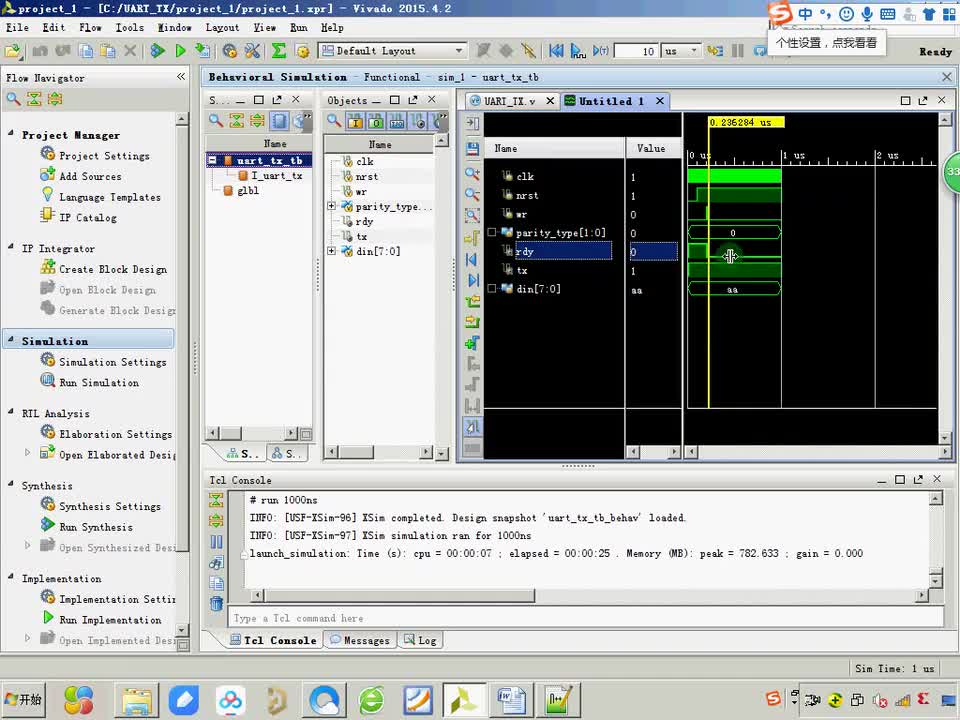

在 ZYNQ進階之路2 中我們講解了PL端PWM呼吸燈的設計,本節我們講解PL端實現串口UART的發送設計; 首先新建一個串口發送的工程,工程建立在ZYNQ進階之路1中已經講述,這里不再累述; 下面

2020-11-25 17:26:21 3067

3067

通用異步收發傳輸器(Universal Asynchronous Receiver/Transmitter),通常稱作UART。它將要傳輸的資料在串行通信與并行通信之間加以轉換。作為把并行輸入信號轉成串行輸出信號的芯片,UART通常被集成于其他通訊接口的連結上。

2023-01-05 09:48:46 2395

2395 特權同學的《FPGA/CPLD邊學邊練---快速入門Verilog/VHDL》中的UART串口收發實驗發送數據和接收的數據不一致。在每個有效數據的后面都會多兩個數據。比如發送的有效數據是:FF。則

2017-11-30 09:25:44

Verilog實現接收的數據進行發送。

2017-05-19 23:03:45

今天學習了UART的相關知識,完成了用上位機輸入字符串然后在虛擬終端上進行顯示。首先應該將設I|O口的功能設置為UART,具體有PINSEL來實現。然后是UART的初始化,主要要先是DLB=1,即另

2013-11-29 21:13:23

1.1 FPGA雙沿發送之Verilog HDL實現1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿發送之Verilog HDL實現;5)結束語。1.1.2 本節

2021-07-26 06:20:59

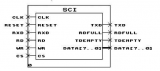

`UART 主要由 UART 內核、信號監測器、移位寄存器、波特率發生器、計數器、總線選擇器和奇偶校驗器總共 7 個模塊組成,如圖 5-5 所示。圖 5-5 UART 實現原理圖UART 各個模塊

2018-10-18 09:51:47

實例通過IIC接口定時讀取RTC中的時、分、秒寄存器,同時將時、分、秒數據通過UART發送到PC上的串口調試助手進行實時的顯示。 2 模塊劃分本實例模塊劃分如圖所示。●Iic_controller.v

2016-04-05 11:57:20

本帖最后由 mr.pengyongche 于 2013-4-30 03:27 編輯

dsp設計100問(之二)[url=www.7773.cc]

2011-10-30 22:10:12

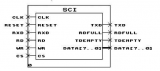

UART 內核模塊是整個設計的核心,所以它也是整個設計中最為復雜的模塊。由于 UART 內核模塊的整體結構比較復雜,下面的內容將從模塊接口、狀態機設計和實現代碼 3 方面介紹UART 內核的實現方法

2018-10-24 09:58:36

做完相應修改即可實現單次將內存緩沖區數據以DMA方式通過UART0發送出去,效果如下。此外,如果想周期性觸發或者條件性觸發,則只需再相應位置添加“DMAMUX0_CHCFG0

2015-01-19 14:33:36

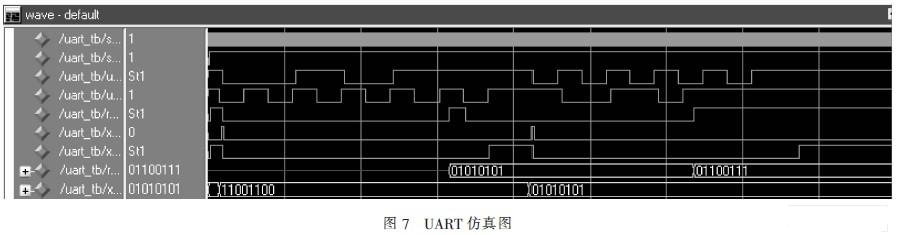

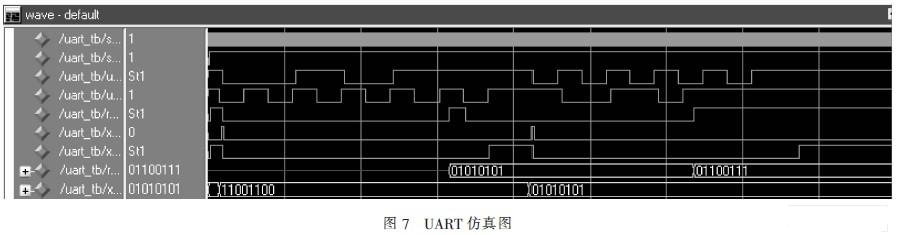

的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA片上UART的設計,給出了仿真結果。關鍵詞:通用異步收發器;串口通信;現場可編程邏輯器件;有限狀態機

2019-06-21 07:17:24

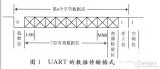

低電平)、8 位數據位、偶校驗、停止位(1 b 高電平) , 波特率可調。 2 波特率發生模塊 設計的UART 的接收和發送按照相同的波特率進行,波特率可以通過接口模塊的總線接口進行設置

2015-02-05 15:33:30

從零開始學習Z-Stack之二歡迎研究ZigBee的朋友和我交流。。。

2012-08-12 22:02:22

本人對于uart串口通訊理解比較混亂,不知道設計的uart接收模塊和發送模塊應該怎么連接,串口通信是把串行數據接收,然后經過接收模塊轉換成并行數據,然后再經過發送模塊一位一位發出去嗎?還是說,串行

2017-12-18 10:47:28

如圖所示在uart中怎么用verilog實現輸出A轉換到a

2019-10-16 16:26:11

//;=================================================================*//; 模塊功能說明: UART Transmit

2014-07-08 23:08:28

跪求各位大神有沒有基于verilog HDL的高速對數運算模塊設計的CORD IC算法實現自然對數運算的代碼

2016-03-10 12:39:28

串行通信的工作方式有哪些?如何實現Verilog串口發送及接收一個字節數據呢?

2021-11-11 06:48:39

怎么實現STM32 UART HAL數據發送?

2021-12-14 07:18:54

的按鈕,電話應用程序將數據通過藍牙發送到模塊,模塊將uart發送到目標。目標響應,模塊從uart接收數據并將數據發送回電話。當然可以。

2020-04-20 10:07:50

大家好,我的問題是,我想發送一個完整的數組由250個整數元素(這意味著它的大小是1000),通過UART1端口在我的PIC32 MX795F512H。下面的代碼顯示了我的UART的初始配置

2019-03-12 15:12:37

發燒友們好,我正在開始學習fpga的知識,現在尋求一個基于verilog的uart程序,要求是初始位一位,終止位一位,數據位8位,實現回環功能。大家能幫助一下我嗎?

2020-05-10 22:53:19

請問Verilog怎么實現UART/RS232/RS485收發自動校調功能,降低接收誤碼率?

2021-06-21 07:27:16

UART 4 UART參考設計,Xilinx提供Verilog代碼 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 本文介紹了I2C總線規范,并根據該規范對I2C進行模塊化設計,用Verilog HDL 語言對每個模塊進行具體描述,并通過模塊之間的調用,基本實現了I2C的主機從機的發送和接收功能。

2009-06-15 10:44:03 144

144 文章介紹了一種采基于FPGA 實現UART電路的方法,并對系統結構進行了模塊化分解以適應自頂向下的設計方法。采用有限狀態機對接收器模塊和發送器模塊進行了設計,所有功能的

2009-08-15 09:27:55 46

46 文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。UART 的波特率可設置調整,工作狀態可讀取。系統結構進行了模塊化分解,使之適應自頂向下(Top-Down)的設計

2009-08-21 11:35:03 52

52 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 簡述了I2C總線的特點;介紹了開發FPGA時I2C總線模塊的設計思想;給出并解釋了用Verilog HDL實現部分I2C總線功能的程序,以及I2C總線主從模式下的仿真時序圖。

2009-10-19 10:49:16 104

104 本文設計了一種基于 FPGA 的UART 核,該核符合串行通信協議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環境下進行設計、仿真,

2009-11-27 15:48:51 17

17 IO模擬UART實現

本應用用于擴展UART端口,在單片機自帶的UART口不夠用的情況下,使用GPIO和定時器實現模擬UART通信。可增加兩個模擬的UART模塊。

2010-03-26 09:20:40 68

68 文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實現UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 用Verilog實現8255芯片功能

2010-11-03 17:06:09 144

144 摘 要 :UART是廣泛使用的串行數據通訊電路。本設計包含UART發送器、接收器和波特率發生器。設計應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2009-06-20 13:14:52 982

982

C8051F310設計的UART擴展實現

UART數據發送協議作為一種簡單的數據發送協議,被大量的使用在當前各種數字外設的數據傳輸上。但是現在的PC機存在無UART接口或接口較

2010-05-27 10:15:41 2452

2452

Name : uart // File Name?? : uart.v// Function??? : Simp

2010-06-05 12:12:03 6236

6236 MAX3109先進的雙通用異步接收發送器(UART)的有128字的接收和發送先進先出(FIFO),它一個高速SPI?或I 2 C控制接口

2011-04-15 10:17:32 1768

1768

本文介紹的基于Wishbone總線的UART IP核的設計方法,通過驗證表明了各項功能達到預期要求,為IP核接口的標準化設計提供了依據。此外,該IP核代碼全部采用模塊化的Verilog-HDL語言編寫,

2011-06-10 11:47:37 3479

3479

在xo640上實現一個簡單的Uart,能夠解析串口數據,并在寄存器中存儲,用FIFO實現數據的傳遞。那么后期可以通過開發板上的串口經CPLD訪問各種數據。比如PC=CPLD=EEPROM等等,極大方便后期

2011-08-05 16:54:46 1741

1741 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。

2011-12-17 00:15:00 57

57 數字系統設計:VERILOG實現 (第2版)

2015-11-30 10:21:33 0

0 STM32 UART 發送數據丟失最后一個字節

2015-12-04 15:10:46 0

0 verilog語言開發的串口模塊程序,測試可用。

2015-12-25 10:25:19 5

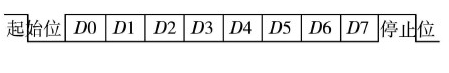

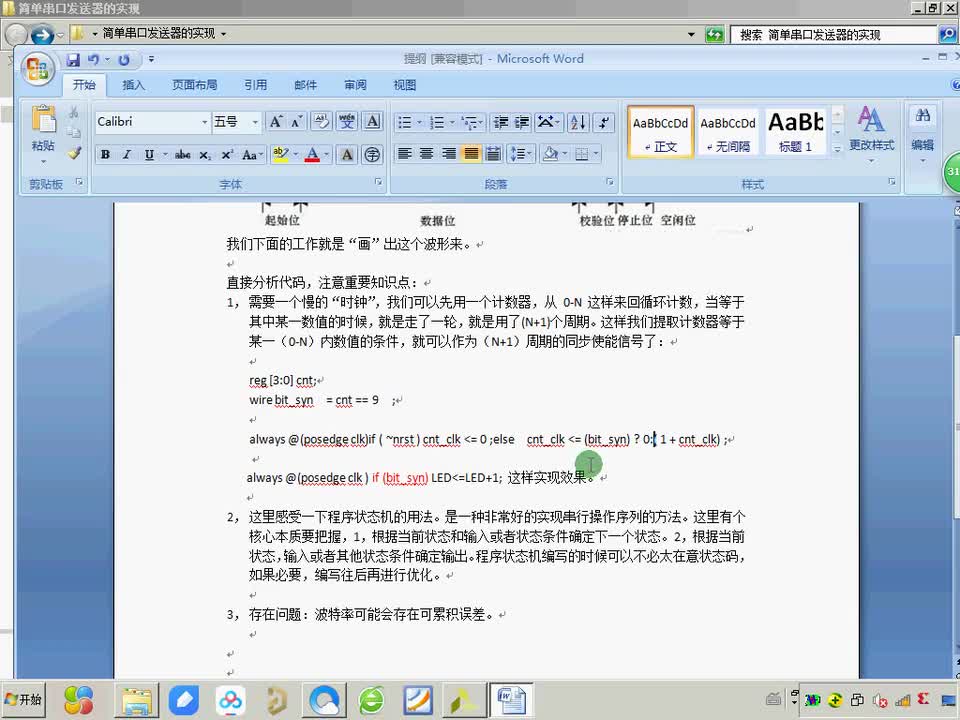

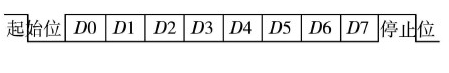

5 異步串行數據的一般格式是:起始位+數據位+停止位,其中起始位1位,8位數據位,奇校驗、偶校驗或無校驗位;停止位可以是1、2位,LSB first: 2.接收原理: 由于UART是異步傳輸,沒有傳輸

2017-02-09 09:41:11 778

778

將AD采集的結果發送到串口,Verilog程序

2017-04-05 11:20:37 0

0 NiosⅡ的UART設計與實現

2017-10-31 15:09:03 17

17 Verilog是描述復雜的硬件電路,設計人員總是將復雜的功能劃分為簡單的功能,模塊是提供每個簡單功能的基本結構。

2017-11-20 16:49:36 5370

5370

使用Verilog描述硬件的基本設計單元是模塊(module)。構建復雜的電子電路,主要是通過模塊的相互連接調用來實現的。模塊被包含在關鍵字module、endmodule之內。實際的電路元件。Verilog中的模塊類似C語言中的函數

2017-12-08 17:20:57 9710

9710 和UART優缺點的基礎,提出了一種基于FPGA采用硬件設計HCI-UART的實現方式。本設計在Quartus II 9.0集成設計環境下,采用硬件描述語言Verilog分模塊設計完成,設計經過Modelsim 6.4a仿真與驗證。

2017-12-11 13:22:51 10881

10881

STM32 UART_發送數據丟失最后一個字節

2018-04-10 11:23:41 3

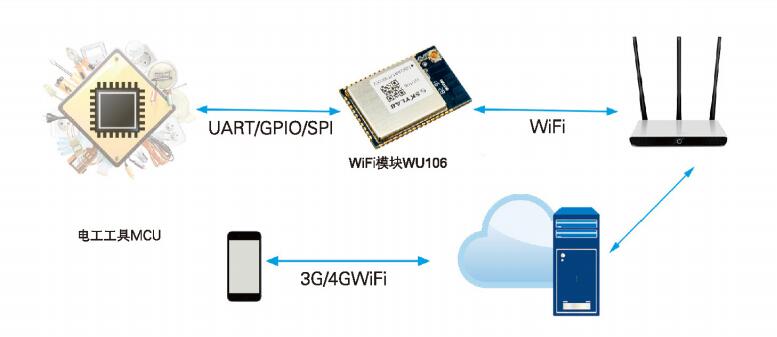

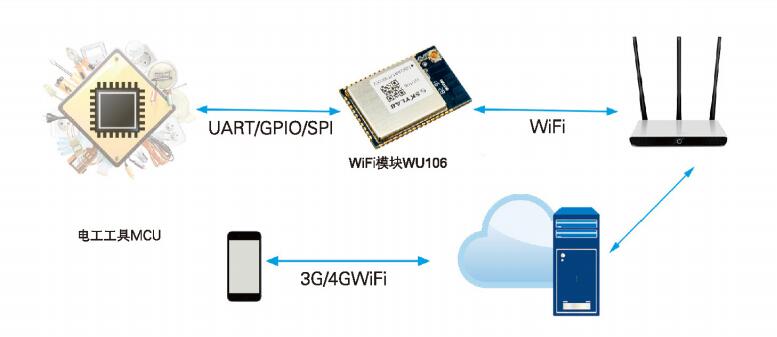

3 棧和IEEE802.11協議棧,能夠實現用戶串口到無線網絡之間的轉換。UART接口WiFi模塊UART接口WiFi模塊是基于UART接口的符合WiFi無線網絡標準的嵌入式模塊,內置無線網絡協議IEEE802.11

2018-08-09 19:01:00 6699

6699 實現RS-232電平和TTL/CMOS電平轉換可以用接口芯片來實現,實現數據的串行到并行轉換用的是UART,它們是實現串行通信必不可少的兩個部分。雖然目前大部分處理器芯片中都集成了UART,但是一般

2019-10-18 07:54:00 2317

2317

本文檔的主要內容詳細介紹的是常用模塊的Verilog HDL設計詳細資料免費下載。

2018-10-16 11:12:54 20

20 字符發送的過程描述:在UART的發送過程中先將數據輸入到發送數據寄存器中(TDR)此時(TXE)被硬件置1,之后TDR寄存器將數據串行移入到發送移位寄存器中,將數據在TX端口發送,此時(TC)被硬件置1。發送與接收是逆過程。

2018-11-08 16:59:25 8795

8795 TCP/IP協議棧,能夠實現用戶串口或TTL電平數據到無線網絡之間的轉換。串口WiFi模塊工作方式分別是透傳模式和命令模式,透傳模式下,不管發送什么數據給模塊,模塊都不會進行處理(退出透傳模式的相關指令

2019-01-14 09:27:02 9728

9728

接收控制模塊與發送控制模塊內部都有一個波特率時鐘產生模塊(BuadRate_set),用于將電路輸入時鐘(clk)進行分頻產生波特率時鐘,用于接收和發送數據控制。

2019-02-04 11:21:00 3596

3596

UART(UniversalAnynchrONousReceiverTransmitter,通用異步接收發送器)是廣泛應用的串行數據傳輸協議之一,其應用范圍遍及計算機外設、工控自動化等場合。雖然

2019-08-30 15:05:04 1410

1410

UART(UniversalAnynchrONousReceiverTransmitter,通用異步接收發送器)是廣泛應用的串行數據傳輸協議之一,其應用范圍遍及計算機外設、工控自動化等場合。雖然

2019-09-03 09:01:10 2011

2011

UART需要使用DMA發送嗎?

2020-03-07 16:57:28 6537

6537 HDL和VHDL的使用比率大概是80%和20%,在中國,大多數電子行業企業都采用Verilog。而模塊化的設計讓Verilog HDL語言具有思路清晰、邏輯關系明確、可讀性強等特點,模塊化的設計在 Verilog HDL語法設計中也成為主流。

2020-03-25 08:00:00 4

4 的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 15:51:05 7

7 的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 17:28:03 10

10 本文主要介紹verilog基礎模塊,夯實基礎,對深入學習FPGA會有很大幫助。

2022-02-08 15:04:08 1966

1966

本教程解釋了如何在基于Verilog的設計中包含Altera的庫模塊,這些設計是使用Quartus R:II軟件實現的。

2021-01-22 15:34:12 4

4 FPGA邏輯設計中通常是一個大的模塊中包含了一個或多個功能子模塊,verilog通過模塊調用或稱為模塊實例化的方式來實現這些子模塊與高層模塊的連接,有利于簡化每一個模塊的代碼,易于維護和修改。

2021-04-30 09:30:45 25

25 1、 關于如何在VHDL模塊調用一個Verilog模塊 在VHDL模塊聲明一個要與調用的Verilog模塊相同名稱的元件(component),元件的名稱和端口模式應與Verilog模塊的名稱和輸入

2021-04-30 14:06:04 8673

8673

選的是一個周期高電平,也可兩個)(無校驗位) 1、prescale是完成一個bit需要主時鐘計數的次數(其和主時鐘以及波特率之間的關系參考網上文章) 2、進入uart模塊的異步信號,最好使用提供的同步器同步 3、異步復位信號最好使用提供的同步器同步 4、波特率任

2021-05-27 18:05:00 2174

2174 基于FPGA的UART模塊設計與實現介紹說明。

2021-06-01 09:43:30 19

19 FPGA設計中DAC控制的Verilog實現(單片機電源維修)-該文檔為FPGA設計中DAC控制的Verilog實現資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 MCU-串口發送實現例程倉庫:https://gitee.com/ll0_0ll/MCU-UART1.串口發送寄存器為空中斷+RingBuff初始化一段內存空間作循環隊列發送數據時,先將數據放到循環

2021-10-28 12:21:01 10

10 功耗,并且集成了豐富的外設模塊,可以滿足工業和消費等多種應用。MSP430FR2311中的eUSCI_A0支持UART通訊,本文對此UART模塊的寄存器配置進行了詳細的分析和計算,以幫助工程師對此

2022-01-11 10:43:11 1727

1727 單片機pic24GPIO模擬uart發送我們經常遇到那種uart資源不夠的情況,這時就需要使用gpio來模擬uart資源。下面就是使用兩個定時器和兩個gpio來完成模擬。‘’’void

2021-11-16 13:51:02 5

5 TMC2225模塊UART調試TMC2225模塊UART調試硬件連線串口調測TMC2225模塊UART調試TMC2225可以通過UART配置相關參數。比較簡便的是通過PC的串口進行調測。硬件連線硬件

2021-12-04 16:36:09 34

34 Uart比較簡單,所以僅對tx作比較詳細的注釋,但里面一些內容還是值得新手學習的

2022-07-01 17:08:50 1304

1304 電子發燒友網站提供《USB轉UART轉換器模塊.zip》資料免費下載

2022-07-19 10:46:50 4

4 有人使用STM32H743做產品開發, DMA 傳輸待發送的數據到 UART 發送寄存器做后續UART通信。在開啟D-Cache的情況下,發現UART沒法發送更新過的數據。

2022-11-23 09:02:19 951

951 UART協議由三根線組成,Tx,Rx,Gnd即發送、接收與地,不包含時鐘線,屬于全雙工異步串行通信協議。

2022-12-15 12:10:46 590

590 實現一個在ARM中通過APB總線連接的UART模塊(Universal Asynchronous Receiver/Transmitter),包括設計與驗證兩部分。

2023-06-05 11:48:38 954

954

和接收部分相反,UART發送數據部分是CPU將需要發送的數據寫到發送數據寄存器(TX_DATA),發送模塊進行數據的發送。

2023-06-05 15:59:52 1695

1695

433模塊是一種常用的無線通信模塊,用于實現短距離無線通信。在433模塊中,一般有發送和接收兩種模式。

2023-06-12 17:41:01 7277

7277 電子發燒友網站提供《UART發送數據丟失最后一個字節.pdf》資料免費下載

2023-08-01 17:57:48 1

1 在芯片設計中,UART(Universal Asynchronous Receiver/Transmitter,通用異步接收/發送器)模塊是一個非常重要的外設模塊。

2023-10-09 14:10:59 642

642 時,它保持在高電壓電平。為了開始數據傳輸,發送 UART 將數據線從高電平拉到低電平(從 1 到 0)。接收 UART 在數據線上檢測到這種從高到低的變化,并開始讀取實際數據。通常,只有一個起始位。 數據位:數據位是從發送方傳輸到接收方的

2023-11-09 17:42:21 263

263 以用來實現與其他外設或者外部設備的數據交互。 然而,在一些情況下,用戶可能會遇到UART3無法發送數據的問題。在接下來的文章中,我們將深入探討這個問題,并提供一些解決方案。 首先,我們需要確定問題出現的具體情況。當UART3無法發送數據時,我們可以逐步排除可能的原因。首先,我們

2024-01-09 10:57:21 344

344 眾所周知,序列發送模塊可以不需要腳本代碼實現測試中特定控制報文序列的發送,該模塊多用于循環順序控制的測試案例中。序列發送模塊的常用場景,主要是針對一些新開發的產品需要通過該模塊來驗證產品功能等等

2024-02-19 14:00:11 114

114

第一部分:簡介 1.1 什么是Verilog模塊? 在Verilog中,模塊是其設計層次結構的基本單元。模塊是一個用于實現特定功能的單獨的硬件單元。它可以是一個組合邏輯電路,也可以是一個時序邏輯電路

2024-02-22 15:56:25 325

325 Verilog是一種硬件描述語言(HDL),廣泛應用于數字電路設計和硬件驗證。在Verilog中,模塊是構建電路的基本單元,而模塊端口對應方式則用于描述模塊之間信號傳遞的方式。本文將介紹

2024-02-23 10:20:32 190

190

正在加载...

電子發燒友App

電子發燒友App

評論