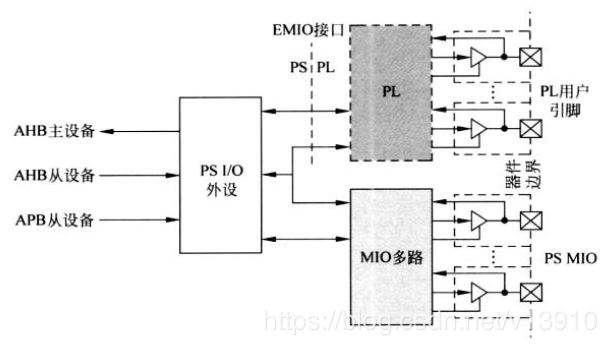

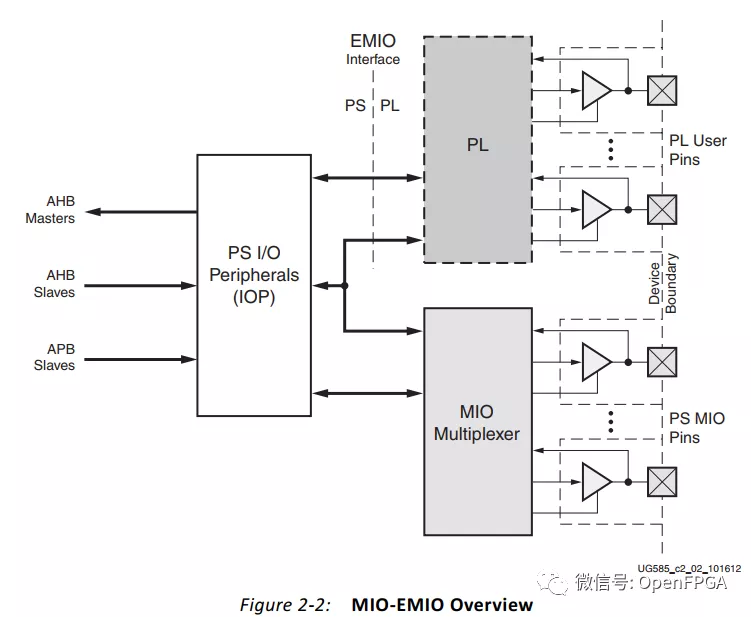

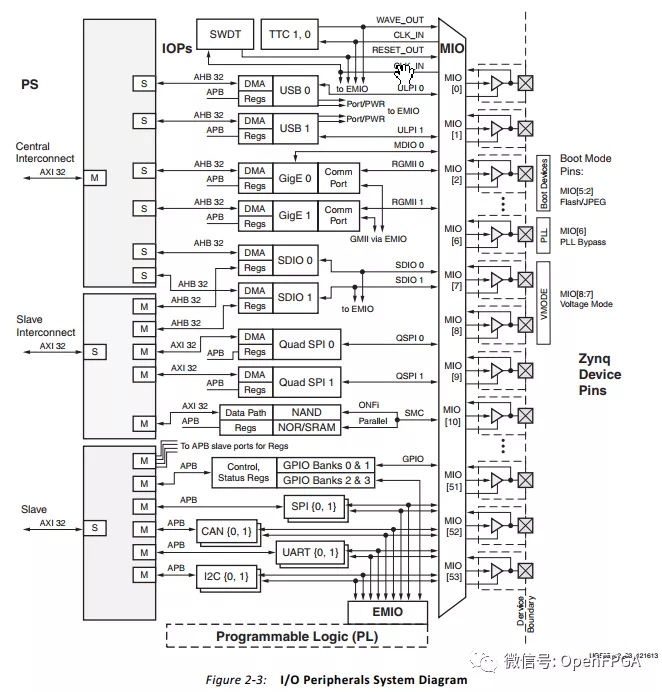

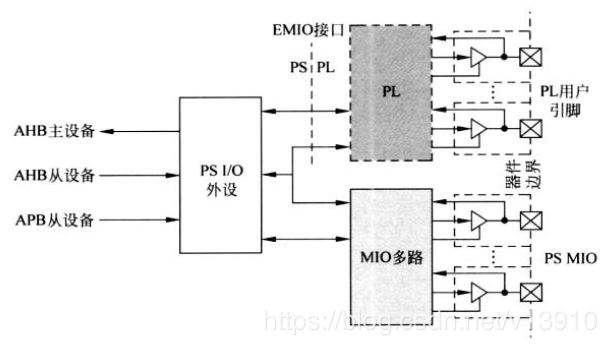

通過(guò)AXI點(diǎn)亮PL端LED。 1. MIO與EMIO 首先來(lái)理清楚MIO與EMIO的關(guān)系。MIO是PS的I/O引腳,一共有54個(gè),分為Bank0與Bank1,可以接許多外設(shè)比如UART、SPI或GPIO

2020-11-24 14:32:33 20374

20374

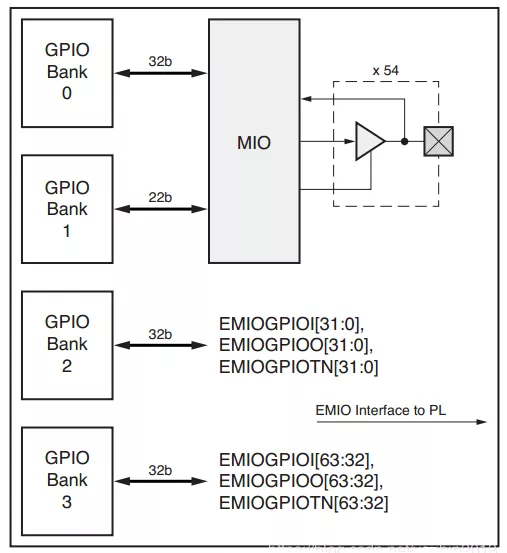

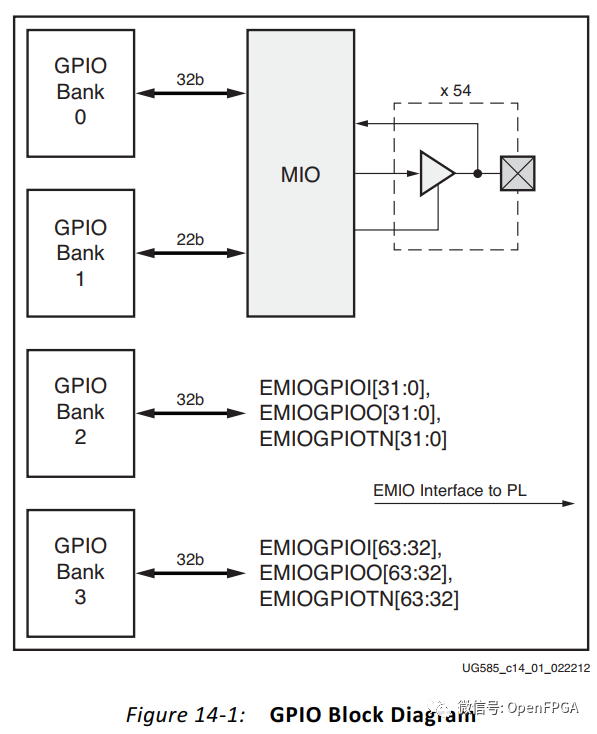

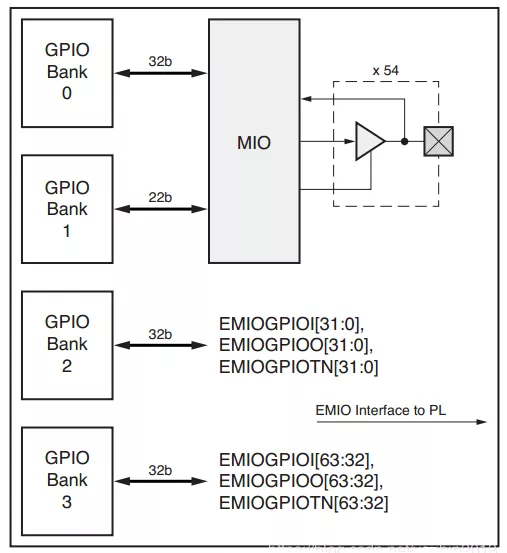

GPIO的結(jié)構(gòu)體系 zynq的GPIO,分為兩種,MIO(multiuse I/O)和EMIO(extendable multiuse I/O)。 ZYNQ的GPIO由4個(gè)BANK組成,其體系結(jié)構(gòu)

2020-12-09 11:41:46 3059

3059

;AXI_GPIO是封裝好的IP核,PS通過(guò)M_AXI_GPIO接口控制PL部分實(shí)現(xiàn)IO,使用時(shí)消耗管腳資源和邏輯資源。 使用的板子是zc702。 1.MIO方式 Zynq7000 系列芯片有 54

2020-12-26 10:12:57 3306

3306

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-02-02 07:30:07

ZYNQ-7000的USB轉(zhuǎn)JTAG驅(qū)動(dòng)無(wú)法使用 使用操作系統(tǒng)是win7 64位 有人遇到過(guò)這個(gè)問(wèn)題嗎?

2013-07-10 22:06:48

上,也可以通過(guò) EMIO 連接到 PL 端的引腳。Zynq-7000 系列芯片一般有 54 個(gè) MIO,個(gè)別芯片如 7z007s 只有 32 個(gè)。GPIO 是英文“general purpose I

2022-02-08 07:27:16

。

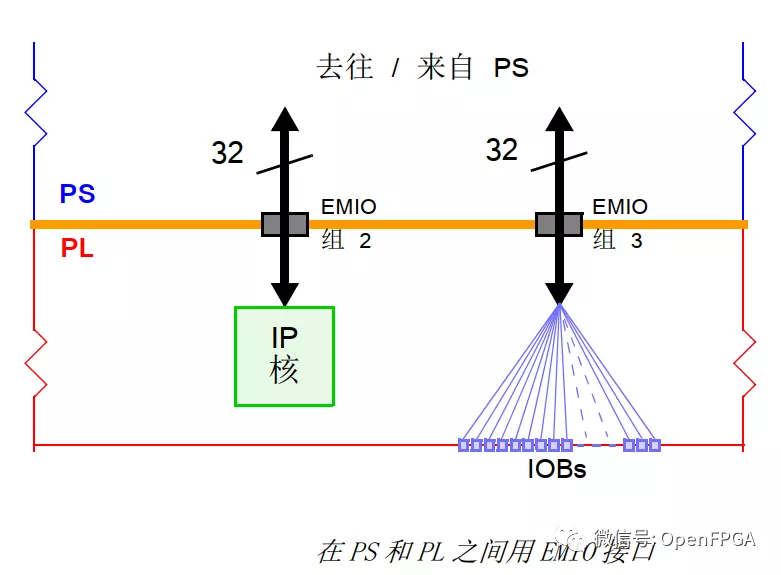

③EMIO :由于MIO管腳有限,PS端可以通過(guò)EMIO訪問(wèn)PL端引腳。

④GP :通用AXI接口,用來(lái)實(shí)現(xiàn)一般主從互聯(lián)、數(shù)據(jù)交互,不用于高性能。

⑤HP :是高性能/帶寬的標(biāo)準(zhǔn)接口,主要用于PL訪問(wèn)PS上

2023-11-03 10:51:39

ZYNQ學(xué)習(xí)筆記_GPIOGPIO介紹MIO介紹EMIO介紹控制GPIO接口的寄存器原理GPIO介紹GPIO的英文全稱為General-purpose input/output,即一種通用外設(shè),可以

2022-02-08 07:30:36

真隨機(jī)數(shù)發(fā)生器在安全解決方案中起著重要作用。真正的隨機(jī)數(shù)發(fā)生器通常由平臺(tái)支持,例如Exynos 5,OMAP 3,4 SoC系列和飛思卡爾i.MX53。我已經(jīng)閱讀了zynq-7000的TRM,但沒有找到隨機(jī)數(shù)生成器。 zynq真的不支持RNG嗎?

2020-07-17 14:27:09

ArduZynq 和 TE0726-03M ZynqBerry SBC 中的 Zynq Z-7010 SoC 的 FPGA 容量存在顯著差異。雖然所有 Zynq-7000 SoC 都采用雙核 Arm

2018-08-31 14:43:05

Zynq-7000是什么?Zynq-7000能干什么?有何作用?

2021-06-30 06:22:55

你好, 我試圖通過(guò)使用XADC讀取模擬信號(hào)。我有Zynq-7000板。我找不到引腳分配文件。要將模擬信號(hào)輸入到從vaux0到vaux15的16個(gè)通道,我應(yīng)該如何與XADC接頭建立輸入連接? 非常感謝。 :)

2020-05-07 08:15:58

我正在使用Zynq-7000,選擇欲望頻率,我知道我應(yīng)該使用-g ConfigRate,但這些設(shè)置數(shù)字是什么意思?例如,默認(rèn)數(shù)字是3,這意味著頻率是300KHz?謝謝

2020-08-05 13:14:33

有關(guān)Zynq-7000里面ARM和FPGA數(shù)據(jù)傳輸是怎么實(shí)現(xiàn)的?求大神解答

2022-07-25 14:42:00

) 的英國(guó)學(xué)者所著,為您詳細(xì)介紹 Xilinx? Zynq?-7000 All Programmable SoC。本書包含了 Zynq-7000 SoC 開發(fā)的方方面面,從硬件到軟件,從理論到實(shí)現(xiàn)

2014-09-04 11:37:18

CPUCPU為Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平臺(tái)升級(jí)能力強(qiáng),以下為Xilinx Zynq-7000特性參數(shù):TLZ7xH-EasyEVM

2022-01-03 07:50:21

今天給大俠帶來(lái)簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn),話不多說(shuō),上貨。Xilinx的ZYNQ系列FPGA是二種看上去對(duì)立面的思想的融合,ARM處理器的串行執(zhí)行+FPGA的并行執(zhí)行

2021-11-09 06:43:27

CPUCPU為Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平臺(tái)升級(jí)能力強(qiáng),以下為Xilinx Zynq-7000特性參數(shù):電源接口和開關(guān)采用12V3A

2021-12-30 07:55:37

Zynq上的APU接口里包含了(ACP)加速一致性接口和(GIC)中斷接口。 通用外設(shè) Zynq-7000 AP SoC內(nèi)部包括很多常見的I/O外設(shè)(IOP)和存儲(chǔ)器接口,是PS的重要組成部分。這些I

2015-07-07 20:22:49

。本章我們將學(xué)習(xí)GPIO中EMIO接口信號(hào)的使用。本章包括以下幾個(gè)部分:33.1簡(jiǎn)介3.2實(shí)驗(yàn)任務(wù)3.3硬件設(shè)計(jì)3.4軟件設(shè)計(jì)3.5下載驗(yàn)證3.1簡(jiǎn)介ZYNQ GPIO接口信號(hào)被分成四組,分別是從

2020-08-29 16:20:36

視頻太大了,無(wú)法上傳,直接分享百度網(wǎng)盤了介紹一下內(nèi)容【黑金ZYNQ7000系列原創(chuàng)視頻教程】20.Linux下的GPIO操作【黑金ZYNQ7000系列原創(chuàng)視頻教程】19.Linux下的hello

2016-11-14 21:04:04

RJ45插頭實(shí)現(xiàn)GE_T模式的電口應(yīng)用。Zynq-7000 PS部分包含兩個(gè)千兆以太網(wǎng)MAC層硬核,因此還需要以太網(wǎng)物理層傳輸芯片實(shí)現(xiàn)千兆以太網(wǎng)接口。MAC層硬核所對(duì)應(yīng)的接口引腳,既可從PS端的MIO引腳

2021-10-22 09:43:10

的收發(fā)器,可為多攝像頭駕駛員輔助系統(tǒng)和 4K2K 超高清電視等大量嵌入式應(yīng)用實(shí)現(xiàn)高度差異化的設(shè)計(jì)。Zynq-7000 SoC 系列集成 ARM 處理器的軟件可編程性與 FPGA 的硬件可編程性,不僅

2018-06-07 15:36:43

描述該參考設(shè)計(jì)是一種可擴(kuò)展的電源設(shè)計(jì),旨在為基于 FPGA 的 Artix-7、Spartan-7 和 Zynq-7000 系列器件供電。此設(shè)計(jì)接收來(lái)自標(biāo)準(zhǔn)直流電源的電力,并通過(guò)明確的 Samtec

2019-01-03 13:47:48

親愛的先生,我們正在為Zynq-7000 soc尋找USB主機(jī)驅(qū)動(dòng)程序。請(qǐng)為此提供支持感謝致敬以上來(lái)自于谷歌翻譯以下為原文Dear Sir,we are loooking for USB host

2019-04-03 10:28:34

`本次測(cè)試使用廣州創(chuàng)龍開發(fā)板 TLZ7x-EasyEVM(基于Xilinx Zynq-7000 SoC高性能低功耗處理器,集成PS端單核/雙核Cortex-A9 ARM + PL端 Artix-7

2018-06-08 10:13:57

如何實(shí)現(xiàn)Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)?

2021-12-23 08:53:58

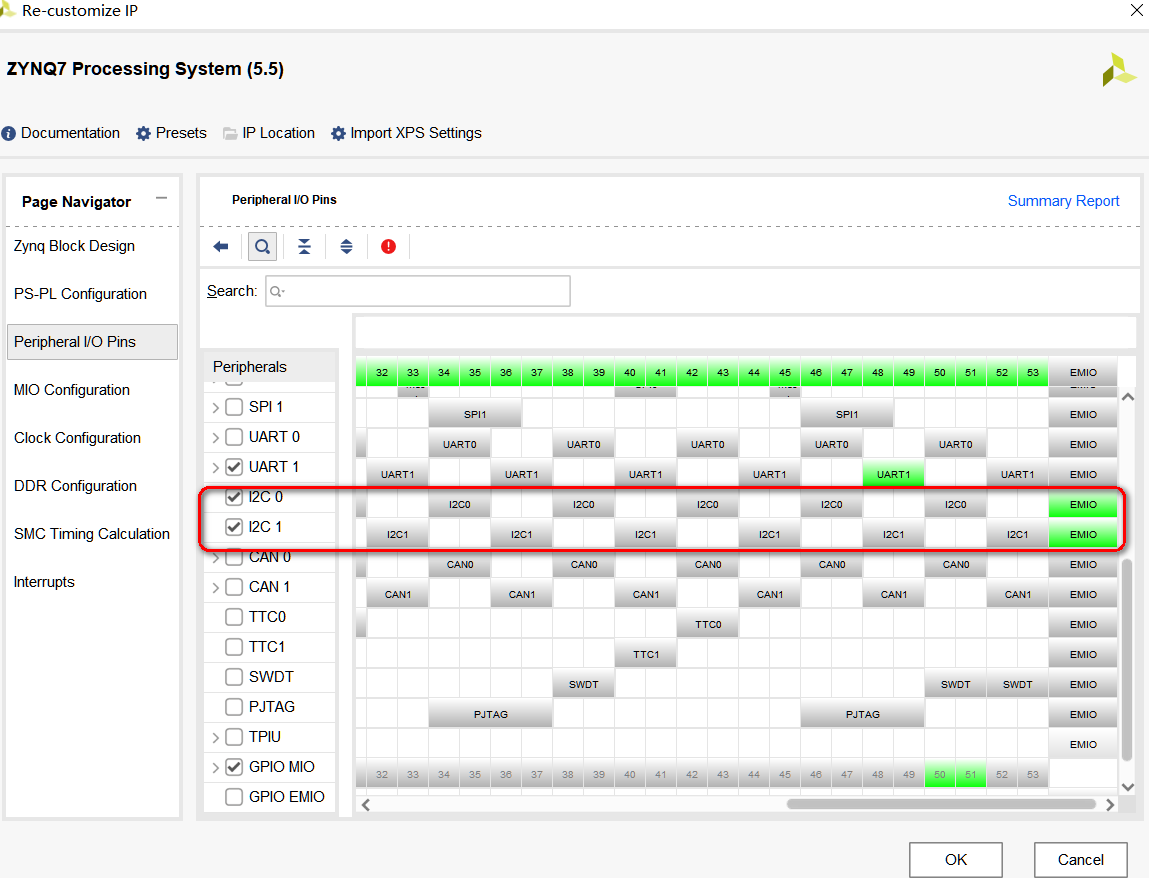

可以通過(guò)EMIO接口連接到PL(最多支持64個(gè)輸入引腳或128個(gè)輸出引腳)。GPIO外設(shè)可以分為4個(gè)Bank。 GPIO外設(shè)的主要特性如下: ● 54個(gè)GPIO信號(hào)通過(guò)MIO引腳引出。 ● 192個(gè)

2019-04-18 16:33:51

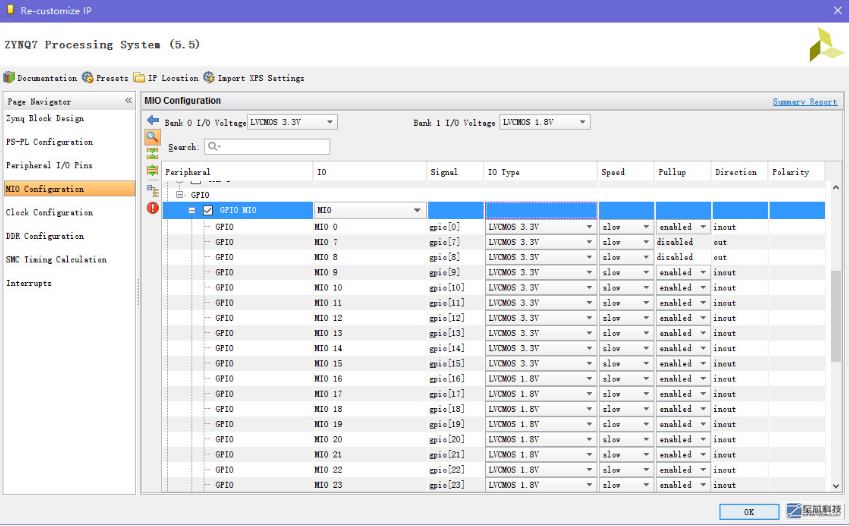

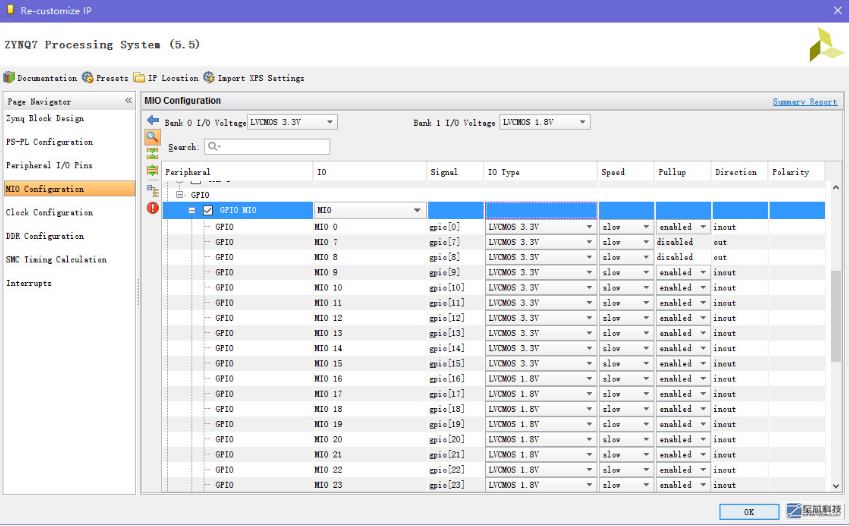

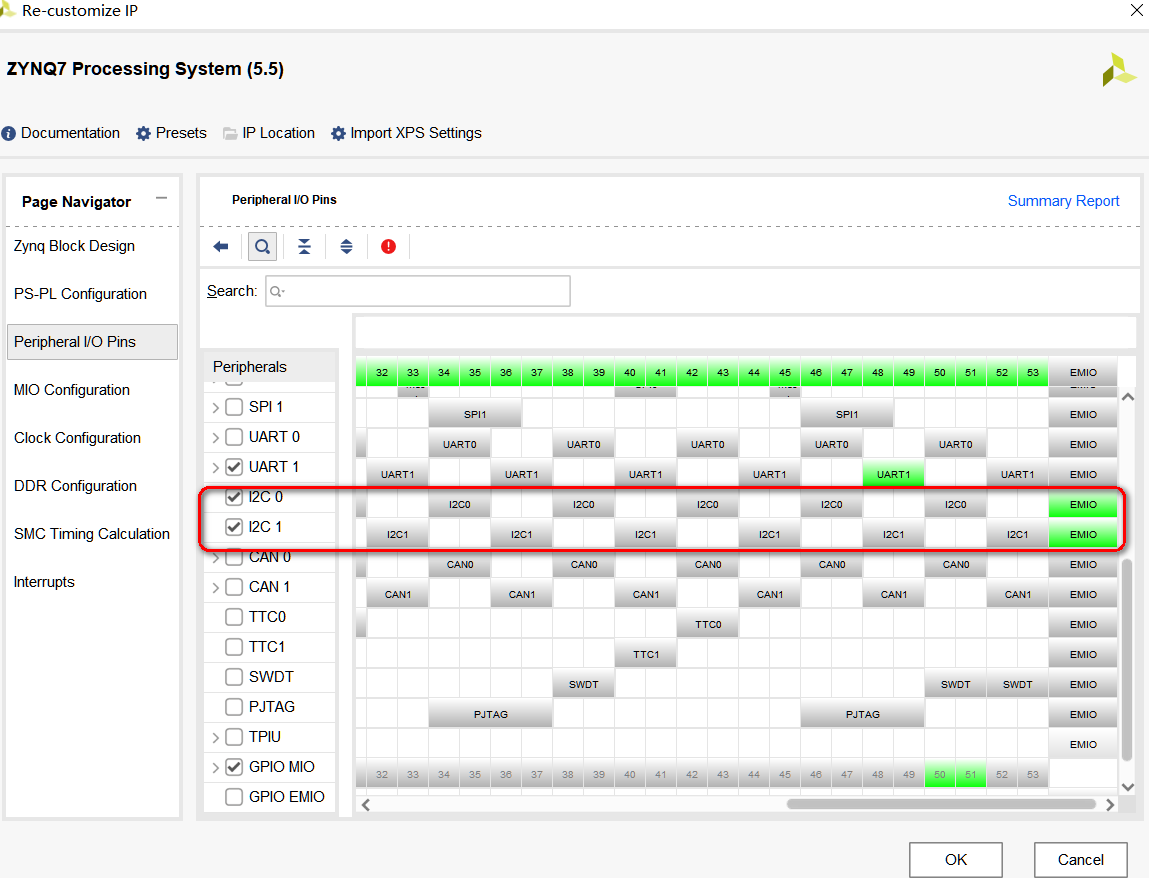

GPIO的PS系統(tǒng)配置打開ZYNQ7 ProcessingSystem的配置頁(yè)面Peripheral I/O Pins,可以看到右側(cè)若勾選GPIO MIO選項(xiàng),在對(duì)應(yīng)的MIO號(hào)若點(diǎn)擊變綠,則表示該MIO號(hào)

2019-10-10 11:21:06

該EMIO功能開啟,EMIO引腳將會(huì)引出到PS系統(tǒng)。完成配置后,回到ZYNQ7系統(tǒng)框圖中,可以看到多了一個(gè)名為GPIO_0的接口。展開GPIO_0接口,實(shí)際上有3組64bit的信號(hào),分別代表input

2019-10-12 17:35:16

最近在學(xué)習(xí)使用時(shí)碰到一些麻煩,還望幫助啊。就是想知道如何在Zynq-7000中進(jìn)行FPGA邏輯設(shè)計(jì),產(chǎn)生LTE-A信號(hào),從而輸入到AD9361,搭建成一個(gè)mimo軟件無(wú)線電平臺(tái)。。

2015-04-03 11:03:46

的可擴(kuò)展處理平臺(tái)(EPP), 賽靈思在今年3月發(fā)布了基于Zynq -7000新系列的首批器件。 采用28 nm制造工藝, Zynq-7000嵌入式處理平臺(tái)系列的每款產(chǎn)品均采用帶有NEON及雙精度浮點(diǎn)引擎

2019-05-16 10:44:42

Zynq-7000系列中的 4 款產(chǎn)品具有完全相同的 ARM 處理系統(tǒng),但是可編程邏輯資源的可擴(kuò)展性有所不同, 因而適用于不同的應(yīng)用。

2011-03-09 09:29:23 1612

1612 賽靈思Zynq-7000 可擴(kuò)展處理平臺(tái)(EPP)將雙 ARM Cortex-A9 MPCore 處理器系統(tǒng)與可編程邏輯和硬 IP 外設(shè)緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。

2011-08-09 10:07:52 3280

3280

Zynq-7000系列是Xilinx推出的首款可擴(kuò)展式處理平臺(tái)(EPP)。該新型產(chǎn)品將業(yè)界標(biāo)準(zhǔn)ARM雙核Cortex-A9 MPCore處理系統(tǒng)與Xilinx一體化28nm可編程邏輯架構(gòu)完美整合在一起。

2012-01-26 19:02:25 1663

1663

近日,賽靈思公司(Xilinx)在2012 年ARM技術(shù)大會(huì)(ARM TechCon 2012)上宣布推出系列解決方案,進(jìn)一步擴(kuò)大Zynq-7000 All Programmable SoC在可信系統(tǒng)中的應(yīng)用,確保其滿足嚴(yán)格的安全標(biāo)準(zhǔn)要求。開發(fā)

2012-11-05 13:34:42 740

740 部分IO資源概述 在新的Zynq UltraScale+系列器件中,PS端的IO得到了增強(qiáng): a) MIO由Zynq-7000的54個(gè)增加到78個(gè); b)除GTR信號(hào)外,所有其他的PS外設(shè)均可

2017-02-08 08:29:11 491

491

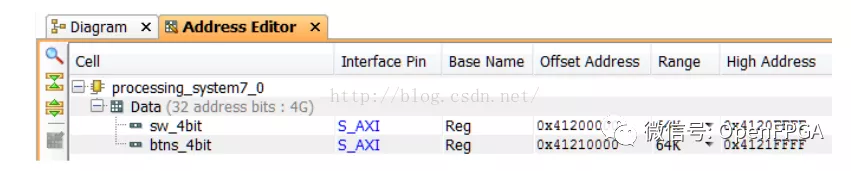

GPIO的博客說(shuō)的有一些不一樣呢。 我們先看有哪三種GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接掛在PS上的GPIO。而AXI_GPIO是通過(guò)AXI總線掛在PS上的GPIO

2017-02-08 10:23:12 2711

2711

以2個(gè)Cortex A9的ARM核為核心,還包括片上存儲(chǔ)器、片外存儲(chǔ)器接口(DDR)和一系列的外設(shè)接口。Zynq-7000系列將ARM CPU和外設(shè)集成在一個(gè)芯片內(nèi),使得Zynq-7000系列皆具處理器和FPGA雙重特性,特別適用于軟硬件協(xié)同設(shè)計(jì)。

2017-11-18 05:11:01 18880

18880

本文試圖搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53:00 2492

2492 用在工業(yè)控制,馬達(dá)驅(qū)動(dòng),測(cè)試和測(cè)量,嵌入式視角系統(tǒng)以及軟件定義無(wú)線電和嵌入系統(tǒng)模塊.本文介紹了Zynq-7000系列特性,框圖以及MicroZed開發(fā)電路板主要特性,框圖,電路圖和材料清單.

2018-05-05 14:32:00 2932

2932

因?yàn)?b class="flag-6" style="color: red">Zynq-7000 PS(Processing System)端嵌入了Cortex-A9 ARM 處理核以及PL(Programmable Logic)端為基于Kintex-7或者Artix-7

2018-05-18 07:07:00 2584

2584 Zynq-7000 AP SoC作為業(yè)界第一款SoC產(chǎn)品,完美集成了雙核ARM Cortex-A9處理器與賽靈思28 nm FPGA。本視頻向您展示了Zynq-7000的強(qiáng)大性能,以及豐富的外設(shè)支持及開發(fā)工具支持情況,讓您能更快地尋找到Zynq-7000的相關(guān)信息和支持資源。

2018-06-05 01:45:00 4172

4172

賽靈思隆重推出Zynq-7000

2018-06-06 03:45:00 3874

3874

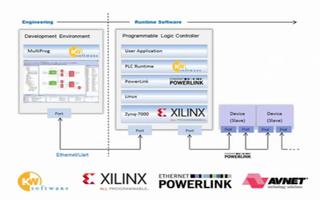

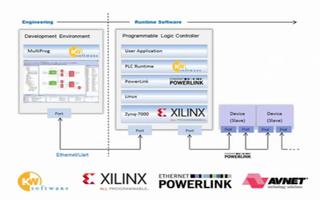

基于Zynq-7000平臺(tái)運(yùn)行SoftPLC的解決方案,集成了KW-SoftPLC,PowerLink實(shí)時(shí)以太網(wǎng)協(xié)議,Linux操作系統(tǒng),用以快速、精準(zhǔn)的實(shí)現(xiàn)工業(yè)控制應(yīng)用

2018-06-05 09:46:00 5215

5215

Xilinx Zynq-7000 EPP Showcased at Embedded World

2018-06-04 13:46:00 2881

2881 Xilinx公司介紹:Zynq-7000 AP SoC 在多種應(yīng)用領(lǐng)域中的演示。

2018-06-04 13:47:00 4466

4466 除了要最終客戶推出屢獲殊榮的Zynq-7000 AP SoC器件幫助他們?cè)诟?jìng)爭(zhēng)中整整領(lǐng)先一代之外,我們今天還推出了豐富的穩(wěn)健可靠的基礎(chǔ)架構(gòu),使Zynq-7000 SoC用戶能夠生產(chǎn)力更高

2018-06-04 13:47:00 3212

3212

XILINX Zynq-7000, Industrial & Medical Imaging Demos - EW 20

2018-05-25 15:49:00 2878

2878 Zynq-7000 Extensible Processing Platform in Action

2018-05-24 16:47:00 3013

3013 我們先看有哪三種GPIO:MIO、EMIO、AXI_GPIO。其中MIO和EMIO是直接掛在PS上的GPIO。而AXI_GPIO是通過(guò)AXI總線掛在PS上的GPIO上。

2018-07-07 08:23:00 4944

4944 GPIO功能,PS部分通過(guò)M_AXI_GP接口來(lái)控制該GPIO IP模塊;另外EMIO模塊雖然使用PS部分GPIO但也使用了PL部分的管腳資源。MIO方式實(shí)現(xiàn)GPIOvivado中zynq設(shè)置如下圖由圖中

2018-08-07 10:16:49 2708

2708

Zynq-7000 PL端HDMI的顯示控制 Zynq-7000 PS到PL端emio的使用 Vivado 專家文章:Tcl 是什么? Zynq-7000 ARM端MIO的使用 Zynq-7000

2019-09-15 14:57:00 3305

3305 Xilinx處理平臺(tái)副總裁Vidya Rajagopalan和ARM物理IP部門技術(shù)副總裁Dipesh Patel介紹了Xilinx的Zynq-7000可擴(kuò)展處理平臺(tái)。

2018-11-20 07:07:00 3318

3318 Zynq-7000 All Programmable SoC評(píng)估套件ZC702簡(jiǎn)介使設(shè)計(jì)人員能夠快速評(píng)估Zynq-7000技術(shù),同時(shí)通過(guò)其可擴(kuò)展性開發(fā)大多數(shù)應(yīng)用。

2018-11-20 06:17:00 3656

3656 觀看世界上第一個(gè)可擴(kuò)展處理平臺(tái)--Zynq-7000 EPP的演示。

2019-01-02 09:31:00 2062

2062 Zynq-7000全可編程SoC提供無(wú)與倫比的性能和功能

2019-01-21 07:32:00 3212

3212 Xilinx為Zynq-7000 SoC提供了一個(gè)穩(wěn)健而廣泛的支持基礎(chǔ),讓用戶基于Zynq的開發(fā)設(shè)計(jì)更加高效,同時(shí)也幫助客戶更快地把設(shè)計(jì)推向市場(chǎng).Zynq-7000 SoC的用戶對(duì)Vivado

2018-11-30 06:08:00 2321

2321 安富利展示了一個(gè)集成的工業(yè)物聯(lián)網(wǎng)(IoT)系統(tǒng),集成了Xilinx Zynq-7000 All Programmable SoC上的機(jī)器視覺,電機(jī)控制和近場(chǎng)通信(NFC)。

2018-11-26 07:00:00 2840

2840 該演示展示了Zynq-7000 All Programmable SoC及其使用NEON引擎或硬件加速來(lái)加速軟件的能力。

查看Zynq-7000 SoC的靈活性,以加速軟件和利用......

2018-11-26 06:56:00 4796

4796 Xilinx及其聯(lián)盟成員在Embedded World 2012上展示了Zynq-7000可擴(kuò)展處理平臺(tái)。

2018-11-26 06:42:00 2330

2330 了解可用于Zynq-7000 All Programmable SoC的各種開發(fā)工具。

從愿景到部署Xilinx開發(fā)工具解決端到端開發(fā)問(wèn)題,包括:系統(tǒng)設(shè)計(jì),軟件和固件開發(fā)......

2018-11-26 06:38:00 3032

3032 了解設(shè)計(jì)人員在使用Zynq-7000 All Programmable SoC器件時(shí)可用的不同I / O,從標(biāo)準(zhǔn)I / O到串行收發(fā)器以及模擬輸入。

2018-11-26 06:36:00 2547

2547 了解MIO和EMIO如何相關(guān)以及如何使用首選的PlanAhead / XPS流將信號(hào)傳遞到“真實(shí)世界”。

2018-11-26 06:27:00 3272

3272 了解如何構(gòu)建FSBL,U-boot,Linux并為Zynq-7000 All Programmable SoC制作可引導(dǎo)映像。

2018-11-23 06:55:00 2470

2470 通過(guò)Zynq-7000 AP SoC了解電源管理技術(shù),并了解Zynq Power Demonstration的這些技術(shù)。

2018-11-22 06:54:00 3500

3500 本視頻將向您講解如何使用Zynq-7000 VIP(驗(yàn)證IP)來(lái)高效地驗(yàn)證基于Zynq-7000處理系統(tǒng)的設(shè)計(jì)。另外,視頻還介紹了如何配置,以及如何使用范例項(xiàng)目進(jìn)行仿真的實(shí)施步驟。

2018-11-22 06:48:00 3995

3995 ZYNQ-7000如何生成從Flash和SD卡啟動(dòng)的鏡像文件 將PL與PS部分一起使用,并且通過(guò)JTAG下載到板子運(yùn)行。對(duì)于ZYNQ,有多種啟動(dòng)方式

2018-12-01 08:38:18 7278

7278

本文檔的主要內(nèi)容詳細(xì)介紹的是Zynq-7000全可編程SOC系列產(chǎn)品選擇指南免費(fèi)下載。

2019-02-15 11:52:09 9

9 ?Cortex?-A9處理器與業(yè)界領(lǐng)先的每瓦28nm可編程邏輯性能相集成,實(shí)現(xiàn)了超過(guò)離散處理器和FPGA系統(tǒng)的功率和性能水平。Zynq-7000系列提供了Dualcore(Zynq-7000設(shè)備

2019-02-15 11:52:14 20

20 Xilinx Zynq-7000 SOC和7系列FPGA內(nèi)存接口解決方案核心提供了到DDR3和DDR2 SDRAM、QDR II+SRAM、RLDRAM II/RLDRAM 3和LPDDR2 SDRAM的高性能連接。

2019-02-25 17:24:55 17

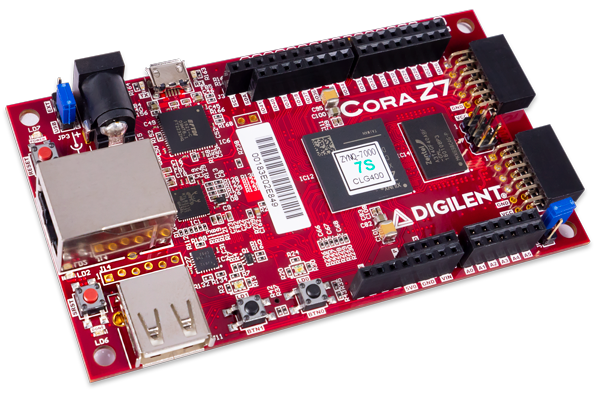

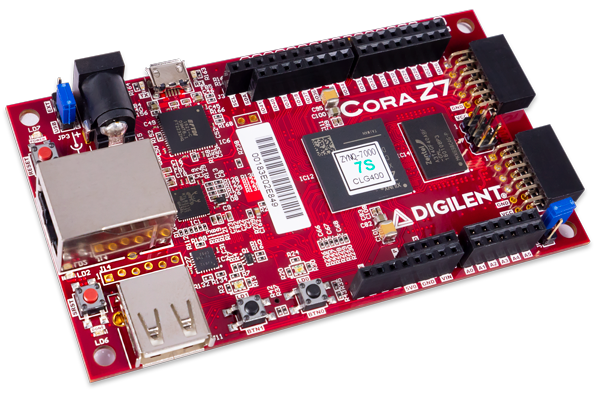

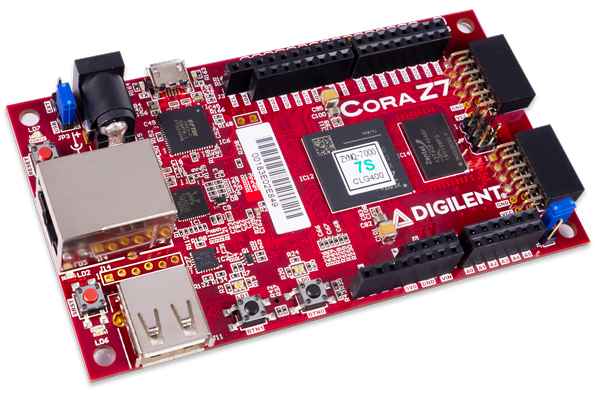

17 Digilent Cora Z7是一款隨時(shí)可用,低成本且易于嵌入的開發(fā)平臺(tái),圍繞Xilinx功能強(qiáng)大的Zynq-7000全可編程片上系統(tǒng)(APSoC)而設(shè)計(jì)。 Zynq-7000架構(gòu)將單核

2019-11-14 15:53:23 2148

2148

Digilent Cora Z7是一款隨時(shí)可用,低成本且易于嵌入的開發(fā)平臺(tái),圍繞Xilinx功能強(qiáng)大的Zynq-7000全可編程片上系統(tǒng)(APSoC)而設(shè)計(jì)。 Zynq-7000架構(gòu)將單核

2019-11-14 15:50:53 1795

1795

Zybo(Zynq? Board)是一款資源豐富且易用的嵌入式軟件及數(shù)字電路入門級(jí)開發(fā)平臺(tái),該平臺(tái)主芯片為Xilinx Zynq-7000系列中的最小型號(hào)Z-7010。

2019-11-25 11:42:27 1363

1363

Zynq-7000 ZING SOM開發(fā)模塊演示,ZingSoM模塊是針對(duì)OEM類型和小批量試生產(chǎn)型客戶量身定制的一款Zynq最小系統(tǒng)板,集成了Zynq All Programmable SoC系統(tǒng)所需的常用組件,包括DDR3和Flash,以及千兆以太網(wǎng)卡和USB接口。

2020-07-02 10:20:00 2517

2517 PS部分框圖如上圖所示,PS 和外部接口之間的通信主要是通過(guò)復(fù)用的輸入 / 輸出( Multiplexed Input/Output,MIO)實(shí)現(xiàn)的,它提供了可以做靈活配置的 54 個(gè)引腳,這表明外部設(shè)備和引腳之間的映射是可以按需定義的。

2020-08-27 14:30:35 4024

4024

為了簡(jiǎn)化使用GPIO,編寫了以下腳本。使用下列腳本,一條命令就能設(shè)置一個(gè)GPIO的輸出值。腳本接受兩個(gè)輸入?yún)?shù)。第一個(gè)參數(shù)表示GPIO編號(hào),MIO GPIO從0開始,EMIO GPIO從78開始。第二個(gè)參數(shù)是輸出值。如果輸出值是1,可以省略第二個(gè)參數(shù)。

2020-09-03 09:50:19 2520

2520

和接口的構(gòu)架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過(guò)

2020-11-02 11:27:51 3880

3880

zynq-7000 SoC產(chǎn)品選型指南

2020-12-09 16:15:01 12

12 ZYNQ7000系列FPGA的PS自帶兩個(gè)IIC接口,接口PIN IO可擴(kuò)展為EMIO形式即將IO約束到PL端符合電平標(biāo)準(zhǔn)的IO(BANK12、BANK13、BANK34、BANK35);SDK

2022-07-25 17:56:52 1404

1404

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 Zynq-7000 SoC數(shù)據(jù)手冊(cè)下載

2021-05-21 15:22:41 28

28 上,也可以通過(guò) EMIO 連接到 PL 端的引腳。Zynq-7000 系列芯片一般有 54 個(gè) MIO,個(gè)別芯片如 7z007s 只有 32 個(gè)。GPIO 是英文“general purpose I/O”的縮寫,即通用的輸入/輸出。是 ZYNQ PS 中的一個(gè)外設(shè),用于觀測(cè)和控制器件引腳的狀態(tài)。圖 1

2021-12-04 18:51:06 16

16 ZYNQ學(xué)習(xí)筆記_GPIOGPIO介紹MIO介紹EMIO介紹控制GPIO接口的寄存器原理GPIO介紹GPIO的英文全稱為General-purpose input/output,即一種通用外設(shè),可以

2021-12-04 19:36:10 10

10 CPUCPU為Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平臺(tái)升級(jí)能力強(qiáng),以下為Xilinx Zynq-7000特性參數(shù):電源接口和開關(guān)采用12V3A

2022-01-07 15:09:26 9

9 前面簡(jiǎn)單學(xué)習(xí)了關(guān)于GPIO的操作,本次將使用PL 端調(diào)用 AXI GPIO IP 核, 并通過(guò) AXI4-Lite 接口實(shí)現(xiàn) PS 與 PL 中 AXI GPIO 模塊的通信。

2022-07-19 17:36:52 3230

3230 本文介紹了Xilinx Zynq-7000系列XC7Z035/XC7Z045系列主要特性,資源框圖及PS端ETH RJ45接口引腳說(shuō)明

2022-11-21 09:17:10 3049

3049

Zynq-7000系列芯片的邏輯資源(PL)是不同的,Z-7020以下是基于A7 FPGA的,Z-7030以上是基于K7的,資源數(shù)量有所不同。而我們使用的Zedboard是Z-7020的。

2022-12-22 09:44:09 1493

1493 電子發(fā)燒友網(wǎng)站提供《用于千兆位收發(fā)器應(yīng)用的全數(shù)字VCXO替代品(7系列/Zynq-7000).pdf》資料免費(fèi)下載

2023-09-14 11:43:37 0

0 電子發(fā)燒友網(wǎng)站提供《Zynq-7000 SoC的安全啟動(dòng)應(yīng)用說(shuō)明.pdf》資料免費(fèi)下載

2023-09-13 11:46:04 1

1 電子發(fā)燒友網(wǎng)站提供《Zynq-7000 SoC:嵌入式設(shè)計(jì)教程.pdf》資料免費(fèi)下載

2023-09-13 09:20:03 3

3 Xilinx 從 Spartan-6 和 Virtex-6 器件開始采用高級(jí)可擴(kuò)展接口 (AXI) 協(xié)議作為知識(shí)產(chǎn)權(quán) (IP) 內(nèi)核。Xilinx 繼續(xù)將 AXI 協(xié)議用于針對(duì) 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論