為幫助同學(xué)們更好地理解和實(shí)現(xiàn)DDS的功能,在硬禾做畢業(yè)設(shè)計(jì)的小楊同學(xué)特制作了一套完整的DDS任意波形發(fā)生器系統(tǒng),它包含如下的功能:

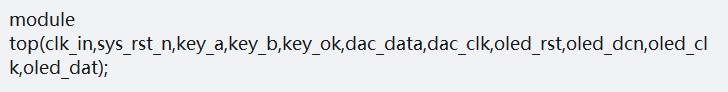

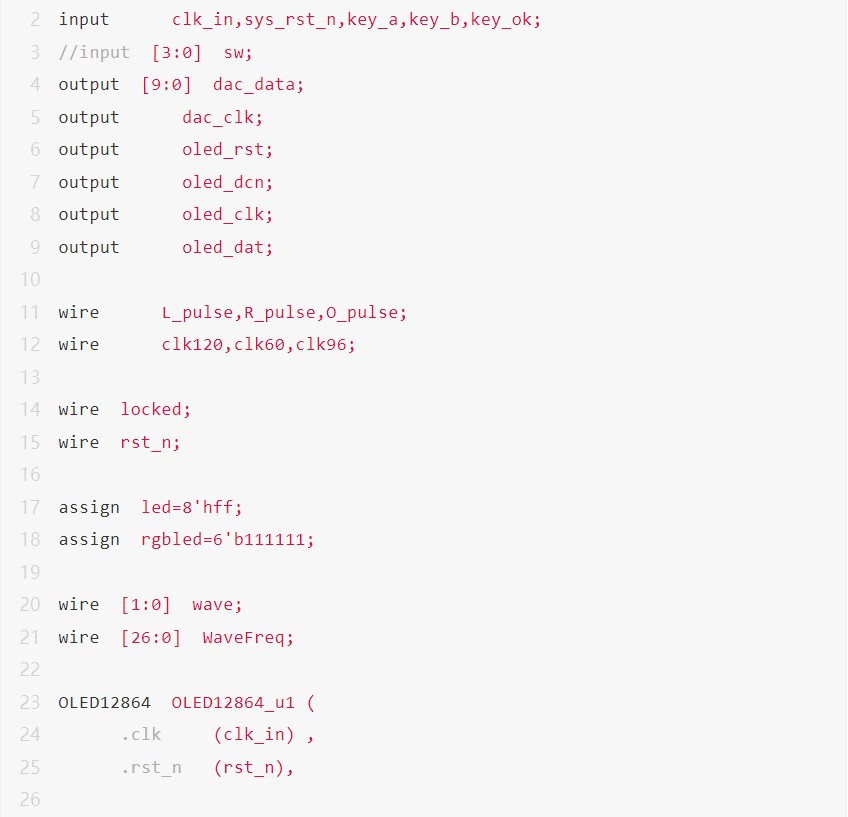

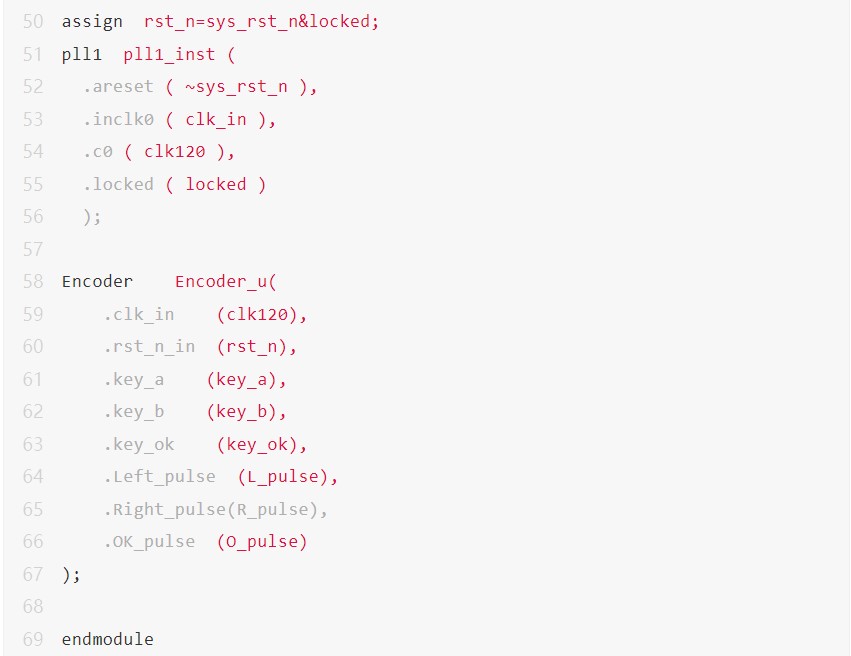

1. 頂層模塊

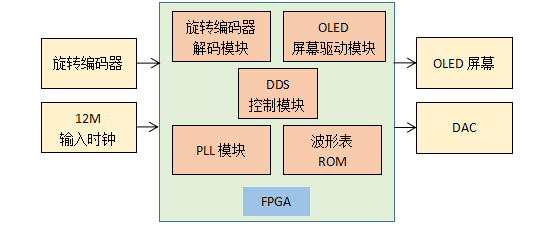

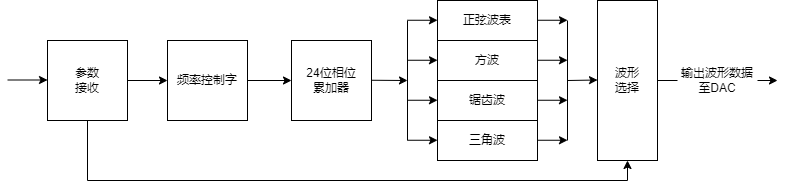

FPGA片內(nèi)邏輯的結(jié)構(gòu)框圖如上圖所示,F(xiàn)PGA片上實(shí)現(xiàn)的邏輯包括:

調(diào)用內(nèi)部鎖相環(huán)由輸入的12M時(shí)鐘得到120MHZ工作時(shí)鐘,驅(qū)動(dòng)DDS控制模塊,輸出作為DAC的轉(zhuǎn)換時(shí)鐘。

處理旋轉(zhuǎn)編碼器的輸入。判斷旋轉(zhuǎn)編碼器的轉(zhuǎn)動(dòng)和按下,順時(shí)針轉(zhuǎn)動(dòng)對(duì)應(yīng)信號(hào)頻率的增加,逆時(shí)針轉(zhuǎn)動(dòng)對(duì)應(yīng)信號(hào)頻率的減小,按下對(duì)應(yīng)波形的切換。

存儲(chǔ)正弦波的波形數(shù)據(jù)。

實(shí)現(xiàn)的波形包括正弦波、三角波、方波、鋸齒波四種波形,波形頻率范圍為100kHZ到10MHZ。

通過(guò)spi總線驅(qū)動(dòng)OLED屏幕指示當(dāng)前的波形和頻率。

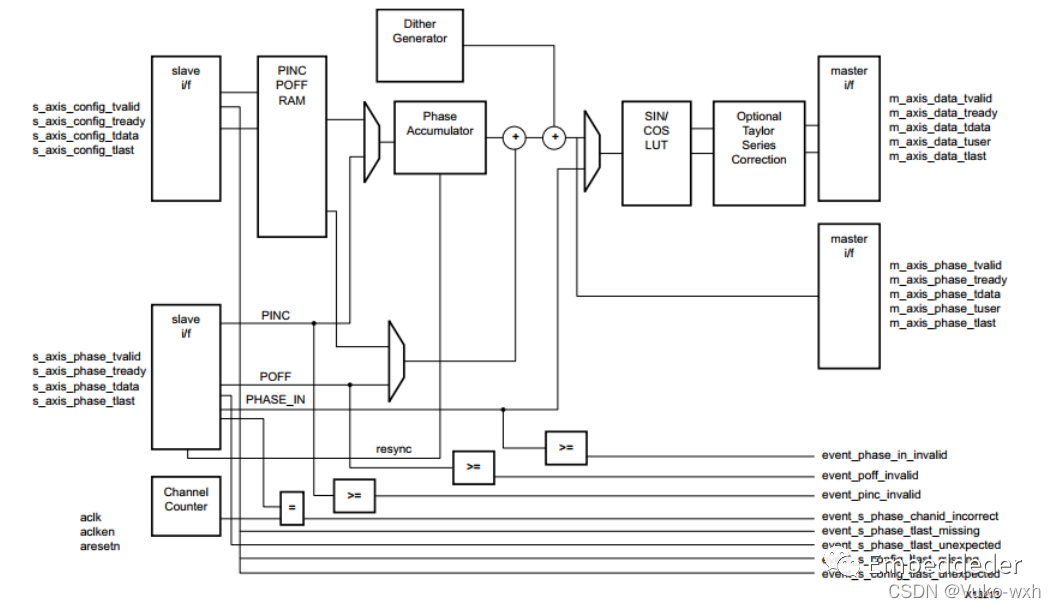

2. DDS核心模塊

DDS控制模塊是信號(hào)發(fā)生器設(shè)計(jì)的核心,利用Verilog實(shí)現(xiàn)DDS的結(jié)構(gòu)框圖如下圖所示。

?

從圖中可以看出,DDS控制模塊根據(jù)旋轉(zhuǎn)編碼器模塊的輸入信號(hào)調(diào)節(jié)頻率控制字、切換波形,輸出一定頻率的方波、三角波、鋸齒波或正弦波數(shù)據(jù)至DAC。同時(shí),DDS控制模塊還會(huì)將當(dāng)前波形信息和頻率信息輸出給OLED模塊用于顯示。四種波形的產(chǎn)生使用同一個(gè)相位累加寄存器,如下圖所示,相位累加寄存器本質(zhì)上是一個(gè)不斷累加的計(jì)數(shù)器,單次累加的幅度是頻率控制字,頻率控制字由旋轉(zhuǎn)編碼器調(diào)節(jié),當(dāng)旋轉(zhuǎn)編碼器順時(shí)針轉(zhuǎn)動(dòng)時(shí)增大頻率控制字,當(dāng)旋轉(zhuǎn)編碼器逆時(shí)針轉(zhuǎn)動(dòng)時(shí)減小頻率控制字。接下來(lái)分別介紹四種波形的原理。

方波 - 取相位累加寄存器的最高位作為判斷條件,當(dāng)最高位為邏輯1,則對(duì)DAC的輸入賦值10’h3ff;當(dāng)最高位為邏輯0,則則對(duì)DAC的輸入賦值10’h000,從而實(shí)現(xiàn)了方波波形。

鋸齒波 - 取相位累加寄存器的高十位直接作為DAC的輸入,隨著相位累加寄存器不斷累加,DAC的輸入也周期性地以鋸齒波形狀循環(huán)。

三角波 - 取相位累加寄存器的最高位作為判斷條件,當(dāng)最高位為邏輯1,則將相位累加寄存器的13到22位直接作為DAC數(shù)據(jù)的輸入;當(dāng)最高位為邏輯0,則將相位累加寄存器的13到22位取反后作為DAC數(shù)據(jù)的輸入。

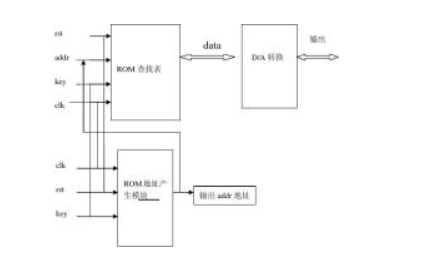

正弦波 - 與其它三種波形不同,正弦波不能直接用取相位累加寄存器作為DAC的輸入,需要將相位累加寄存器的高8位作為正弦波表的地址輸入,這樣的話,就實(shí)現(xiàn)了在一個(gè)周期內(nèi)以一定間隔讀出正弦波表內(nèi)的數(shù)據(jù)作為DAC的輸入。

下面是DDS的主代碼,可以選擇輸出的波形以及相應(yīng)的頻率

// --------------------------------------------------------------------

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// --------------------------------------------------------------------

// Module: dds

//

// Author: Step

//

// Description: dds

//

// Web

//

// --------------------------------------------------------------------

// Code Revision History :

// --------------------------------------------------------------------

// Version: |Mod. Date: |Changes Made:

// V1.0 |2021.11.27 |Initial ver

// --------------------------------------------------------------------

module dds(clk_in,rst_n,O_pulse,L_pulse,R_pulse,dac_data,wave,WaveFreq);//

localparam SIN = 2'b00, SAW = 2'b01, TRI = 2'b10, SQU = 2'b11;

input clk_in; // 小腳丫FPGA的外部時(shí)鐘頻率為12MHz

input rst_n;

input wire O_pulse,L_pulse,R_pulse;

output reg [9:0] dac_data; // 10位數(shù)據(jù)輸出送給外部的DAC

output reg [1:0] wave;

output reg [26:0] WaveFreq;

reg [23:0] phase_acc; //增加相位累加器位數(shù)使得分辨率提高

wire [23:0] phase;

reg [23:0] f_inc;

assign phase=phase_acc;

always @(posedge clk_in) phase_acc <= phase_acc + f_inc; //f_inc=24'd27962;主時(shí)鐘為12MHz,則產(chǎn)生20KHz的正弦波信號(hào)

wire [9:0] sin_dat; //正弦波

wire [9:0] saw_dat = phase[23:14]; //鋸齒波

wire [9:0] tri_dat = phase[23]? (~phase[22:13]) : phase[22:13]; //三角波

wire [9:0] squ_dat = phase[23]? 10'h3ff : 10'h000; //方波

always @(*) begin

case(wave)

2'b00: dac_data = sin_dat; //正弦波

2'b01: dac_data = saw_dat; //鋸齒波

2'b10: dac_data = tri_dat; //三角波

2'b11: dac_data = squ_dat; //方波

default: dac_data = sin_dat; //正弦波

endcase

end

lookup_tables u_lookup_tables(.phase(phase_acc[23:16]), .sin_out(sin_dat));

//波形輸出選擇

always @(posedge clk_in or negedge rst_n) begin

if(!rst_n) wave <= SIN;

else if(O_pulse)begin

case(wave)

SIN: wave <= SAW;

SAW: wave <= TRI;

TRI: wave <= SQU;

SQU: wave <= SIN;

default: wave <= SIN;

endcase

end else wave <= wave;

end

//頻率控制

always@(posedge clk_in or negedge rst_n) begin

if(!rst_n) begin

f_inc <= 24'h22222;

WaveFreq<=1_000_000;

end

else if(L_pulse==1'b1) begin

if(f_inc <= 24'h369d) f_inc <= f_inc;

else begin

f_inc <= f_inc - 24'h369d;

WaveFreq<=WaveFreq-100000;

end

end

else if(R_pulse==1'b1) begin

if(f_inc >= 24'h155554) f_inc <= f_inc;

else begin

f_inc <= f_inc + 24'h369d;

WaveFreq<=WaveFreq+100000;

end

end

else f_inc <= f_inc;

end

endmodule

//dds時(shí)鐘頻率給定后,輸出信號(hào)的頻率取決于頻率控制字,

// 頻率分辨率取決于累加器位數(shù),

// 相位分辨率取決于ROM的地址線位數(shù),

// 幅度量化噪聲取決于ROM的數(shù)據(jù)位字長(zhǎng)和D/A轉(zhuǎn)換器位數(shù)

查找表的程序,主要是利用了正弦波的對(duì)稱性,為了節(jié)省FPGA的資源,可以只構(gòu)建一個(gè)象限的波形,另外3個(gè)象限可以基于其對(duì)稱性通過(guò)邏輯來(lái)實(shí)現(xiàn)。

/* lookup_tables.v */

module lookup_tables(phase, sin_out);

input [7:0] phase;

output [9:0] sin_out;

wire [9:0] sin_out;

reg [5:0] address;

wire [1:0] sel;

wire [8:0] sine_table_out;

reg [9:0] sine_onecycle_amp;

//assign sin_out = {4'b0, sine_onecycle_amp[9:4]} + 9'hff; // 可以調(diào)節(jié)輸出信號(hào)的幅度

assign sin_out = sine_onecycle_amp[9:0];

assign sel = phase[7:6];

sin_table u_sin_table(address,sine_table_out);

always @(sel or sine_table_out)

begin

case(sel)

2'b00: begin

sine_onecycle_amp = 9'h1ff + sine_table_out[8:0];

address = phase[5:0];

end

2'b01: begin

sine_onecycle_amp = 9'h1ff + sine_table_out[8:0];

address = ~phase[5:0];

end

2'b10: begin

sine_onecycle_amp = 9'h1ff - sine_table_out[8:0];

address = phase[5:0];

end

2'b11: begin

sine_onecycle_amp = 9'h1ff - sine_table_out[8:0];

address = ~ phase[5:0];

end

endcase

end

endmodule

構(gòu)建正弦波表的程序,無(wú)論使用Lattice的Diamond以及Inel的Quartus編譯工具中都有相應(yīng)的IP可以直接調(diào)用使用。在這里我們通過(guò)Verilog代碼自行構(gòu)建一個(gè)正弦波表。

module sin_table(address,sin);

output [8:0] sin;

input [5:0] address;

reg [8:0] sin;

always @(address)

begin

case(address)

6'h0: sin=9'h0;

6'h1: sin=9'hC;

6'h2: sin=9'h19;

6'h3: sin=9'h25;

6'h4: sin=9'h32;

6'h5: sin=9'h3E;

6'h6: sin=9'h4B;

6'h7: sin=9'h57;

6'h8: sin=9'h63;

6'h9: sin=9'h70;

6'ha: sin=9'h7C;

6'hb: sin=9'h88;

6'hc: sin=9'h94;

6'hd: sin=9'hA0;

6'he: sin=9'hAC;

6'hf: sin=9'hB8;

6'h10: sin=9'hC3;

6'h11: sin=9'hCF;

6'h12: sin=9'hDA;

6'h13: sin=9'hE6;

6'h14: sin=9'hF1;

6'h15: sin=9'hFC;

6'h16: sin=9'h107;

6'h17: sin=9'h111;

6'h18: sin=9'h11C;

6'h19: sin=9'h126;

6'h1a: sin=9'h130;

6'h1b: sin=9'h13A;

6'h1c: sin=9'h144;

6'h1d: sin=9'h14E;

6'h1e: sin=9'h157;

6'h1f: sin=9'h161;

6'h20: sin=9'h16A;

6'h21: sin=9'h172;

6'h22: sin=9'h17B;

6'h23: sin=9'h183;

6'h24: sin=9'h18B;

6'h25: sin=9'h193;

6'h26: sin=9'h19B;

6'h27: sin=9'h1A2;

6'h28: sin=9'h1A9;

6'h29: sin=9'h1B0;

6'h2a: sin=9'h1B7;

6'h2b: sin=9'h1BD;

6'h2c: sin=9'h1C3;

6'h2d: sin=9'h1C9;

6'h2e: sin=9'h1CE;

6'h2f: sin=9'h1D4;

6'h30: sin=9'h1D9;

6'h31: sin=9'h1DD;

6'h32: sin=9'h1E2;

6'h33: sin=9'h1E6;

6'h34: sin=9'h1E9;

6'h35: sin=9'h1ED;

6'h36: sin=9'h1F0;

6'h37: sin=9'h1F3;

6'h38: sin=9'h1F6;

6'h39: sin=9'h1F8;

6'h3a: sin=9'h1FA;

6'h3b: sin=9'h1FC;

6'h3c: sin=9'h1FD;

6'h3d: sin=9'h1FE;

6'h3e: sin=9'h1FF;

6'h3f: sin=9'h1FF;

endcase

end

endmodule

3. 編碼器輸入模塊

// --------------------------------------------------------------------

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// --------------------------------------------------------------------

// Module: Encoder

//

// Author: Step

//

// Description: Driver for rotary encoder

//

// Web

//

// --------------------------------------------------------------------

// Code Revision History :

// --------------------------------------------------------------------

// Version: |Mod. Date: |Changes Made:

// V1.0 |2021.11.27 |Initial ver

// --------------------------------------------------------------------

module Encoder

(

input clk_in, //系統(tǒng)時(shí)鐘

input rst_n_in, //系統(tǒng)復(fù)位,低有效

input wire key_a,

input wire key_b,

input wire key_ok,

output reg Left_pulse, //左旋轉(zhuǎn)脈沖輸出

output reg Right_pulse, //右旋轉(zhuǎn)脈沖輸出

output OK_pulse //按動(dòng)脈沖輸出

);

localparam NUM_500US = 6_0000;

reg [15:0] cnt;

//計(jì)數(shù)器周期為500us,控制鍵值采樣頻率

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) cnt <= 0;

else if(cnt >= NUM_500US-1) cnt <= 1'b0;

else cnt <= cnt + 1'b1;

end

reg [5:0] cnt_20ms;

reg key_a_r,key_a_r1;

reg key_b_r,key_b_r1;

reg key_ok_r;

//針對(duì)A、B、D管腳分別做簡(jiǎn)單去抖操作,

//如果對(duì)旋轉(zhuǎn)編碼器的要求比較高,建議現(xiàn)對(duì)旋轉(zhuǎn)編碼器的輸出做嚴(yán)格的消抖處理后再來(lái)做旋轉(zhuǎn)編碼器的驅(qū)動(dòng)

//對(duì)旋轉(zhuǎn)編碼器的輸入緩存,消除亞穩(wěn)態(tài)同時(shí)延時(shí)鎖存

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) begin

key_a_r <= 1'b1;

key_a_r1 <= 1'b1;

key_b_r <= 1'b1;

key_b_r1 <= 1'b1;

cnt_20ms <= 1'b1;

key_ok_r <= 1'b1;

end else if(cnt == NUM_500US-1) begin

key_a_r <= key_a;

key_a_r1 <= key_a_r;

key_b_r <= key_b;

key_b_r1 <= key_b_r;

if(cnt_20ms >= 6'd40) begin //對(duì)于按鍵D信號(hào)還是采用20ms周期采樣的方法,40*500us = 20ms

cnt_20ms <= 6'd0;

key_ok_r <= key_ok;

end else begin

cnt_20ms <= cnt_20ms + 1'b1;

key_ok_r <= key_ok_r;

end

end

end

reg key_ok_r1;

//對(duì)按鍵D信號(hào)進(jìn)行延時(shí)鎖存

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) key_ok_r1 <= 1'b1;

else key_ok_r1 <= key_ok_r;

end

wire A_state = key_a_r1 && key_a_r && key_a; //旋轉(zhuǎn)編碼器A信號(hào)高電平狀態(tài)檢測(cè)

wire B_state = key_b_r1 && key_b_r && key_b; //旋轉(zhuǎn)編碼器B信號(hào)高電平狀態(tài)檢測(cè)

assign OK_pulse = key_ok_r1 && (!key_ok_r); //旋轉(zhuǎn)編碼器D信號(hào)下降沿檢測(cè)

reg A_state_reg;

//延時(shí)鎖存

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) A_state_reg <= 1'b1;

else A_state_reg <= A_state;

end

//旋轉(zhuǎn)編碼器A信號(hào)的上升沿和下降沿檢測(cè)

wire A_pos = (!A_state_reg) && A_state;

wire A_neg = A_state_reg && (!A_state);

//通過(guò)旋轉(zhuǎn)編碼器A信號(hào)的邊沿和B信號(hào)的電平狀態(tài)的組合判斷旋轉(zhuǎn)編碼器的操作,并輸出對(duì)應(yīng)的脈沖信號(hào)

always@(posedge clk_in or negedge rst_n_in)begin

if(!rst_n_in)begin

Right_pulse <= 1'b0;

Left_pulse <= 1'b0;

end else begin

if(A_pos && B_state) Left_pulse <= 1'b1;

else if(A_neg && B_state) Right_pulse <= 1'b1;

else begin

Right_pulse <= 1'b0;

Left_pulse <= 1'b0;

end

end

end

endmodule

4. 將頻率值轉(zhuǎn)換為OLED顯示器上的字符

module getChar3 (

input clk,

input rst_n,

input [31:0] WaveFreq,

output reg[(8*16-1):0] char

);

reg [31:0] t_bin;

reg [3:0] bcd8,bcd7,bcd6,bcd5,bcd4,bcd3,bcd2,bcd1;

reg [3:0] state;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

t_bin<=WaveFreq;

char<= 0;

bcd8<= 0;

bcd7<= 0;

bcd6<= 0;

bcd5<= 0;

bcd4<= 0;

bcd3<= 0;

bcd2<= 0;

bcd1<= 0;

state<=0;

end

else begin

case (state)

0: begin

t_bin<=WaveFreq;

state<=state+1;

end

1: begin

if($signed(t_bin)-$signed(10000000)>=0)begin

bcd8<=bcd8+1;

t_bin<=t_bin-10000000;

end

else begin

state<=state+1;

end

end

2: begin

if($signed(t_bin)-$signed(1000000)>=0)begin

bcd7<=bcd7+1;

t_bin<=t_bin-1000000;

end

else begin

state<=state+1;

end

end

3: begin

if($signed(t_bin)-$signed(100000)>=0)begin

bcd6<=bcd6+1;

t_bin<=t_bin-100000;

end

else begin

state<=state+1;

end

end

4: begin

if($signed(t_bin)-$signed(10000)>=0)begin

bcd5<=bcd5+1;

t_bin<=t_bin-10000;

end

else begin

state<=state+1;

end

end

5: begin

if($signed(t_bin)-$signed(1000)>=0)begin

bcd4<=bcd4+1;

t_bin<=t_bin-1000;

end

else begin

state<=state+1;

end

end

6: begin

if($signed(t_bin)-$signed(100)>=0)begin

bcd3<=bcd3+1;

t_bin<=t_bin-100;

end

else begin

state<=state+1;

end

end

7: begin

if($signed(t_bin)-$signed(10)>=0)begin

bcd2<=bcd2+1;

t_bin<=t_bin-10;

end

else begin

state<=state+1;

end

end

8: begin

if($signed(t_bin)-$signed(1)>=0)begin

bcd1<=bcd1+1;

t_bin<=t_bin-1;

end

else begin

state<=state+1;

end

end

9:begin

t_bin<=WaveFreq;

char<={" ",4'h0,bcd8,4'h0,bcd7,"_",

4'h0,bcd6,4'h0,bcd5,4'h0,bcd4,"_",

4'h0,bcd3,4'h0,bcd2,4'h0,bcd1,"Hz "};

bcd8<= 0;

bcd7<= 0;

bcd6<= 0;

bcd5<= 0;

bcd4<= 0;

bcd3<= 0;

bcd2<= 0;

bcd1<= 0;

state<=0;

end

default: begin

t_bin<=WaveFreq;

bcd7<= 0;

bcd6<= 0;

bcd5<= 0;

bcd4<= 0;

bcd3<= 0;

bcd2<= 0;

bcd1<= 0;

state<=0;

end

endcase

end

end

endmodule

5. OLED顯示模塊

這是通過(guò)SPI總線方式來(lái)驅(qū)動(dòng)128*64分辨率的OLED顯示屏顯示相應(yīng)信息的邏輯代碼

該模塊的輸入包括時(shí)鐘、復(fù)位、輸入變量,輸出是驅(qū)動(dòng)ssd1306的的五根總線:包括spi的三條總線、一條ssd1306復(fù)位線、一條ssd1306數(shù)據(jù)指令選擇線。該模塊通過(guò)SPI總線完成OLED屏幕的顯示,能夠顯示字符和漢字。該模塊中,利用查找表實(shí)現(xiàn)字符、漢字模的存儲(chǔ),利用一個(gè)一段式狀態(tài)機(jī)實(shí)現(xiàn):初始化配置SSD1306驅(qū)動(dòng)芯片、在屏幕上顯示指定的信息。其中,IDLE狀態(tài)作為初始狀態(tài)完成所有寄存器變量的初始化;MAIN狀態(tài)作為總調(diào)度實(shí)現(xiàn)了整個(gè)OLED模塊的流程調(diào)度,如果想要使用本模塊,只需要在本狀態(tài)進(jìn)行修改;INIT狀態(tài)通過(guò)調(diào)用WRITE狀態(tài)將23條SSD1306的配置指令通過(guò)SPI時(shí)序發(fā)出,完成SSD1306的配置;SCAN狀態(tài)通過(guò)調(diào)用WRITE狀態(tài)完成字符的顯示;CHINESE狀態(tài)通過(guò)調(diào)用WRITE狀態(tài)完成漢字的顯示;WRITE狀態(tài)作為底層狀態(tài),完成SPI的傳輸過(guò)程;DELAY狀態(tài)的功能是延時(shí)。本模塊的使用通過(guò)在MAIN狀態(tài)里進(jìn)行添加相應(yīng)的邏輯來(lái)實(shí)現(xiàn),如果顯示漢字則需要在漢字字模中添加相應(yīng)的字模信息。如果想要實(shí)時(shí)刷新信息,需要將動(dòng)態(tài)顯示的信息通過(guò)本module的輸入端口sw傳入模塊本在MAIN狀態(tài)里進(jìn)行調(diào)用,也可自行添加輸入端口變量。

// --------------------------------------------------------------------

// Module: OLED12864?

// Description: OLED12864_Driver

// --------------------------------------------------------------------

module OLED12864

(

? input? ? ? ? clk,? ? //12MHz緋葷粺鏃墮挓

? input? ? ? ? rst_n,? ? //緋葷粺澶嶄綅錛屼綆鏈夋晥

? input? ? [3:0]? sw,

? input? ? [1:0]? wave,

? input [26:0]? ? WaveFreq,

? output? reg? ? ? oled_csn,? //OLCD娑叉櫠灞忎嬌鑳

? output? reg? ? ? oled_rst,? //OLCD娑叉櫠灞忓浣

? output? reg? ? ? oled_dcn,? //OLCD鏁版嵁鎸囦護(hù)鎺у埗

? output? reg? ? ? oled_clk,? //OLCD鏃墮挓淇″彿

? output? reg? ? ? oled_dat? //OLCD鏁版嵁淇″彿

);

? localparam INIT_DEPTH = 16'd23; //LCD鍒濆鍖栫殑鍛戒護(hù)鐨勬暟閲

? localparam IDLE = 7'h1, MAIN = 7'h2, INIT = 7'h4, SCAN = 7'h8, WRITE = 7'h10, DELAY = 7'h20,CHINESE=7'h40;

? localparam HIGH? = 1'b1, LOW = 1'b0;

? localparam DATA? = 1'b1, CMD = 1'b0;

? reg? ?[7:0]? ? ? ?cmd [24:0];

? reg? ?[39:0]? ? ? ?mem [122:0];

? reg? ? [63:0]? ? ? mem_hanzi[79:0];

? reg? ? [4:0]? ? ? length_hanzi;

? reg? [7:0]? ? ? ? y_p, x_ph, x_pl;

? reg? [(8*21-1):0]? ?char;

? reg? [7:0]? ? ? ? num, char_reg;? ? ? ??

? reg? [4:0]? ? ? ? cnt_main, cnt_init, cnt_scan, cnt_write,cnt_chinese;

? reg? [15:0]? ? ? num_delay, cnt_delay, cnt;

? reg? [6:0]? ? ? ?state, state_back;

? reg [4:0]? ? ? hanzi_fuzhujishu;

? ? wire [(8*16-1):0]? ?char3;

? getChar3 getChar3 (

? ? ? ? .clk(clk),

? ? ? ? .rst_n(rst_n),

? ? ? ? .WaveFreq(WaveFreq),

? ? ? ? .char(char3)

? ? );

? always @ (posedge clk or negedge rst_n) begin

? ? if(!rst_n) begin

? ? ? cnt_main <= 1'b0; cnt_init <= 1'b0; cnt_scan <= 1'b0; cnt_write <= 1'b0;cnt_chinese <= 1'b0;

? ? ? y_p <= 1'b0; x_ph <= 1'b0; x_pl <= 1'b0;length_hanzi<=5'd0;hanzi_fuzhujishu<=5'd0;

? ? ? num <= 1'b0; char <= 1'b0; char_reg <= 1'b0;

? ? ? num_delay <= 16'd5; cnt_delay <= 1'b0; cnt <= 1'b0;

? ? ? oled_csn <= HIGH; oled_rst <= HIGH; oled_dcn <= CMD; oled_clk <= HIGH; oled_dat <= LOW;

? ? ? state <= IDLE; state_back <= IDLE;

? ? end else begin

? ? ? case(state)

? ? ? ? IDLE:begin

? ? ? ? ? ? cnt_main <= 1'b0; cnt_init <= 1'b0; cnt_scan <= 1'b0; cnt_write <= 1'b0;

? ? ? ? ? ? y_p <= 1'b0; x_ph <= 1'b0; x_pl <= 1'b0;

? ? ? ? ? ? num <= 1'b0; char <= 1'b0; char_reg <= 1'b0;

? ? ? ? ? ? num_delay <= 16'd5; cnt_delay <= 1'b0; cnt <= 1'b0;

? ? ? ? ? ? oled_csn <= HIGH; oled_rst <= HIGH; oled_dcn <= CMD; oled_clk <= HIGH; oled_dat <= LOW;

? ? ? ? ? ? state <= MAIN; state_back <= MAIN;

? ? ? ? ? end

? ? ? ? MAIN:begin

? ? ? ? ? ? if(cnt_main >= 5'd14) cnt_main <= 5'd12;

? ? ? ? ? ? else cnt_main <= cnt_main + 1'b1;

? ? ? ? ? ? case(cnt_main)? //MAIN鐘舵€? ? ? ? ? ??

? ? ? ? ? ? ? 5'd0 :? begin state <= INIT; end

? ? ? ? ? ? ? 5'd1 :? begin y_p <= 8'hb0; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd8; char <= "DDS? ? ?";state <= SCAN; end

? ? ? ? ? ? ? 5'd2 :? begin y_p <= 8'hb1; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd8; char <= "? ? ? ? ";state <= SCAN; end? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ??

? ? ? ? ? ? ? 5'd3 :? begin y_p <= 8'hb0; x_ph <= 8'h14; x_pl <= 8'h00; num <= 5'd8; char <= "? ? ? ? ?";state <= SCAN; end

? ? ? ? ? ? ? 5'd4 :? begin y_p <= 8'hb1; x_ph <= 8'h14; x_pl <= 8'h00; num <= 5'd8; char <= "? ? ? ? ?";state <= SCAN; end? ? ? ? ? ? ? ? ? ? ? ??

? ? ? ? ? ? ? 5'd5 :? begin y_p <= 8'hb2; x_ph <= 8'h14; x_pl <= 8'h00; num <= 5'd8; char <= "? ? ? ? ?";state <= SCAN; end

? ? ? ? ? ? ? 5'd6 :? begin y_p <= 8'hb3; x_ph <= 8'h14; x_pl <= 8'h00; num <= 5'd8; char <= "? ? ? ? ?";state <= SCAN; end

? ? ? ? ? ? ? 5'd7 :? begin y_p <= 8'hb4; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd16; char <= "? ? ? ? ? ? ? ? ";state <= SCAN; end

? ? ? ? ? ? ? 5'd8 :? begin y_p <= 8'hb5; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd16; char <= "? ? ? ? ? ? ? ? ";state <= SCAN; end

? ? ? ? ? ? ? 5'd9 :? begin y_p <= 8'hb6; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd16; char <= "? ? ? ? ? ? ? ? ";state <= SCAN; end

? ? ? ? ? ? ? 5'd10:? begin y_p <= 8'hb7; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd16; char <= "? ? ? ? ? ? ? ? ";state <= SCAN; end? ? ? ? ? ? ??

? ? ? ? ? ? ? 5'd11:? ;//begin y_p <= 8'hb1; x_ph <= 8'h15; x_pl <= 8'h00; num <= 5'd 1; char <= sw; state <= SCAN; end

? ? ? ? ? ? ? 5'd12:? begin y_p <= 8'hb2; x_ph <= 8'h10; x_pl <= 8'h00; length_hanzi <= 5'd9;?

? ? ? ? ? ? ? ? ? ? if? ? ?(wave==2'b00)begin hanzi_fuzhujishu<=5'd8;state <= CHINESE; end?

? ? ? ? ? ? ? ? ? ? else if(wave==2'b01)begin hanzi_fuzhujishu<=5'd2;state <= CHINESE; end?

? ? ? ? ? ? ? ? ? ? else if(wave==2'b10)begin hanzi_fuzhujishu<=5'd4;state <= CHINESE; end?

? ? ? ? ? ? ? ? ? ? else begin hanzi_fuzhujishu<=5'd6;state <= CHINESE; end //if(wave==2'b11)

? ? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? 5'd13 :? begin y_p <= 8'hb3; x_ph <= 8'h10; x_pl <= 8'h00; length_hanzi <= 5'd9;?

? ? ? ? ? ? ? ? ? ? if? ? ?(wave==2'b00)begin hanzi_fuzhujishu<=5'd9;state <= CHINESE; end?

? ? ? ? ? ? ? ? ? ? else if(wave==2'b01)begin hanzi_fuzhujishu<=5'd3;state <= CHINESE; end?

? ? ? ? ? ? ? ? ? ? else if(wave==2'b10)begin hanzi_fuzhujishu<=5'd5;state <= CHINESE; end?

? ? ? ? ? ? ? ? ? ? else begin hanzi_fuzhujishu<=5'd7;state <= CHINESE; end //if(wave==2'b11)

? ? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? 5'd14 :? begin y_p <= 8'hb5; x_ph <= 8'h10; x_pl <= 8'h00; num <= 5'd16; char <= char3;state <= SCAN; end

? ? ? ? ? ? ? default: state <= IDLE;

? ? ? ? ? ? endcase

? ? ? ? ? end

? ? ? ? INIT:begin? //鍒濆鍖栫姸鎬

? ? ? ? ? ? case(cnt_init)

? ? ? ? ? ? ? 5'd0:? begin oled_rst <= LOW; cnt_init <= cnt_init + 1'b1; end? //澶嶄綅鏈夋晥

? ? ? ? ? ? ? 5'd1:? begin num_delay <= 16'd25000; state <= DELAY; state_back <= INIT; cnt_init <= cnt_init + 1'b1; end? //寤舵椂澶т簬3us

? ? ? ? ? ? ? 5'd2:? begin oled_rst <= HIGH; cnt_init <= cnt_init + 1'b1; end? //澶嶄綅鎭㈠

? ? ? ? ? ? ? 5'd3:? begin num_delay <= 16'd25000; state <= DELAY; state_back <= INIT; cnt_init <= cnt_init + 1'b1; end? //寤舵椂澶т簬220us

? ? ? ? ? ? ? 5'd4:? begin?

? ? ? ? ? ? ? ? ? ? if(cnt>=INIT_DEPTH) begin? //褰5鏉℃寚浠ゅ強(qiáng)鏁版嵁鍙戝嚭鍚庯紝閰嶇疆瀹屾垚

? ? ? ? ? ? ? ? ? ? ? cnt <= 1'b0;

? ? ? ? ? ? ? ? ? ? ? cnt_init <= cnt_init + 1'b1;

? ? ? ? ? ? ? ? ? ? end else begin??

? ? ? ? ? ? ? ? ? ? ? cnt <= cnt + 1'b1; num_delay <= 16'd5;

? ? ? ? ? ? ? ? ? ? ? oled_dcn <= CMD; char_reg <= cmd[cnt]; state <= WRITE; state_back <= INIT;

? ? ? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? 5'd5:? begin cnt_init <= 1'b0; state <= MAIN; end? //鍒濆鍖栧畬鎴愶紝榪斿洖MAIN鐘舵€

? ? ? ? ? ? ? default: state <= IDLE;

? ? ? ? ? ? endcase

? ? ? ? ? end

? ? ? ? SCAN:begin? //鍒峰睆鐘舵€侊紝浠嶳AM涓鍙栨暟鎹埛灞

? ? ? ? ? ? if(cnt_scan == 5'd11) begin

? ? ? ? ? ? ? if(num) cnt_scan <= 5'd3;

? ? ? ? ? ? ? else cnt_scan <= cnt_scan + 1'b1;

? ? ? ? ? ? end?

? ? ? ? ? ? else if(cnt_scan == 5'd12) cnt_scan <= 1'b0;

? ? ? ? ? ? else cnt_scan <= cnt_scan + 1'b1;

? ? ? ? ? ? case(cnt_scan)

? ? ? ? ? ? ? 5'd 0:? begin oled_dcn <= CMD; char_reg <= y_p; state <= WRITE; state_back <= SCAN; end? ? //瀹氫綅鍒楅〉鍦板潃

? ? ? ? ? ? ? 5'd 1:? begin oled_dcn <= CMD; char_reg <= x_pl; state <= WRITE; state_back <= SCAN; end? //瀹氫綅琛屽湴鍧€浣庝綅

? ? ? ? ? ? ? 5'd 2:? begin oled_dcn <= CMD; char_reg <= x_ph; state <= WRITE; state_back <= SCAN; end? //瀹氫綅琛屽湴鍧€楂樹(shù)綅

? ? ? ? ? ? ? 5'd 3:? begin num <= num - 1'b1;end

? ? ? ? ? ? ? 5'd 4:? begin oled_dcn <= DATA; char_reg <= 8'h00; state <= WRITE; state_back <= SCAN; end? //灝*8鐐歸樀緙栫▼8*8

? ? ? ? ? ? ? 5'd 5:? begin oled_dcn <= DATA; char_reg <= 8'h00; state <= WRITE; state_back <= SCAN; end? //灝*8鐐歸樀緙栫▼8*8

? ? ? ? ? ? ? 5'd 6:? begin oled_dcn <= DATA; char_reg <= 8'h00; state <= WRITE; state_back <= SCAN; end? //灝*8鐐歸樀緙栫▼8*8

? ? ? ? ? ? ? 5'd 7:? begin oled_dcn <= DATA; char_reg <= mem[char[(num*8)+:8]][39:32]; state <= WRITE; state_back <= SCAN; end

? ? ? ? ? ? ? 5'd 8:? begin oled_dcn <= DATA; char_reg <= mem[char[(num*8)+:8]][31:24]; state <= WRITE; state_back <= SCAN; end

? ? ? ? ? ? ? 5'd 9:? begin oled_dcn <= DATA; char_reg <= mem[char[(num*8)+:8]][23:16]; state <= WRITE; state_back <= SCAN; end

? ? ? ? ? ? ? 5'd10:? begin oled_dcn <= DATA; char_reg <= mem[char[(num*8)+:8]][15: 8]; state <= WRITE; state_back <= SCAN; end

? ? ? ? ? ? ? 5'd11:? begin oled_dcn <= DATA; char_reg <= mem[char[(num*8)+:8]][ 7: 0]; state <= WRITE; state_back <= SCAN; end

? ? ? ? ? ? ? 5'd12:? begin state <= MAIN; end

? ? ? ? ? ? ? default: state <= IDLE;

? ? ? ? ? ? endcase

? ? ? ? ? end

? ? ? ? //length_hanzi<=5'd8-----涓€琛屽啓鍏

? ? ? ? CHINESE:begin? //鏄劇ず姹夊瓧

? ? ? ? ? ? if(cnt_chinese == 5'd11) begin

? ? ? ? ? ? ? if(length_hanzi>=5'd2) cnt_chinese <= 5'd3;

? ? ? ? ? ? ? else cnt_chinese <= cnt_chinese + 1'b1;

? ? ? ? ? ? end?

? ? ? ? ? ? else if(cnt_chinese == 5'd12) cnt_chinese <= 1'b0;

? ? ? ? ? ? else cnt_chinese <= cnt_chinese+1'b1;

? ? ? ? ? ? case(cnt_chinese)? ??

? ? ? ? ? ? ? 5'd 0:? begin oled_dcn <= CMD; char_reg <= y_p; state <= WRITE; state_back <= CHINESE; end? ? //瀹氫綅鍒楅〉鍦板潃

? ? ? ? ? ? ? 5'd 1:? begin oled_dcn <= CMD; char_reg <= 8'h00; state <= WRITE; state_back <= CHINESE; end? //瀹氫綅琛屽湴鍧€浣庝綅

? ? ? ? ? ? ? 5'd 2:? begin oled_dcn <= CMD; char_reg <= 8'h10; state <= WRITE; state_back <= CHINESE; end? //瀹氫綅琛屽湴鍧€楂樹(shù)綅

? ? ? ? ? ? ? 5'd 3:? begin length_hanzi <= length_hanzi - 1'b1;end//length_hanzi鍒濆=9錛氭瘡琛岄暱搴︿負(fù)8

? ? ? ? ? ? ? 5'd 4:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][63:56]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd 5:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][55:48]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd 6:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][47:40]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd 7:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][39:32]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd 8:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][31:24]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd 9:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][23:16]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd10:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][15: 8]; state <= WRITE; state_back <= CHINESE; end

? ? ? ? ? ? ? 5'd11:? begin oled_dcn <= DATA; char_reg <= mem_hanzi[hanzi_fuzhujishu*8+8-length_hanzi][ 7: 0]; state <= WRITE; state_back <= CHINESE; end?

? ? ? ? ? ? ? 5'd12:? begin state <= MAIN; end

? ? ? ? ? ? ? default: state <= IDLE;

? ? ? ? ? ? endcase

? ? ? ? ? end

? ? ? ? WRITE:begin? //WRITE鐘舵€侊紝灝嗘暟鎹寜鐓PI鏃跺簭鍙戦€佺粰灞忓箷

? ? ? ? ? ? if(cnt_write >= 5'd17) cnt_write <= 1'b0;

? ? ? ? ? ? else cnt_write <= cnt_write + 1'b1;

? ? ? ? ? ? case(cnt_write)

? ? ? ? ? ? ? 5'd 0:? begin oled_csn <= LOW; end? //9浣嶆暟鎹渶楂樹(shù)綅涓哄懡浠ゆ暟鎹帶鍒朵綅

? ? ? ? ? ? ? 5'd 1:? begin oled_clk <= LOW; oled_dat <= char_reg[7]; end? //鍏堝彂楂樹(shù)綅鏁版嵁

? ? ? ? ? ? ? 5'd 2:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd 3:? begin oled_clk <= LOW; oled_dat <= char_reg[6]; end

? ? ? ? ? ? ? 5'd 4:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd 5:? begin oled_clk <= LOW; oled_dat <= char_reg[5]; end

? ? ? ? ? ? ? 5'd 6:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd 7:? begin oled_clk <= LOW; oled_dat <= char_reg[4]; end

? ? ? ? ? ? ? 5'd 8:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd 9:? begin oled_clk <= LOW; oled_dat <= char_reg[3]; end

? ? ? ? ? ? ? 5'd10:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd11:? begin oled_clk <= LOW; oled_dat <= char_reg[2]; end

? ? ? ? ? ? ? 5'd12:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd13:? begin oled_clk <= LOW; oled_dat <= char_reg[1]; end

? ? ? ? ? ? ? 5'd14:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd15:? begin oled_clk <= LOW; oled_dat <= char_reg[0]; end? //鍚庡彂浣庝綅鏁版嵁

? ? ? ? ? ? ? 5'd16:? begin oled_clk <= HIGH; end

? ? ? ? ? ? ? 5'd17:? begin oled_csn <= HIGH; state <= DELAY; end? //

? ? ? ? ? ? ? default: state <= IDLE;

? ? ? ? ? ? endcase

? ? ? ? ? end

? ? ? ? DELAY:begin? //寤舵椂鐘舵€

? ? ? ? ? ? if(cnt_delay >= num_delay) begin

? ? ? ? ? ? ? cnt_delay <= 16'd0; state <= state_back;?

? ? ? ? ? ? end else cnt_delay <= cnt_delay + 1'b1;

? ? ? ? ? end

? ? ? ? default:state <= IDLE;

? ? ? endcase

? ? end

? end

? //OLED閰嶇疆鎸囦護(hù)鏁版嵁

? always@(posedge rst_n)

? ? begin

? ? ? cmd[0 ] = {8'hae};?

? ? ? cmd[1 ] = {8'hd5};?

? ? ? cmd[2 ] = {8'h80};?

? ? ? cmd[3 ] = {8'ha8};?

? ? ? cmd[4 ] = {8'h3f};?

? ? ? cmd[5 ] = {8'hd3};?

? ? ? cmd[6 ] = {8'h00};?

? ? ? cmd[7 ] = {8'h40};?

? ? ? cmd[8 ] = {8'h8d};?

? ? ? cmd[9 ] = {8'h14};?

? ? ? cmd[10] = {8'h20};?

? ? ? cmd[11] = {8'h02};

? ? ? cmd[12] = {8'hc8};

? ? ? cmd[13] = {8'ha1};

? ? ? cmd[14] = {8'hda};

? ? ? cmd[15] = {8'h12};

? ? ? cmd[16] = {8'h81};

? ? ? cmd[17] = {8'hcf};

? ? ? cmd[18] = {8'hd9};

? ? ? cmd[19] = {8'hf1};

? ? ? cmd[20] = {8'hdb};

? ? ? cmd[21] = {8'h40};

? ? ? cmd[22] = {8'haf};

? ? end?

? //5*8鐐歸樀瀛楀簱鏁版嵁

? always@(posedge rst_n)

? ? begin

? ? ? mem[? 0] = {8'h3E, 8'h51, 8'h49, 8'h45, 8'h3E};? ?// 48? 0

? ? ? mem[? 1] = {8'h00, 8'h42, 8'h7F, 8'h40, 8'h00};? ?// 49? 1

? ? ? mem[? 2] = {8'h42, 8'h61, 8'h51, 8'h49, 8'h46};? ?// 50? 2

? ? ? mem[? 3] = {8'h21, 8'h41, 8'h45, 8'h4B, 8'h31};? ?// 51? 3

? ? ? mem[? 4] = {8'h18, 8'h14, 8'h12, 8'h7F, 8'h10};? ?// 52? 4

? ? ? mem[? 5] = {8'h27, 8'h45, 8'h45, 8'h45, 8'h39};? ?// 53? 5

? ? ? mem[? 6] = {8'h3C, 8'h4A, 8'h49, 8'h49, 8'h30};? ?// 54? 6

? ? ? mem[? 7] = {8'h01, 8'h71, 8'h09, 8'h05, 8'h03};? ?// 55? 7

? ? ? mem[? 8] = {8'h36, 8'h49, 8'h49, 8'h49, 8'h36};? ?// 56? 8

? ? ? mem[? 9] = {8'h06, 8'h49, 8'h49, 8'h29, 8'h1E};? ?// 57? 9

? ? ? mem[ 10] = {8'h7C, 8'h12, 8'h11, 8'h12, 8'h7C};? ?// 65? A

? ? ? mem[ 11] = {8'h7F, 8'h49, 8'h49, 8'h49, 8'h36};? ?// 66? B

? ? ? mem[ 12] = {8'h3E, 8'h41, 8'h41, 8'h41, 8'h22};? ?// 67? C

? ? ? mem[ 13] = {8'h7F, 8'h41, 8'h41, 8'h22, 8'h1C};? ?// 68? D

? ? ? mem[ 14] = {8'h7F, 8'h49, 8'h49, 8'h49, 8'h41};? ?// 69? E

? ? ? mem[ 15] = {8'h7F, 8'h09, 8'h09, 8'h09, 8'h01};? ?// 70? F

? ? ? mem[ 32] = {8'h00, 8'h00, 8'h00, 8'h00, 8'h00};? ?// 32? sp?

? ? ? mem[ 33] = {8'h00, 8'h00, 8'h2f, 8'h00, 8'h00};? ?// 33? !??

? ? ? mem[ 34] = {8'h00, 8'h07, 8'h00, 8'h07, 8'h00};? ?// 34??

? ? ? mem[ 35] = {8'h14, 8'h7f, 8'h14, 8'h7f, 8'h14};? ?// 35? #

? ? ? mem[ 36] = {8'h24, 8'h2a, 8'h7f, 8'h2a, 8'h12};? ?// 36? $

? ? ? mem[ 37] = {8'h62, 8'h64, 8'h08, 8'h13, 8'h23};? ?// 37? %

? ? ? mem[ 38] = {8'h36, 8'h49, 8'h55, 8'h22, 8'h50};? ?// 38? &

? ? ? mem[ 39] = {8'h00, 8'h05, 8'h03, 8'h00, 8'h00};? ?// 39? '

? ? ? mem[ 40] = {8'h00, 8'h1c, 8'h22, 8'h41, 8'h00};? ?// 40? (

? ? ? mem[ 41] = {8'h00, 8'h41, 8'h22, 8'h1c, 8'h00};? ?// 41? )

? ? ? mem[ 42] = {8'h14, 8'h08, 8'h3E, 8'h08, 8'h14};? ?// 42? *

? ? ? mem[ 43] = {8'h08, 8'h08, 8'h3E, 8'h08, 8'h08};? ?// 43? +

? ? ? mem[ 44] = {8'h00, 8'h00, 8'hA0, 8'h60, 8'h00};? ?// 44? ,

? ? ? mem[ 45] = {8'h08, 8'h08, 8'h08, 8'h08, 8'h08};? ?// 45? -

? ? ? mem[ 46] = {8'h00, 8'h60, 8'h60, 8'h00, 8'h00};? ?// 46? .

? ? ? mem[ 47] = {8'h20, 8'h10, 8'h08, 8'h04, 8'h02};? ?// 47? /

? ? ? mem[ 48] = {8'h3E, 8'h51, 8'h49, 8'h45, 8'h3E};? ?// 48? 0

? ? ? mem[ 49] = {8'h00, 8'h42, 8'h7F, 8'h40, 8'h00};? ?// 49? 1

? ? ? mem[ 50] = {8'h42, 8'h61, 8'h51, 8'h49, 8'h46};? ?// 50? 2

? ? ? mem[ 51] = {8'h21, 8'h41, 8'h45, 8'h4B, 8'h31};? ?// 51? 3

? ? ? mem[ 52] = {8'h18, 8'h14, 8'h12, 8'h7F, 8'h10};? ?// 52? 4

? ? ? mem[ 53] = {8'h27, 8'h45, 8'h45, 8'h45, 8'h39};? ?// 53? 5

? ? ? mem[ 54] = {8'h3C, 8'h4A, 8'h49, 8'h49, 8'h30};? ?// 54? 6

? ? ? mem[ 55] = {8'h01, 8'h71, 8'h09, 8'h05, 8'h03};? ?// 55? 7

? ? ? mem[ 56] = {8'h36, 8'h49, 8'h49, 8'h49, 8'h36};? ?// 56? 8

? ? ? mem[ 57] = {8'h06, 8'h49, 8'h49, 8'h29, 8'h1E};? ?// 57? 9

? ? ? mem[ 58] = {8'h00, 8'h36, 8'h36, 8'h00, 8'h00};? ?// 58? :

? ? ? mem[ 59] = {8'h00, 8'h56, 8'h36, 8'h00, 8'h00};? ?// 59? ;

? ? ? mem[ 60] = {8'h08, 8'h14, 8'h22, 8'h41, 8'h00};? ?// 60? <

? ? ? mem[ 61] = {8'h14, 8'h14, 8'h14, 8'h14, 8'h14};? ?// 61? =

? ? ? mem[ 62] = {8'h00, 8'h41, 8'h22, 8'h14, 8'h08};? ?// 62? >

? ? ? mem[ 63] = {8'h02, 8'h01, 8'h51, 8'h09, 8'h06};? ?// 63? ?

? ? ? mem[ 64] = {8'h32, 8'h49, 8'h59, 8'h51, 8'h3E};? ?// 64? @

? ? ? mem[ 65] = {8'h7C, 8'h12, 8'h11, 8'h12, 8'h7C};? ?// 65? A

? ? ? mem[ 66] = {8'h7F, 8'h49, 8'h49, 8'h49, 8'h36};? ?// 66? B

? ? ? mem[ 67] = {8'h3E, 8'h41, 8'h41, 8'h41, 8'h22};? ?// 67? C

? ? ? mem[ 68] = {8'h7F, 8'h41, 8'h41, 8'h22, 8'h1C};? ?// 68? D

? ? ? mem[ 69] = {8'h7F, 8'h49, 8'h49, 8'h49, 8'h41};? ?// 69? E

? ? ? mem[ 70] = {8'h7F, 8'h09, 8'h09, 8'h09, 8'h01};? ?// 70? F

? ? ? mem[ 71] = {8'h3E, 8'h41, 8'h49, 8'h49, 8'h7A};? ?// 71? G

? ? ? mem[ 72] = {8'h7F, 8'h08, 8'h08, 8'h08, 8'h7F};? ?// 72? H

? ? ? mem[ 73] = {8'h00, 8'h41, 8'h7F, 8'h41, 8'h00};? ?// 73? I

? ? ? mem[ 74] = {8'h20, 8'h40, 8'h41, 8'h3F, 8'h01};? ?// 74? J

? ? ? mem[ 75] = {8'h7F, 8'h08, 8'h14, 8'h22, 8'h41};? ?// 75? K

? ? ? mem[ 76] = {8'h7F, 8'h40, 8'h40, 8'h40, 8'h40};? ?// 76? L

? ? ? mem[ 77] = {8'h7F, 8'h02, 8'h0C, 8'h02, 8'h7F};? ?// 77? M

? ? ? mem[ 78] = {8'h7F, 8'h04, 8'h08, 8'h10, 8'h7F};? ?// 78? N

? ? ? mem[ 79] = {8'h3E, 8'h41, 8'h41, 8'h41, 8'h3E};? ?// 79? O

? ? ? mem[ 80] = {8'h7F, 8'h09, 8'h09, 8'h09, 8'h06};? ?// 80? P

? ? ? mem[ 81] = {8'h3E, 8'h41, 8'h51, 8'h21, 8'h5E};? ?// 81? Q

? ? ? mem[ 82] = {8'h7F, 8'h09, 8'h19, 8'h29, 8'h46};? ?// 82? R

? ? ? mem[ 83] = {8'h46, 8'h49, 8'h49, 8'h49, 8'h31};? ?// 83? S

? ? ? mem[ 84] = {8'h01, 8'h01, 8'h7F, 8'h01, 8'h01};? ?// 84? T

? ? ? mem[ 85] = {8'h3F, 8'h40, 8'h40, 8'h40, 8'h3F};? ?// 85? U

? ? ? mem[ 86] = {8'h1F, 8'h20, 8'h40, 8'h20, 8'h1F};? ?// 86? V

? ? ? mem[ 87] = {8'h3F, 8'h40, 8'h38, 8'h40, 8'h3F};? ?// 87? W

? ? ? mem[ 88] = {8'h63, 8'h14, 8'h08, 8'h14, 8'h63};? ?// 88? X

? ? ? mem[ 89] = {8'h07, 8'h08, 8'h70, 8'h08, 8'h07};? ?// 89? Y

? ? ? mem[ 90] = {8'h61, 8'h51, 8'h49, 8'h45, 8'h43};? ?// 90? Z

? ? ? mem[ 91] = {8'h00, 8'h7F, 8'h41, 8'h41, 8'h00};? ?// 91? [

? ? ? mem[ 92] = {8'h55, 8'h2A, 8'h55, 8'h2A, 8'h55};? ?// 92? .

? ? ? mem[ 93] = {8'h00, 8'h41, 8'h41, 8'h7F, 8'h00};? ?// 93? ]

? ? ? mem[ 94] = {8'h04, 8'h02, 8'h01, 8'h02, 8'h04};? ?// 94? ^

? ? ? mem[ 95] = {8'h40, 8'h40, 8'h40, 8'h40, 8'h40};? ?// 95? _

? ? ? mem[ 96] = {8'h00, 8'h01, 8'h02, 8'h04, 8'h00};? ?// 96? '

? ? ? mem[ 97] = {8'h20, 8'h54, 8'h54, 8'h54, 8'h78};? ?// 97? a

? ? ? mem[ 98] = {8'h7F, 8'h48, 8'h44, 8'h44, 8'h38};? ?// 98? b

? ? ? mem[ 99] = {8'h38, 8'h44, 8'h44, 8'h44, 8'h20};? ?// 99? c

? ? ? mem[100] = {8'h38, 8'h44, 8'h44, 8'h48, 8'h7F};? ?// 100 d

? ? ? mem[101] = {8'h38, 8'h54, 8'h54, 8'h54, 8'h18};? ?// 101 e

? ? ? mem[102] = {8'h08, 8'h7E, 8'h09, 8'h01, 8'h02};? ?// 102 f

? ? ? mem[103] = {8'h18, 8'hA4, 8'hA4, 8'hA4, 8'h7C};? ?// 103 g

? ? ? mem[104] = {8'h7F, 8'h08, 8'h04, 8'h04, 8'h78};? ?// 104 h

? ? ? mem[105] = {8'h00, 8'h44, 8'h7D, 8'h40, 8'h00};? ?// 105 i

? ? ? mem[106] = {8'h40, 8'h80, 8'h84, 8'h7D, 8'h00};? ?// 106 j

? ? ? mem[107] = {8'h7F, 8'h10, 8'h28, 8'h44, 8'h00};? ?// 107 k

? ? ? mem[108] = {8'h00, 8'h41, 8'h7F, 8'h40, 8'h00};? ?// 108 l

? ? ? mem[109] = {8'h7C, 8'h04, 8'h18, 8'h04, 8'h78};? ?// 109 m

? ? ? mem[110] = {8'h7C, 8'h08, 8'h04, 8'h04, 8'h78};? ?// 110 n

? ? ? mem[111] = {8'h38, 8'h44, 8'h44, 8'h44, 8'h38};? ?// 111 o

? ? ? mem[112] = {8'hFC, 8'h24, 8'h24, 8'h24, 8'h18};? ?// 112 p

? ? ? mem[113] = {8'h18, 8'h24, 8'h24, 8'h18, 8'hFC};? ?// 113 q

? ? ? mem[114] = {8'h7C, 8'h08, 8'h04, 8'h04, 8'h08};? ?// 114 r

? ? ? mem[115] = {8'h48, 8'h54, 8'h54, 8'h54, 8'h20};? ?// 115 s

? ? ? mem[116] = {8'h04, 8'h3F, 8'h44, 8'h40, 8'h20};? ?// 116 t

? ? ? mem[117] = {8'h3C, 8'h40, 8'h40, 8'h20, 8'h7C};? ?// 117 u

? ? ? mem[118] = {8'h1C, 8'h20, 8'h40, 8'h20, 8'h1C};? ?// 118 v

? ? ? mem[119] = {8'h3C, 8'h40, 8'h30, 8'h40, 8'h3C};? ?// 119 w

? ? ? mem[120] = {8'h44, 8'h28, 8'h10, 8'h28, 8'h44};? ?// 120 x

? ? ? mem[121] = {8'h1C, 8'hA0, 8'hA0, 8'hA0, 8'h7C};? ?// 121 y

? ? ? mem[122] = {8'h44, 8'h64, 8'h54, 8'h4C, 8'h44};? ?// 122 z

? ? end

? ? //姹夊瓧錛氱‖紱懼鍫

? always@(posedge rst_n)

? ? begin

? ? ? mem_hanzi[? 0] = {8'h04,8'h84,8'hE4,8'h5C,8'h44,8'hC4,8'h00,8'hF2};? ?// 48? 0

? ? ? mem_hanzi[? 1] = {8'h92,8'h92,8'hFE,8'h92,8'h92,8'hF2,8'h02,8'h00};? ?// 49? 1

? ? ? mem_hanzi[? 8] = {8'h02,8'h01,8'h7F,8'h10,8'h10,8'h3F,8'h80,8'h8F};? ?// 50? 2

? ? ? mem_hanzi[? 9] = {8'h54,8'h24,8'h5F,8'h44,8'h84,8'h87,8'h80,8'h00};? ?// 51? 3

? ? ? mem_hanzi[? 2] = {8'h00,8'h40,8'h44,8'h44,8'h44,8'h44,8'hC4,8'hFC};? ?// 52? 4

? ? ? mem_hanzi[? 3] = {8'hC2,8'h42,8'h42,8'h43,8'h42,8'h40,8'h00,8'h00};? ?// 53? 5

? ? ? mem_hanzi[? 10] = {8'h20,8'h20,8'h10,8'h08,8'h04,8'h03,8'h00,8'hFF};? ?// 54? 6

? ? ? mem_hanzi[? 11] = {8'h00,8'h03,8'h04,8'h08,8'h10,8'h20,8'h20,8'h00};? ?// 55? 7

? ? ? mem_hanzi[? 4] = {8'h40,8'h30,8'h11,8'h96,8'h90,8'h90,8'h91,8'h96};? ?// 56? 8

? ? ? mem_hanzi[? 5 ] = {8'h90,8'h90,8'h98,8'h14,8'h13,8'h50,8'h30,8'h00};? ?// 48? 0

? ? ? mem_hanzi[? 12] = {8'h04,8'h04,8'h04,8'h04,8'h04,8'h44,8'h84,8'h7E};? ?// 49? 1

? ? ? mem_hanzi[? 13] = {8'h06,8'h05,8'h04,8'h04,8'h04,8'h04,8'h04,8'h00};? ?// 50? 2

? ? ? mem_hanzi[? 6] = {8'h20,8'h18,8'h08,8'hEA,8'h2C,8'h28,8'h28,8'h2F};? ?// 51? 3

? ? ? mem_hanzi[? 7] = {8'h28,8'h28,8'h2C,8'hEA,8'h08,8'h28,8'h18,8'h00};? ?// 52? 4

? ? ? mem_hanzi[? 14] = {8'h40,8'h40,8'h48,8'h49,8'h49,8'h49,8'h49,8'h7F};? ?// 53? 5

? ? ? mem_hanzi[? 15] = {8'h49,8'h49,8'h49,8'h49,8'h48,8'h40,8'h40,8'h00};? ?// 54? 6

? ? ? mem_hanzi[? 16] ={8'h40,8'h30,8'hEF,8'h24,8'h24,8'h00,8'hFE,8'h92};//閿嬌娉2 3

? ? ? mem_hanzi[? 17] ={8'h92,8'h92,8'hF2,8'h92,8'h92,8'h9E,8'h80,8'h00};

? ? ? mem_hanzi[? 18] ={8'h40,8'h40,8'h40,8'h7C,8'h40,8'h40,8'h40,8'h7F};

? ? ? mem_hanzi[? 19] ={8'h44,8'h44,8'h44,8'h44,8'h44,8'h40,8'h40,8'h00};

? ? ? mem_hanzi[? 20] ={8'h10,8'h60,8'h02,8'h0C,8'hC0,8'h00,8'hF8,8'h88};

? ? ? mem_hanzi[? 21] ={8'h88,8'h88,8'hFF,8'h88,8'h88,8'hA8,8'h18,8'h00};

? ? ? mem_hanzi[? 22] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 23] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};? ? ??

? ? ? mem_hanzi[? 24] ={8'h01,8'h01,8'h7F,8'h21,8'h91,8'h60,8'h1F,8'h00};

? ? ? mem_hanzi[? 25] ={8'hFC,8'h44,8'h47,8'h44,8'h44,8'hFC,8'h00,8'h00};

? ? ? mem_hanzi[? 26] ={8'h00,8'h00,8'h7F,8'h40,8'h50,8'h48,8'h44,8'h43};

? ? ? mem_hanzi[? 27] ={8'h44,8'h48,8'h50,8'h40,8'hFF,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 28] ={8'h04,8'h04,8'h7C,8'h03,8'h80,8'h60,8'h1F,8'h80};?

? ? ? mem_hanzi[? 29] ={8'h43,8'h2C,8'h10,8'h28,8'h46,8'h81,8'h80,8'h00};/*"娉,2*/

? ? ? mem_hanzi[? 30] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 31] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 32] ={8'h00,8'h04,8'h84,8'h84,8'h84,8'h84,8'h84,8'h84};? //涓夎娉5

? ? ? mem_hanzi[? 33] = {8'h84,8'h84,8'h84,8'h84,8'h84,8'h04,8'h00,8'h00};

? ? ? mem_hanzi[? 34] ={8'h20,8'h10,8'hE8,8'h24,8'h27,8'h24,8'h24,8'hE4};

? ? ? mem_hanzi[? 35] ={8'h24,8'h34,8'h2C,8'h20,8'hE0,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 36] ={8'h10,8'h60,8'h02,8'h0C,8'hC0,8'h00,8'hF8,8'h88};

? ? ? mem_hanzi[? 37] ={8'h88,8'h88,8'hFF,8'h88,8'h88,8'hA8,8'h18,8'h00};

? ? ? mem_hanzi[? 38] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 39] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};? ? ??

? ? ? mem_hanzi[? 40] ={8'h20,8'h20,8'h20,8'h20,8'h20,8'h20,8'h20,8'h20};

? ? ? mem_hanzi[? 41] ={8'h20,8'h20,8'h20,8'h20,8'h20,8'h20,8'h20,8'h00};

? ? ? mem_hanzi[? 42] ={8'h80,8'h60,8'h1F,8'h09,8'h09,8'h09,8'h09,8'h7F};

? ? ? mem_hanzi[? 43] ={8'h09,8'h09,8'h49,8'h89,8'h7F,8'h00,8'h00,8'h00};/*"瑙,4*/

? ? ? mem_hanzi[? 44] ={8'h04,8'h04,8'h7C,8'h03,8'h80,8'h60,8'h1F,8'h80};

? ? ? mem_hanzi[? 45] ={8'h43,8'h2C,8'h10,8'h28,8'h46,8'h81,8'h80,8'h00};/*"娉,5*/

? ? ? mem_hanzi[? 46] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 47] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};? ? ??

? ? ? mem_hanzi[? 48] ={8'h08,8'h08,8'h08,8'h08,8'h08,8'hF8,8'h89,8'h8E};

? ? ? mem_hanzi[? 49] ={8'h88,8'h88,8'h88,8'h88,8'h08,8'h08,8'h08,8'h00};

? ? ? mem_hanzi[? 50] ={8'h10,8'h60,8'h02,8'h0C,8'hC0,8'h00,8'hF8,8'h88};?

? ? ? mem_hanzi[? 51] ={8'h88,8'h88,8'hFF,8'h88,8'h88,8'hA8,8'h18,8'h00};

? ? ? mem_hanzi[? 52] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 53] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};??

? ? ? mem_hanzi[? 54] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 55] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};? ? ? ? ? ??

? ? ? mem_hanzi[? 56] ={8'h00,8'h80,8'h40,8'h20,8'h18,8'h07,8'h00,8'h00};

? ? ? mem_hanzi[? 57] ={8'h40,8'h80,8'h40,8'h3F,8'h00,8'h00,8'h00,8'h00};/*"鏂,6*/

? ? ? mem_hanzi[? 58] ={8'h04,8'h04,8'h7C,8'h03,8'h80,8'h60,8'h1F,8'h80};

? ? ? mem_hanzi[? 59] = {8'h43,8'h2C,8'h10,8'h28,8'h46,8'h81,8'h80,8'h00};/*"娉,7*/

? ? ? mem_hanzi[? 60] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 61] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};??

? ? ? mem_hanzi[? 62] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 63] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 64] ={8'h00,8'h02,8'h02,8'hC2,8'h02,8'h02,8'h02,8'hFE};//姝e雞娉89

? ? ? mem_hanzi[? 65] ={8'h82,8'h82,8'h82,8'h82,8'h82,8'h02,8'h00,8'h00};

? ? ? mem_hanzi[? 66] ={8'h02,8'hE2,8'h22,8'h22,8'h3E,8'h00,8'h08,8'h88};

? ? ? mem_hanzi[? 67] = {8'h48,8'h39,8'h0E,8'h08,8'hC8,8'h08,8'h08,8'h00};

? ? ? mem_hanzi[? 68] ={8'h10,8'h60,8'h02,8'h0C,8'hC0,8'h00,8'hF8,8'h88};?

? ? ? mem_hanzi[? 69] ={8'h88,8'h88,8'hFF,8'h88,8'h88,8'hA8,8'h18,8'h00};

? ? ? mem_hanzi[? 70] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 71] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};? ? ??

? ? ? mem_hanzi[? 72] ={8'h40,8'h40,8'h40,8'h7F,8'h40,8'h40,8'h40,8'h7F};

? ? ? mem_hanzi[? 73] ={8'h40,8'h40,8'h40,8'h40,8'h40,8'h40,8'h40,8'h00};/*"姝,8*/

? ? ? mem_hanzi[? 74] ={8'h00,8'h43,8'h82,8'h42,8'h3E,8'h00,8'h21,8'h71};

? ? ? mem_hanzi[? 75] ={8'h29,8'h25,8'h23,8'h21,8'h28,8'h70,8'h00,8'h00};/*"寮,9*/

? ? ? mem_hanzi[? 76] ={8'h04,8'h04,8'h7C,8'h03,8'h80,8'h60,8'h1F,8'h80};

? ? ? mem_hanzi[? 77] ={8'h43,8'h2C,8'h10,8'h28,8'h46,8'h81,8'h80,8'h00};/*"娉,10*/

? ? ? mem_hanzi[? 78] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};

? ? ? mem_hanzi[? 79] ={8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00,8'h00};? ? ??

? ? end

endmodule

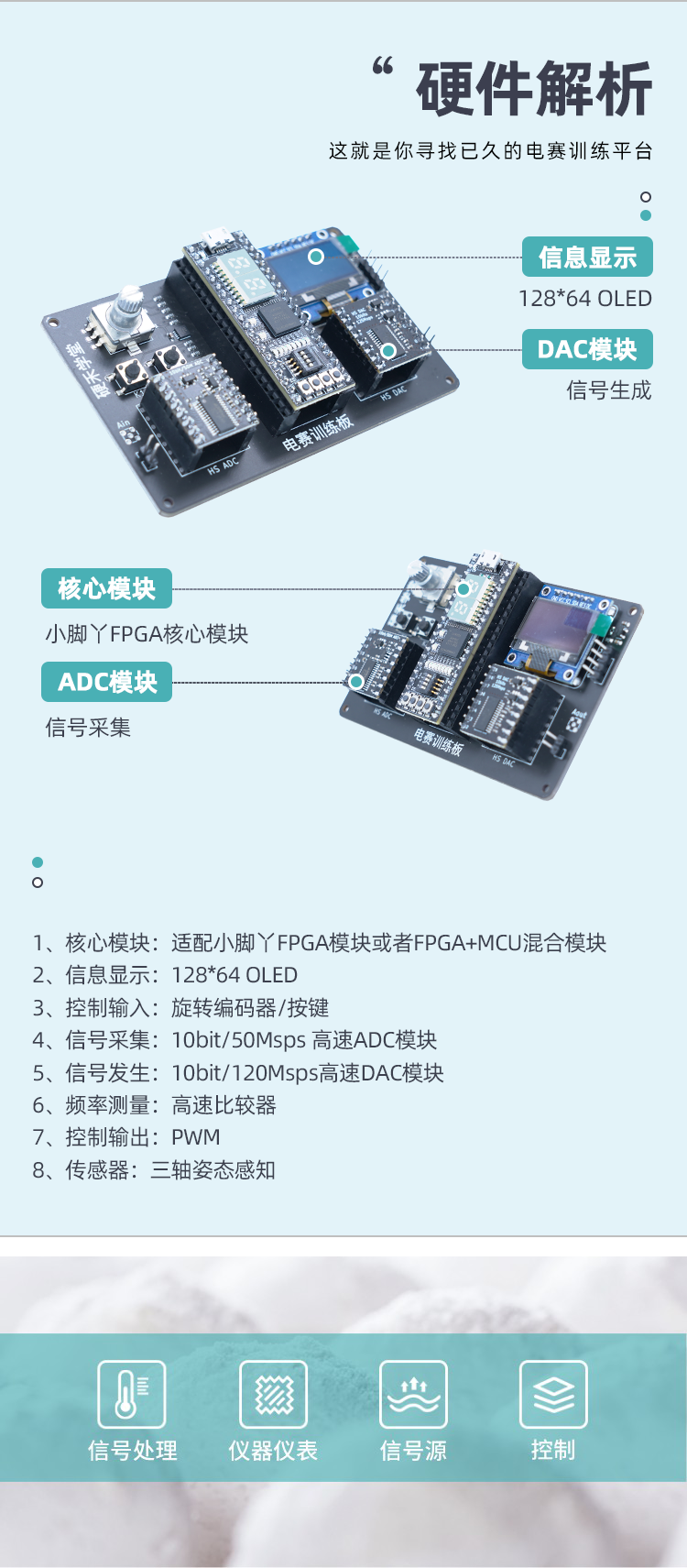

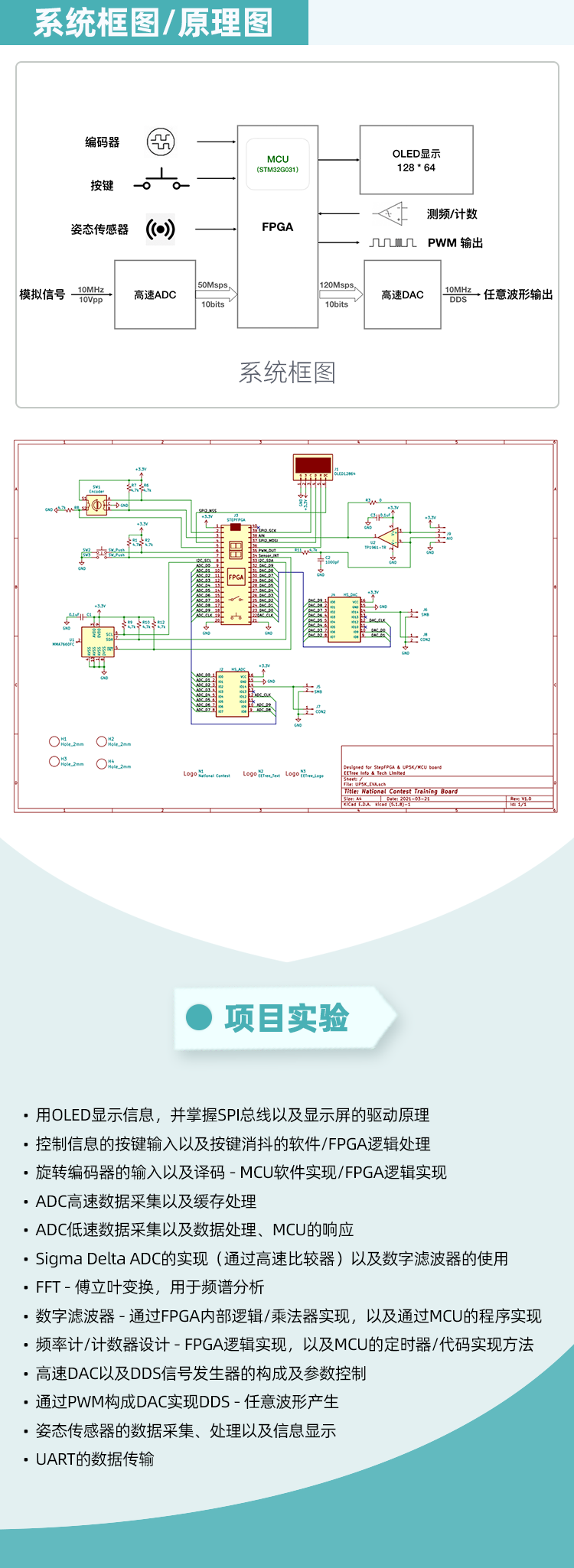

關(guān)于這個(gè)板卡的功能介紹如下:

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論