對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局

2014-08-28 17:10:03 8153

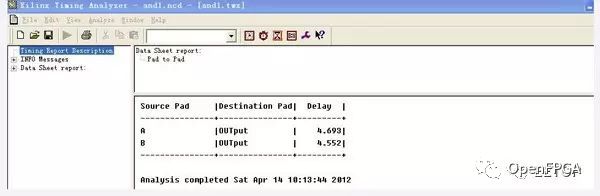

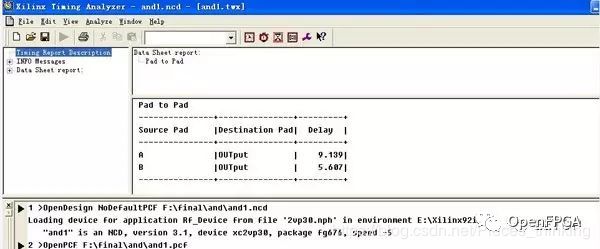

8153 信號在FPGA器件中通過邏輯單元連線時,一定存在延時。延時的大小不僅和連線的長短和邏輯單元的數目有關,而且也和器件的制造工藝、工作電壓、溫度等有關。

2020-03-29 10:27:00 3276

3276 影響電路工作的可靠性、穩定性,嚴重時會導致整個數字系統的誤動作和邏輯紊亂。下面就來討論交流一下FPGA 的競爭冒險與毛刺問題。

在數字電路中,常規介紹和解釋:

什么是競爭與冒險現象:

在組合電路中

2023-11-02 17:22:20

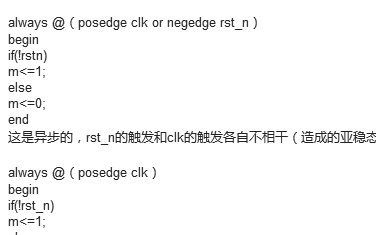

的,亞穩態主要發生在異步信號檢測、跨時鐘域信號傳輸以及復位電路等常用設計中。03 亞穩態危害由于產生亞穩態后,寄存器 Q 端輸出在穩定下來之前可能是毛刺、振蕩、固定的某一電壓值。在信號傳輸中產生亞穩態

2020-10-22 11:42:16

冒險往往會影響到邏輯電路的穩定性。時鐘端口、清零和置位端口對毛刺信號十分敏感,任何一點毛刺都可能會使系統出錯,因此判斷邏輯電路中是否存在冒險以及如何避免冒險是設計人員必須要考慮的問題。如何處理毛刺

2018-08-01 09:53:36

競爭冒險:在組合電路中,當邏輯門有兩個互補輸入信號同時向相反狀態變化時,輸出端可能產生過渡干擾脈沖的現象,稱為競爭冒險。那么 FPGA 產生競爭冒險的原因是什么呢? 信號在 FPGA 器件內部通過

2024-02-21 16:26:56

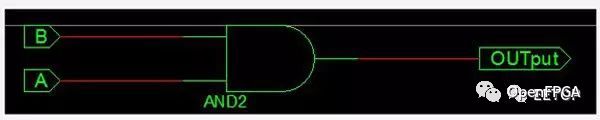

用FPGA做DDS,請教這種由于輸出信號的各位跳變時間有差異導致的毛刺怎么解決?

2017-05-17 09:57:54

有先有后,這種時差引起的現象稱為競爭(Race)。競爭的結果將很可能導致冒險(Hazard)發生(例如產生毛刺),造成錯誤的后果,并影響系統的工作。組合邏輯電路的冒險僅在信號狀態改變的時刻出現毛刺,這種冒險

2014-06-30 15:45:20

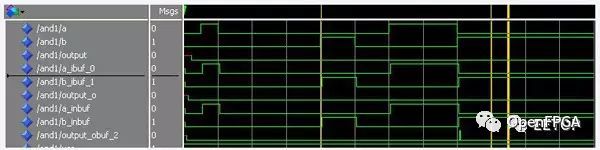

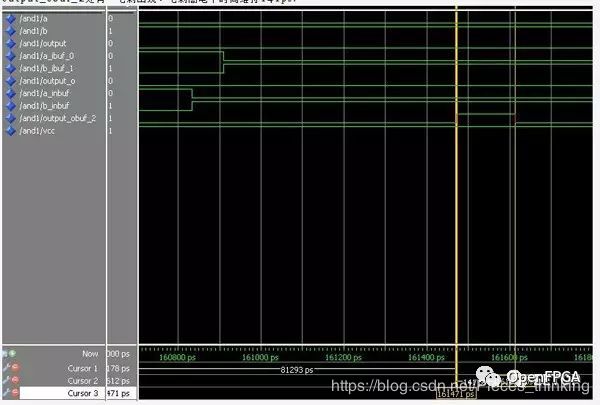

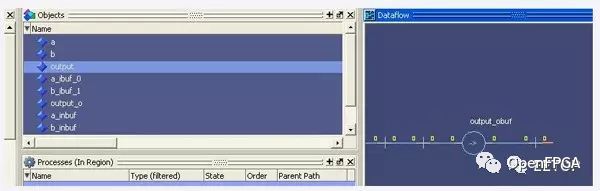

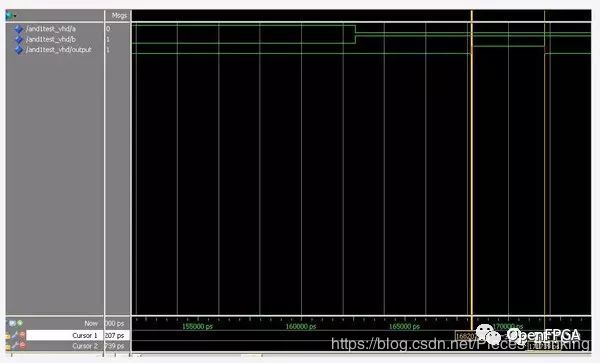

,我們稱之為“毛刺”。如果一個組合邏輯電路中有毛刺出現,就說明該電路存在“冒險”。(特權同學,版權所有)下面我們可以列舉一個簡單例子來看看毛刺現象是如何產生和消除的。如圖5.14所示,這里在圖5.10

2015-07-08 10:38:02

電路輸出發生瞬時錯誤的現象叫做冒險。(也就是由于競爭產生的毛刺叫做冒險)

判斷方法:

1)代數法:如果布爾式中有相反的信號則很有可能產生競爭和冒險現象;

2)圖形法:有兩個相切的卡諾圈并且相切處沒有被

2023-11-03 10:39:27

摘要:FPGA異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

FPGA 20 位總線輸入經過164245轉換后,高低電平變化時有時有毛刺,能達到4.6V。不知會不會燒壞FPGA。也沒找到技術支持電話。哪位大哥哥幫幫我。謝謝了

2013-07-15 15:01:45

FPGA的IO口輸出20M頻率方波信號,上升沿和下降沿有毛刺怎么辦?串聯磁珠或者匹配電阻有效嗎?同事想的辦法是在后面加個高頻的運放組成的射極跟隨器。我認為毛刺會通過射極跟隨器走到下一級電路。不知道怎么解決好?

2019-01-21 06:35:23

在FPGA的設計中,毛刺現象是長期困擾電子設計工程師的設計問題之一,是影響工程師設計效率和數字系統設計有效性和可靠性的主要因素。由于信號在FPGA的內部走線和通過邏輯單元時造成的延遲,在多路信號變化

2012-09-06 14:37:54

,提高電路的穩定性,而且其先進的開發工具使整個系統的設計調試周期大大縮短。而在FPGA設計中也存在一些難點問題,本文將主要分析、討論毛刺信號的產生原因及消除毛刺的方法。通過綜合運用這些方法,可以最大

2009-04-21 16:47:58

摘 要:以現場可編程門陣列(以下簡稱FPGA)在設計中由于其內部構成,容易引起競爭問題。以我們在實驗教學中的應用與實踐為主線,詳細介紹了消除競爭冒險的各種方法。關鍵詞:現場可編程

2009-04-21 16:44:44

下面對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用

2021-06-30 07:00:00

FPGA連續信號給到AD9736,但是總會有周期毛刺出現,如圖

邏輯分析儀檢查FPGA的輸出信號,沒有該毛刺出現

2023-12-18 06:16:33

FPGA連續信號給到AD9736,但是總會有周期毛刺出現,如圖邏輯分析儀檢查FPGA的輸出信號,沒有該毛刺出現

2018-09-10 11:13:52

數字邏輯電路中的兩個基本門電路,A、B經過不同的傳輸途徑達到,那么在設計時往往難于準確知道A、B到達次序的先后,以及它們在上升時間和下降時間上的細微差異。因此,我們只能說只要存在競爭現象,輸出就有可能

2023-02-21 15:35:38

,因此毛刺現象在PLD、FPGA設計中尤為突出) 圖2給出了一個邏輯冒險的例子,從圖3的仿真波形可以看出,"A、B、C、D"四個輸入信號經過布線延時以后,高低電平變換不是同時發生

2012-02-10 09:50:36

fpga的gnd)。現在能正常控制電機。但是只要電機驅動一通電,用邏輯分析儀看fpga輸出的自定義調試信號時 發現有大量高頻毛刺。為此在fpga和電機驅動模塊之間加了56v二極管。現在電機驅動通電但是電機不

2017-09-15 17:46:04

我用FPGA控制ad7865采集數據時,采集到的正弦波數據波形出現一些毛刺現象,請問該怎么解決,謝謝幫忙!

2014-06-07 00:00:30

錯位現象得到明顯好轉。示波器探頭測量信號時相當于并聯上一個pF級的電容,也能夠一定程度上起到濾波的效果,因此可以斷定同步信號的毛刺影響了數據的采集。其中一個同步信號如圖1,兩個有效高脈沖之間有很多毛刺

2019-06-04 05:00:17

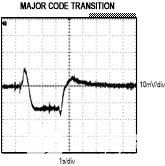

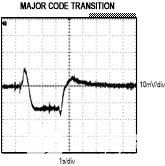

下圖是從AD5764芯片手冊中截取的。

下圖除了0 - 2.0us 是毛刺,其余部分都是穩定在了-6mV 。

我的問題是:我用示波器測量我的波形的時候,到處都是大約20mV的毛刺。沒有像這么穩定的 -6mV 。請問這是什么原因?

另外我想知道下圖您是用示波器側的嗎,您的電路是什么樣的呢?

2023-12-12 07:16:26

我使用AD5781的評估板,輸出10Hz 100mV的正弦波,我讀入AD7768-1的數據再通過AD5781輸出,我AD7768-1采集的數據中沒有毛刺,但我AD5781輸出的數據經過運放

2023-12-07 06:04:30

最近使用AD768的過程中發現,在數據轉換過程中伴隨時鐘信號的下降沿有一個4mV左右的毛刺,同時注意到fpga到da的數據線上也有這個現象,兩者之間是通過74alvc164245完成電平轉換的,現在想辦法去掉這個毛刺,請問有些什么好的建議!

2018-12-07 09:41:12

最近使用AD768的過程中發現,在數據轉換過程中伴隨時鐘信號的下降沿有一個4mV左右的毛刺,同時注意到fpga到da的數據線上也有這個現象,兩者之間是通過74alvc164245完成電平轉換的,現在想辦法去掉這個毛刺,請問有些什么好的建議!

2023-12-22 06:59:24

在測試AD9117時,用FPGA給DAC一個正弦波的數字信號,在輸出端發現有脈沖毛刺出現,在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認為是毛刺造成,請問是否知道關于這個毛刺生成的有關原因

2023-12-13 06:19:05

在測試AD9117時,用FPGA給DAC一個正弦波的數字信號,在輸出端發現有脈沖毛刺出現,在示波器上有毛刺的余暉。在頻譜上會有底噪抖動,我認為是毛刺造成,請問是否知道關于這個毛刺生成的有關原因

2019-01-17 08:19:07

前端電路輸入標準的正弦波,AD9681采集到的數據通過串行LVDS發送的到FPGA,這是FPGA采集到的波形:上邊沿下邊沿出現了規則的毛刺。前期排查:1、將拜倫變壓器后端的差分模擬信號飛線到另一

2019-01-18 16:33:32

前端電路輸入標準的正弦波,AD9681采集到的數據通過串行LVDS發送的到FPGA,這是FPGA采集到的波形:上邊沿下邊沿出現了規則的毛刺。

前期排查:

1、將拜倫變壓器后端的差分模擬信號飛

2023-12-12 06:00:44

我們目前在做一個超寬帶的項目,信號帶寬528MHz發端送給射頻的信號采樣率為2.112Gbps,由于是I Q兩路送入射頻,所以我們的硬件板上有兩片AD9739,在FPGA內部我們的數據速率

2018-12-11 11:33:51

黃色為Vtune電壓,藍色為MUXOUT鎖定指示。如圖所示,黃色尖狀毛刺出現時,未鎖定。請問是,ADF4153A器件原因造成的隨機性不鎖定現象嘛?并且會在不鎖定的時刻出現毛刺。

2018-08-03 07:53:20

各位大神: 我在使用ADIS16209進行靜態測試的時候,輸出的雙軸加速度計輸出會出現毛刺,具體現象如圖所示,請各位大神幫忙分析原因。

2018-12-19 09:27:03

用LSM6DSM芯片,采集三軸加速度信號,出現如下的毛刺現象電路原理圖如下請問大家遇到過類此問題嘛,怎么解決的!謝謝!!

2019-04-02 19:39:40

在組合邏輯中,由于門的輸入信號通路中經過了不同的延時,導致到達該門的時間不一致叫競爭。產生毛刺叫冒險。 如果布爾式中有相反的信號則可能產生競爭和冒險現象。 解決方法:一是添加布爾式的消去項,二是在芯片外部加電容。

2019-08-02 11:57:35

,但是將程序下載到電路板上發現輸出端的信號為:

這個圖是通過示波器直接測芯片DAC0輸出端的波形,而且該輸出端未接任何東西,2.5v電壓正常,但是會出現周期性的毛刺,毛刺大致值為180mV左右

2024-01-12 07:44:18

控制fpga進行,該階躍信號連接到fpga的某個引腳。發現在PCI-6733輸出的波形在時鐘的邊沿有毛刺。請問毛刺是什么原因呀?是時鐘的質量不夠好嗎?還是接地有什么問題?

2020-05-17 09:24:09

如何解決電路中短時脈沖波形失真的所謂“毛刺”現象?并提出相應的解決辦法。

2021-04-08 06:25:08

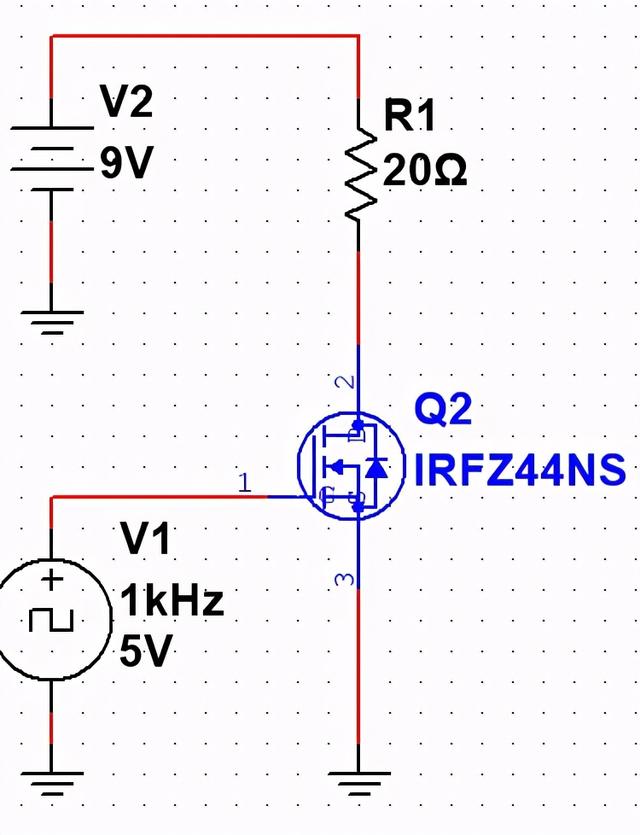

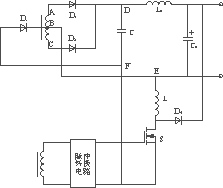

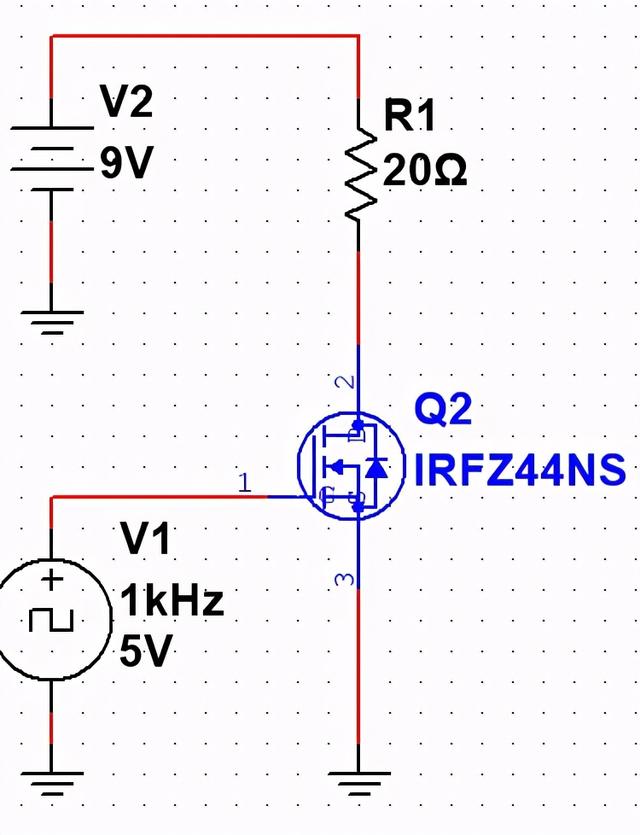

毛刺現象是我們每一個電子愛好者避之唯恐不及的,今天我們來學習一個毛刺現象以及如何規避它,進而掌握電感升壓的原理。簡單場管開關電路讓我們從一個簡單的電路開始,該電路使用一個 N 溝道場效應管控制 20

2021-12-30 07:09:17

用FPGA做數字頻率計 捕捉上升沿低頻部分的方波是靠比較器產生的 LM339KHz級別還好Hz級的信號 頻率越低 示波器拉開看 產生的信號上升沿里面全是毛刺低頻部分 使用LM339的探測范圍要求

2016-06-28 18:31:31

小弟今日碰到如下難題,請教站內高手幫忙解析一下,跪謝200mv(可能本身就有毛刺)的工頻信號經過下圖電路積分移相后,輸出的波形有很多毛刺,不能達到測試要求,試過好多方法對積分移

2010-02-09 16:42:25

小弟今日碰到如下難題,請教站內高手幫忙解析一下,跪謝200mv(可能本身就有毛刺)的工頻信號經過下圖電路積分移相后,輸出的波形有很多毛刺,不能達到測試要求,試過好多方法對積分移

2010-02-09 16:44:09

小弟今日碰到如下難題,請教站內高手幫忙解析一下,跪謝200mv(可能本身就有毛刺)的工頻信號經過下圖電路積分移相后,輸出的波形有很多毛刺,不能達到測試要求,試過好多方法對積分移

2010-02-09 16:39:56

,就說明該電路存在“冒險”。(與分立元件不同,由于 PLD 內部不存在寄生電容電感,這些毛刺將被完整的保留并向下一級傳遞,因此毛刺現象在 PLD、FPGA 設計中尤為突出)。毛刺的累加,將會影響整個

2023-05-30 17:15:28

的看到毛刺現象(圖3-數字處理過程中已減去直流偏置),數字量采樣時 采樣了4次,去掉最大和最小值,在進行平均的;如果僅采樣一次,那毛刺更大。一開始懷疑是3.3V電壓源的問題(產生直流偏置,和對AD口進行

2018-10-08 17:02:49

想測頻10-300kHz,信號跳變的時候毛刺很多,硬件定型了,只能用fpga濾波,誰有比較好的解決方法,能有現成代碼最好了,謝謝啦

2013-11-29 23:08:31

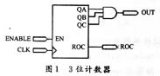

)。17.FPGA 設計中如何實現同步時序電路的延時?首先說說異步電路的延時實現:異步電路一半是通過加 buffer、兩級與非門等(我還沒用過所以也不是很清楚),但這是不適合同步電路實現延時的。在同步電路中,對于

2019-08-16 08:30:00

最新的化學去毛刺工藝

一提到去毛刺,很多人馬上聯想到的是洗磨。洗磨是現在運用最為普遍的一種去毛

2009-03-20 13:39:22 1055

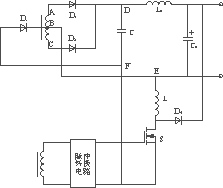

1055 高頻整流電路中的新型電壓毛刺無損吸收電路

0 引言

電壓毛刺是高頻變換器研制和生產過程中的棘手問題,處理得不好會帶來許多的

2009-07-06 08:27:55 1134

1134

電路的諧振現象分析

諧振現象是交流電路中產生的一種特殊現象,對諧振現象的研究有著重要的意義。在實

2009-07-27 08:11:02 10045

10045

組合邏輯中的競爭與冒險及毛刺的處理方法 在組合邏輯中,由于門的輸入信號通路中經過了不同的延時,導致到達該門的時間不一致叫競爭。產生毛刺叫冒險。如果布爾式中有相反的信號則可能產生競爭和冒險現象。解決方法:一是添加布爾式的(冗余)消去項,但是不

2011-01-24 18:12:53 0

0 本文從FPGA的原理結構的角度探討了產生毛刺的原因及產生的條件,在此基礎上,總結了多種不同的消除方法,在最后結合具體的應用對解決方案進行深入的分析。

2011-08-03 11:48:15 1931

1931

和所有的數字電路一樣,毛刺也是FPGA電路中的棘手問題,它的出現會影響電路工作的穩定性,可靠性,嚴重時會導致整個數字系統的誤動作和邏輯紊亂。

2017-02-11 03:59:38 1626

1626

的濾波電路。 SDA 或 SCL 線路上的毛刺會導致信號線路的瞬間錯誤觸發。 SDA 上的毛刺會導致錯誤 START 條件或錯誤 STOP 條件的識別,從而破壞總線協議。 SCL 上的毛刺會導致錯誤的數據傳輸,也會破壞總線協議。

2018-06-29 14:00:00 17133

17133 毛刺現象在FPGA設計中非常普遍, 而毛刺的出現往往導致系統結果的錯誤。本文從FPGA的原理結構的角度深入探討了毛刺產生的原因及產生的條件,總結了多種不同的解決方法,并結合具體的應用對解決方案進行

2017-11-22 14:24:54 8414

8414 鑄鐵去毛刺,切冒口,切焊口。鋁件去毛刺,發動機殼去毛刺

2017-11-24 14:40:53 3

3 數字電路設計人員經常面臨的挑戰之一是要消除所設計電路的毛刺信號。為此,通常需要確保數據鎖存期間具有足夠的建立時間以及保持時間。 毛刺是不能在整個時鐘周期內都保持有效的信號。帶毛刺的信號如果饋送

2018-03-27 18:46:00 1

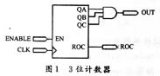

1 通過改變設計,破壞毛刺產生的條件,來減少毛刺的發生。例如,在數字電路設計中,常常采用格雷碼計數器取代普通的二進制計數器,這是因為格雷碼計數器的輸出每次只有一位跳變,消除了競爭冒險的發生條件,避免了毛刺的產生。

2018-06-23 08:49:00 1613

1613

大家好,又到了每日學習的時間了,今天我們來聊一聊FPGA學習中,亞穩態現象。 說起亞穩態,首先我們先來了解一下什么叫做亞穩態。亞穩態現象:信號在無關信號或者異步時鐘域之間傳輸時導致數字器件失效的一種

2018-06-22 14:49:49 3222

3222

高壓包的高壓卡簧與高壓線連接焊點有毛刺,毛刺尖端會產生放電現象,若放電,會將高壓帽橡膠燒老化。所以說如果家里或下雨季節,家里比較潮濕,電視機高壓卡簧與高壓線連接焊點的毛刺會發電,導致電視高壓包損壞。

2019-01-22 17:04:46 31358

31358 毛刺的英文名是veining,一般金屬件表面出現余屑和表面極細小的顯微金屬顆粒,這些被稱為毛刺。毛刺越多,其質量標準越低。所以企業生產產品的時候都會想辦法盡量減少出現的毛刺。

2019-04-29 16:03:57 11433

11433 去毛刺,就是去除在零件面與面相交處所形成的刺狀物或飛邊。毛刺的危害性尤為明顯, 逐漸引起人們的普遍重視, 并開始對毛刺的生成機理及去除方法進行研究。

2019-05-22 11:24:14 8338

8338 毛刺其實是一種金屬鑄造、銑切、電鍍術語。毛刺的英文名是veining,一般金屬件表面出現余屑和表面極細小的顯微金屬顆粒,這些被稱為毛刺。毛刺越多,其質量標準越低。所以企業生產產品的時候都會想辦法盡量減少出現的毛刺。

2019-05-22 14:24:56 8647

8647 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。 流程: 1. 異步復位: 優點:⑴大多數

2020-10-30 12:17:55 323

323 決這個問題,愛奇藝深度學習平臺團隊經過多個階段的優化實踐,最后對 TF Serving 和 TensorFlow 的源碼進行深入優化,將模型熱更新時的毛刺現象解決,本文將分享 TensorFlow

2020-12-17 16:48:47 3930

3930 LTC6994-1LTC1541演示電路-帶毛刺抑制器的高精度、功耗、過壓檢測器

2021-06-03 08:18:16 9

9 毛刺現象是我們每一個電子愛好者避之唯恐不及的,今天我們來學習一個毛刺現象以及如何規避它,進而掌握電感升壓的原理。簡單場管開關電路讓我們從一個簡單的電路開始,該電路使用一個 N 溝道場效應管控制 20

2022-01-10 10:53:27 4

4 當DAC輸出模擬值發生變化時,在DAC輸出端觀察到動態現象,表現為毛刺,如圖1所示。該毛刺能量定義為電壓曲線下的面積與示波器上捕獲的時間圖的關系。該毛刺能量的單位是nV × s。

2022-12-15 11:53:04 1858

1858

在電源電壓超過±5V的R-2R DAC設計中,DAC的主要進位轉換期間可能會出現較大的電壓毛刺(高達1.5V)。這些毛刺會傳播到輸出緩沖放大器,并出現在輸出端。控制頂部 (VREF+) 和底部 (VREF-) 單刀雙擲開關(S0 至 SN)的電平轉換器的回轉會導致毛刺(圖 1)。

2023-02-24 17:10:06 1767

1767

示波器波形毛刺通常是由信號本身帶來的噪聲或者示波器本身的問題造成的。下面是一些減少示波器波形毛刺的方法

2023-05-02 09:55:00 15997

15997 在金屬制品加工中不可避免的出現各種毛刺,這些毛刺對工件質量產生嚴重的影響,因此去毛刺成為后續加工中一個必不可少的工序。以前大多企業通過人工去毛刺,但現在機械手裝配速科德Kasite浮動去毛刺主軸,將去毛刺工藝提高到一個新的水平。

2022-06-14 16:52:29 551

551

毛刺危害大,目前去毛刺有機器人去毛刺、人工去毛刺、化學去毛刺、高溫去毛刺、滾磨去毛刺、研磨去毛刺、沖模去毛刺等多種方法。其中機器人浮動去毛刺能力穩定,生產效率高,易于實現自動化數控,對于精度要求高或造型復雜的零件毛刺也能輕松去除。 ???

2022-11-29 10:20:59 417

417

當錫膏焊接完成后,我們可能會發現,錫膏的邊緣并不平整,表面有毛刺或玷污,遇到這樣的問題該怎么辦?下面錫膏廠家來為大家講解一下:首先我們來分析下造成這種現象的根源:一、PCB板焊后成型模糊:錫膏邊緣

2023-05-29 09:35:30 464

464

毛刺現象是我們每一個電子愛好者避之唯恐不及的,今天我們來學習一個毛刺現象以及如何規避它,進而掌握電感升壓的原理。

2023-08-15 14:53:20 2103

2103

浮動主軸壓鑄鋁去毛刺技術是一種高效、精準的去毛刺方法,通過旋轉切割工具和主軸相對運動來去除壓鑄鋁制品表面的毛刺。該技術具有減少加工時間和成本、提高加工精度、適用于不同形狀和材料的工件等優點。浮動主軸

2023-09-18 14:46:32 366

366

機械臂去毛刺主軸是一種高效的自動化去毛刺技術,廣泛應用于金屬加工和汽車零部件加工等領域。通過高速旋轉的主軸和精確控制的機械臂,實現高精度、高效率、高質量的自動化去毛刺作業,提高生產效率和產品質量,降低人工操作風險,提高作業安全性。

2023-11-28 13:41:19 179

179

什么是毛刺?毛刺的大小和方向 如何測量毛刺的尺寸?如何檢查已去除的毛刺? 毛刺是指由于加工工藝或其他原因產生的金屬表面上的不平整區域或小尖刺。毛刺通常形成于金屬的切削或沖壓過程中,可能會影響產品

2023-12-07 14:24:36 1284

1284 如何最小化毛刺尺寸?如何控制毛刺方向? 為了得到高質量的產品或工藝品,我們通常需要把毛刺的尺寸最小化,并控制其方向。毛刺會影響制品的外觀質量、功能性能以及使用壽命。本文將介紹毛刺的形成原因、影響因素

2023-12-07 14:24:39 213

213 PCB鉆孔毛刺產生的原因及毛刺的危害 PCB(Printed Circuit Board)是一種非常重要的電子組件,被廣泛應用于各種電子設備中。在PCB的生產過程中,鉆孔是一個非常關鍵的步驟,用于

2023-12-07 14:24:41 1345

1345 什么是緊固件毛刺呢?緊固件毛刺是怎么樣形成的呢?要如何很好的去除這種毛刺呢? 緊固件毛刺是指在緊固件(如螺釘、螺帽、螺栓等)的表面形成的一層或多層細小的突起。這些毛刺通常是由于制造過程中的不完

2023-12-07 14:24:44 287

287 沖裁加工時總是會產生毛刺,很難消除掉,因此,經常在加工后進行壓毛刺來消除毛刺。鑒于分型面的問題,最近使用去毛刺的方式有增加的趨勢.

2023-12-12 14:17:08 240

240

信號毛刺是指信號中出現的突然幅度變化,通常表現為信號波形上的尖峰或震蕩。這種現象可能會導致電子設備的不穩定性,甚至影響設備的正常運行。為了準確觀察信號毛刺并找出其原因,使用示波器是一種常見的方法。本文將介紹如何使用示波器觀察信號毛刺,并給出一些常見的處理方法。

2023-12-26 15:04:48 330

330

電子發燒友App

電子發燒友App

評論