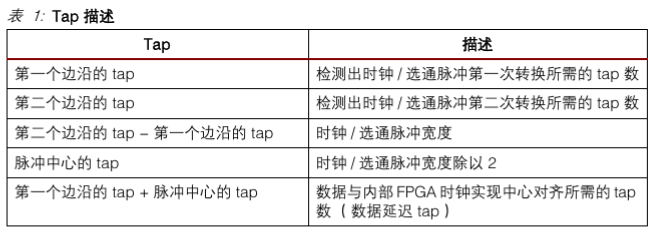

配置歷史回顧當FPGA首次面世時,可選擇的配置存儲器是并行EPROM或并行EEPROM產品。隨著時間的推移,NOR閃存技術應運而生,同時因其系統內可重復編程性和高性價比而被廣泛采用。在第二次革命性轉折

2021-09-03 07:00:00

各位大神好,我想用FPGA讀寫DRAM存儲器,求大神指點哪位大佬有代碼分析一份更是感激不盡,好人一生平安。

2018-01-14 15:31:32

的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能,FPGA允許無限次的編程。圖

2023-02-23 15:24:55

存儲器接口生成器(MIG)解決方案---Virtex-4 存儲器接口和Virtex-II Pro存儲器解決方案 Virtex-4? FPGAs solve

2009-10-24 12:02:14

文章目錄前言一、 存儲器與通用寄存器1. 存儲器2. 通用寄存器前言上一章我們曾簡單的介紹過計算機中的一些硬件和軟件的相關概念,還不熟悉的小伙伴可以點擊下面的鏈接進行預習:[匯編語言] - 匯編語言

2021-12-13 06:29:53

存儲器的理解存儲器是由簡單的電子器件例如PMOS管、NMOS管進行組合形成邏輯上的與非或門,之后在此基礎上,形成組合邏輯用于存儲信息,例如R-S鎖存器和門控D鎖存器,進而進一步組合復雜化,形成我們

2021-12-10 06:54:11

技術的日趨成熟,存儲器價格會回穩.然而就DRAM市場來說,誰也不知道DRAM的供貨何時才會穩定下來.再來看市場需求狀況,雖然有些存儲器市場分段的市場需求正在增長,但是這些分段的增長幅度并不高,可見主要的問題是來自于供給側.

2019-07-16 08:50:19

信號(包括YCbCr數據流、行場同步信號和像素時鐘)經ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉換,再將轉換后的每個像素的RGB值寫入SDRAM存儲器。再由

2019-05-05 09:29:33

作者:武漢大學物理科學與技術學院 趙東方 李雄 于心亮 程方敏引言本文從實際應用的角度出發,采用FPGA作為主控芯片,設計了一款數字視頻接口轉換設備,該設備針對于MT9M111這款數字圖像傳感器產生

2019-04-23 07:00:10

ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉換,再將轉換后的每個像素的RGB值寫入SDRAM存儲器。再由FPGA主控芯片按照輸出分辨率的要求從SDRAM存儲器中

2019-05-29 05:00:03

同步信號和像素時鐘)經ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉換,再將轉換后的每個像素的RGB值寫入SDRAM存儲器。再由FPGA主控芯片按照輸出分辨率

2019-04-17 07:00:05

針對基于SRAM工藝的器件的下載配置問題,本文介紹采用AT89S2051單片機配合串行E2PROM存儲器,實現CPLD/FPGA器件的被動串行(PS)模式的下載配置。

2021-04-13 06:25:40

。在結構上的改進主要包括可變寬度的存儲器接口、更快速的指令周期時間、可設置優先級的雙通道DMA處理器、靈活的引導程序裝入方式、可重新定位的中斷向量表以及可選的邊緣/電平觸發中斷方式等。 1

2019-06-12 05:00:08

選用大容量NOR Flash存儲器來存儲配置碼流,并利用JTAG接口完成配置碼流下載的FPGA多配置解決方案。與System ACE方案相比,該方案不僅能快速完成多個配置碼流的下載,還具有更高的配置速度

2019-05-30 05:00:05

庫的慢-慢工藝點對塊進行合成,以200 MHz的目標速度確認時序特性。

接口存儲器端口上的信號符合RAM編譯器為TSMC CL013G工藝技術生產的單端口同步存儲器組件所要求的時序要求

2023-08-21 06:55:33

本章節介紹了 Cyclone? IV 器件的存儲器接口管腳的支持以及外部存儲器接口的特性。除了大量供應的片上存儲器,Cyclone IV 器件可以很容易地與各種外部存儲器件建立連接,其中包括

2017-11-14 10:12:11

。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中

2019-05-24 05:00:34

DDR3存儲器接口控制器是什么?有什么優勢?

2021-04-30 06:57:16

本應用指南展示了與DS80C320存儲器接口有關的關鍵時序,以及各種CPU晶振頻率所需的存儲器速度。

2014-09-23 13:38:01

EVERSPIN非易失性存儲器嵌入式技術

2020-12-21 07:04:49

問題一:位圖都存儲在哪了?都在程序存儲器里嗎問題二:能不能將位圖存儲到外部內存中?問題三:F429的程序存儲器和數據存儲器有多大?

2020-05-20 04:37:13

FIFO存儲器是系統的緩沖環節,如果沒有FIFO存儲器,整個系統就不可能正常工作,它主要有幾方面的功能:1)對連續的數據流進行緩存,防止在進機和存儲操作時丟失數據;2)數據集中起來進行進棧和存儲,可

2022-01-18 10:03:06

嵌入式系統的海量存儲器多采用Flash存儲器實現擴展,由于Flash存儲器具有有限寫入次數的壽命限制,因此對于Flash存儲器局部的頻繁操作會縮短Flash存儲器的使用壽命。如何設計出一個合理

2019-08-16 07:06:12

DDR3 IC(實現 36 位接口),或額外的 8 位 DDR3 IC(實現 72 位接口)以存放與整個外部數據空間相關的 ECC 值。 總結 新型 KeyStone 架構在存儲器架構方面具備各種優勢

2011-08-13 15:45:42

本來想用一多維數組來發揮存儲的作用(周期控制算法需要),可是在幾層的While循環中,會多次的初始化數組;后來采用存儲器模塊(如圖),實際運行時達不到理想的控制效果,存儲器模塊的help講的也太簡略

2020-05-14 13:39:49

Molex推出下一代高性能超低功率存儲器技術

2021-05-21 07:00:24

。 2、硬盤存儲器 信息可以長期保存,可以讀寫,容量大,但是不方便攜帶。 3、移動存儲器 主要包括閃存盤(優盤)、移動硬盤、固態硬盤(SSD)。 4、閃存盤(優盤) 采用Flash存儲器(閃存

2019-06-05 23:54:02

關于數Gpbs高速存儲器接口設計的分析,看完你就懂了

2021-05-19 06:38:12

性存儲器:指當電源被關斷之后,數據隨即消失的存儲器(如.RAM隨機存儲器 ) 。這種存儲器的特點是一般采用CMOS技術,以降低功耗。并且采用并行方式傳輸數據,因而具有高速存取數據的能力。這種存儲器

2020-12-25 14:50:34

復雜可編程邏輯器件—FPGA技術在近幾年的電子設計中應用越來越廣泛。FPGA具有的硬件邏輯可編程性、大容量、高速、內嵌存儲陣列等特點使其特別適合于高速數據采集、復雜控制邏輯、精確時序邏輯等場合的應用。而應用FPGA中的存儲功能目前還是一個較新的技術。

2019-10-12 07:32:24

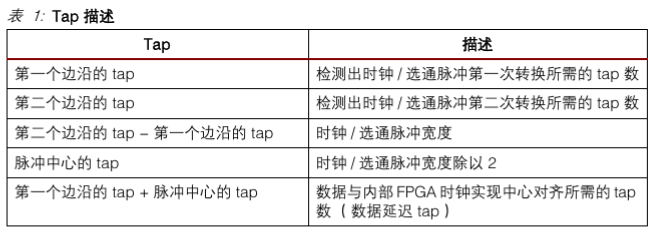

高性能系統設計師在滿足關鍵時序余量的同時要力爭獲得更高性能,而存儲器接口設計則是一項艱巨挑戰。雙倍數據速率SDRAM和4倍數據速率SDRAM都采用源同步接口來把數據和時鐘(或選通脈沖)由發射器傳送

2019-04-29 07:00:06

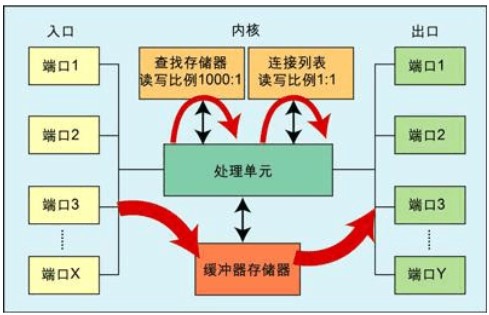

使用新的UniPHY架構。存儲器接口的底層架構和外部接口如圖1所示。從圖1可見,整個存儲接口是由三部分組成的,Controller單元、PHY單元及一些相關接口。其中主要的便是Controller單元、PHY單元

2019-06-13 05:00:06

。在結構上的改進主要包括可變寬度的存儲器接口、更快速的指令周期時間、可設置優先級的雙通道DMA處理器、靈活的引導程序裝入方式、可重新定位的中斷向量表以及可選的邊緣/電平觸發中斷方式等。 1

2019-06-14 05:00:08

FIFO。圖3所示是將緊耦合數據存儲器中的數據寫人FIFO的時序驗證。4 SRAM的接口設計本設計中的SRAM采用的是ISSI公司的IS61LV25616AL-10TL型16位高速異步SRAM,它屬于

2018-12-07 10:27:46

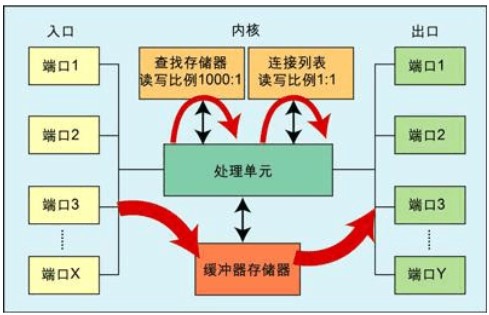

I/FFPGA。在串行接口和并行接口之間的是流量管理器IP解決方案,它負責對傳入和傳出的信息流執行服務質量(QoS)相關功能。存儲器控制器負責控制主要用作數據包緩沖器的外部存儲器。這種結構的優越性包括

2019-04-12 07:00:11

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

本文提出了一個網絡存儲器的基本解決方案,實現了網絡存儲器的基本功能。

2021-04-26 06:50:19

AHB接口的作用有哪些?什么是FSMC的地址映射呢?如何使用FSMC外接存儲器呢?

2021-12-15 07:32:27

本文介紹了使用XCR3032實現K9K1G08U0M與微控制器的接口原理,給出了VerilogHD L實現程序。對大容量FLASH存儲器的接口設計具有一定的參考價值。

2021-04-29 06:34:20

如何利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口?

2021-05-06 07:23:59

Flash類型與技術特點有哪些?如何去選擇uClinux的塊驅動器?如何去設計Flash存儲器?

2021-04-27 06:20:01

本文介紹了一種0.13微米CMOS T藝下FPGA中嵌入式存儲器模塊的設計與實現。

2021-04-09 06:02:09

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

如何用低成本FPGA解決高速存儲器接口挑戰?

2021-04-29 06:59:22

富士通半導體(上海)有限公司供稿鐵電隨機存儲器(FRAM) RFID由于存儲容量大、擦寫速度快一直被用作數據載體標簽。內置的串行接口可將傳感器與RFID連接在一起,從而豐富了RFID應用。

2019-07-26 07:31:26

電存儲器FRAM,則可很好地解決成本問題,同時又可得到更高的數據存儲可靠性。鐵電存儲器是RAMTRON公司的專利產品,該產品的核心技術是鐵電晶體材料,這一特殊材料使得鐵電存儲器產品同時擁有隨機存儲器

2019-04-28 09:57:17

請問怎么利用FPGA實現模式可變的衛星數據存儲器糾錯系統?

2021-04-13 06:10:54

TPMS技術及輪胎定位原理是什么?如何解決TPMS輪胎換位和調換輪胎時的重新定位問題?怎么實現外置編碼存儲器輪胎定位技術?

2021-05-14 06:13:50

如何滿足各種讀取數據捕捉需求以實現高速接口?怎么縮短高端存儲器接口設計?

2021-04-29 07:00:08

數據存儲器 FLASH程序存儲器 FLASH數據存儲器 片內RAM數據存儲器16M字節外部數據存儲器各有什么區別?特點?小弟看到這段 很暈。ADuC812的用戶數據存儲器包含三部分,片內640字節的FLASH數據存儲器、256字節的RAM以及片外可擴展到16M字節的數據存儲器。求助高手。解釋一下不同。

2011-11-29 09:50:46

切換期間存儲信息。非易失性存儲器用于存儲可執行代碼或常量數據、校準數據、安全性能和防護安全相關信息等重要數據,以作將來檢索用途。目前市場上主要包含這幾種不同類型的非易失性存儲器,如NOR 閃存

2019-07-23 06:15:10

目前高級應用要求新的存儲器技術能力出現。隨著電子系統需要更多的代碼和數據,所導致的結果就是對存儲器的需求永不停歇。相變存儲器(PCM)以創新的關鍵技術特色滿足了目前電子系統的需要。針對電子系統的重點

2018-05-17 09:45:35

簡易串行存儲器拷貝器相關資料下載

2021-05-14 07:59:03

虛擬地址物理地址等眾多地址及MMU相關知識先聊聊存儲器STM32單片機存儲器關于編譯器生成的文件數據在存儲器上的存儲結構物理地址、虛擬地址、線性地址和邏輯地址物理地址虛擬地址邏輯地址線性地址這些地址

2022-02-11 07:51:30

Linux將虛擬存儲器高端的1/4留給內核,剩下3/4全留給用戶進程。虛擬存儲器上中的程序主要由以下幾個重要組成部分:

2019-08-07 07:00:01

本文分別介紹了存儲器的分類、組成、層次結構、常見存儲器及存儲器的選擇,最后描述了計算機存儲器的一些新技術。存儲器是計算機系統中的記憶設備,用來存放程序和數據。計算機中全部信息,包括輸入的原始數據

2021-09-09 07:47:39

計算機硬件能直接執行哪種語言?計算機的存儲器采用分級存儲體系的目的是什么?常用的虛擬存儲器由哪兩級存儲器組成?

2021-09-17 06:44:39

FLASH+SRAM+EEPROM 實現有困難,或功耗,速度,成本三者難以協調的應用。本文介紹的多功能雙接口存儲器方案,除了實現低功耗快速存儲的功能外,還包括RTC,硬件看門狗,AES 數據加/解密,接口擴展等功能。2

2019-06-12 05:00:08

請問一下與EEPROM存儲器相關的寄存器有哪些?分別有什么作用?

2021-07-08 06:55:19

如何滿足各種讀取數據捕捉需求以實現高速接口?如何讓接收到的時鐘與數據中心對準?為了縮短設計周期應遵循哪些規則?如何設計存儲器接口才能獲得更高性能?

2021-04-14 06:30:23

網絡存儲器技術是如何產生的?怎樣去設計一種網絡存儲器?

2021-05-26 07:00:22

于兩電極之間,使用金屬互連并鈍化后完成鐵電制造過程。Ramtron公司的鐵電存儲器技術到現在已經相當的成熟。最初的鐵電存儲器采用兩晶體管/兩電容器(2T/2C)的結構,導致元件體積相對過大。最近隨著鐵

2011-11-19 11:53:09

于兩電極之間,使用金屬互連并鈍化后完成鐵電制造過程。Ramtron公司的鐵電存儲器技術到現在已經相當的成熟。最初的鐵電存儲器采用兩晶體管/兩電容器(2T/2C)的結構,導致元件體積相對過大。最近隨著鐵

2011-11-21 10:49:57

給出了由(2,1,N)系列卷積碼Viterbi 譯碼中路徑度量存儲器及其接口的使用FPGA實現時的設計方法,譯碼器采用四個ACS 并行運算的方式,狀態度量的更新采用乒乓模式,闡述了存

2009-09-08 14:49:05 9

9 本文設計了一種基于0.13 微米CMOS 工藝的FPGA 芯片中的嵌入式存儲器模塊。該容量為18Kb 的同步雙端口存儲模塊,可以配置成為只讀存儲器或靜態隨機存儲器,每個端口有6 種數據寬

2009-12-19 16:19:50 24

24 利用Virtex-5 FPGA迎接存儲器接口設計挑戰:在不支持新的接口協議時,存儲器接口設計師總是試圖支持越來越快的接口總線速度。目前,源同步雙數據速率 (DDR)存儲器件,例如 DDR2 SDRAM

2010-04-25 10:28:16 57

57 便攜存儲器的接口 接口類型是指該便攜存儲產品所采用的與電腦系統相連接的接口規格。目前的便攜存儲產品基

2010-01-09 14:51:08 1277

1277 本文介紹了FPGA外部存儲器的設計方法,可以有效地解決雷達實時信號處理過程中海量數據的存儲問題,同時也可以充分利用FPGA去控制SDRAM和FLASH,不僅保證了資源的充分利用,也可以

2011-08-18 11:46:45 7309

7309

山東省濟南華芯半導體公司旗下首條高端(FBGA)存儲器集成電路封裝測試生產線日前在下線,這將改變中國大容量存儲器芯片長期依賴國外的局面

2011-12-28 09:17:29 1290

1290 高速SDRAM存儲器接口電路設計(Altera FPGA開發板)如下圖所示:

2012-08-15 14:33:41 3326

3326

FLASH存儲器接口電路圖(Altera FPGA開發板)

2012-08-15 14:36:31 6269

6269

異步SRAM存儲器接口電路設計(Altera FPGA開發板)如圖所示:

2012-08-15 14:37:05 3862

3862

使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 FPGA 設計人員在滿足關鍵時序余量的同時力爭實現更高性能,在這種情況下,存儲器接口的設計是一個一向構成艱難而耗時的挑戰。Xilinx FPGA 提供 I/O 模塊和邏輯資源,從而使接口設計變

2013-03-14 15:16:07 71

71 Xilinx FPGA工程例子源碼:Xilinx DDR2存儲器接口調試代碼

2016-06-07 14:54:57 27

27 基于FPGA的高速固態存儲器優化設計_楊玉華

2017-01-13 21:40:36 1

1 接口,無所不包。 性能要求和 Xilinx 解決方案 20 世紀 90 年代后期,存儲器接口從單倍數據速率 SDRAM 發展為雙

2017-11-24 16:21:46 876

876 許多 FPGA 設計都采用高速存儲器接口,可能調試比較困難,不過只要采用正確的方法就能成功進行調試。 現代 FPGA 通常連接高速 SRAM 和 SDRAM 存儲器 。要確保這種器件無差錯運行,調試

2018-01-12 11:48:44 1031

1031

賽靈思公司(Xilinx)宣布,采用HBM和CCIX技術的新型16nm Virtex UltraScale+ FPGA的細節。該支持HBM的FPGA系列,擁有最高存儲器帶寬,相比DDR4 DIMM

2018-07-31 09:00:00 2545

2545 目前存儲器接口經常要求時鐘速度超過200MHz以滿足線卡和交換卡的吞吐量要求,這是FPGA架構的主要挑戰。PLL是基本的允許控制時鐘數據關系的部件。

2019-06-11 08:04:00 6512

6512

觀看業界首款采用XilinxVirtex?-7 FPGA的12.5 Gb / s混合存儲器立方體(HMC)接口演示。

2018-11-29 06:46:00 2786

2786 了解如何使用Vivado存儲器接口生成器(MIG)創建UltraScale存儲器接口設計。

本視頻將向您展示如何為UltraScale器件配置MIG IP內核,包括MIG IP I / O的I / O Bank規劃。

2018-11-22 07:13:00 2633

2633 大多數存儲器接口都是源同步接口,從外部存儲器器件傳出的數據和時鐘/ 選通脈沖是邊沿對齊的。在 Virtex-4 器件采集這一數據,需要延遲時鐘/ 選通脈沖或數據。利用直接時鐘控制技術,數據經延遲

2020-04-11 09:55:08 743

743

串行接口存儲器廣泛應用于消費類、汽車、電信、醫療、工業和 PC 相關市場。串行存儲器主要用于存儲個人偏好數據和配置/設置數據,是當今使用的最為靈活的非易失性存儲器(Nonvolatile

2021-03-31 11:14:47 7

7 基于FPGA塊存儲器的多位反轉容錯

2021-06-19 14:16:57 19

19 FPGA各存儲器之間的關系(嵌入式開發工作怎么樣)-該文檔為FPGA各存儲器之間的關系總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 16:35:09 6

6 FPGA中嵌入式塊存儲器的設計(嵌入式開發平臺)-該文檔為FPGA中嵌入式塊存儲器的設計總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-08-04 10:14:40 6

6 采用領先FPGA供應商提供的硬件經過驗證的參考設計。用戶在自己的定制設計中,可把參考設計作為起點,從而節省寶貴的時間和資源

2023-10-27 16:47:57 157

157

正在加载...

電子發燒友App

電子發燒友App

評論