基于IEEE1149.4的測試方法研究

根據混合信號邊界掃描測試的工作機制,提出了符合1149.4標準的測試方法,并用本研究室開發的混合信號邊界掃描測試系統進行了測試驗證。

??? 關鍵詞:混合信號,邊界掃描,IEEE1149.4,測試方法

1 引 言

邊界掃描體系結構及測試訪問端口IEEE1149.1標準,對純數字電路來講,無疑是十分成功的。它雖主要是為了解決電路板互連測試(Interconnect Testing)而設計的〔1〕,亦可進一步延伸到IC(IntegratedCircuit)級、板級和系統級測試。由于IEEE1149.1被廣泛地接受和使用,所以,混合信號測試總線標準IEEE1149.4〔2〕必須與1149.1標準兼容(準確地說,1149.4應當是1149.1的超集)。它們的主要目的是支持互連測試、參數測試和功能測試。

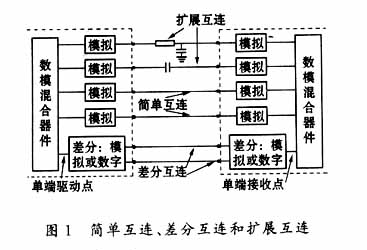

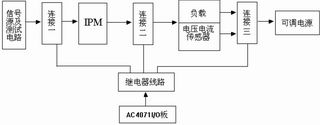

在如圖1所示的模擬/混合信號電路板上,IC間的互連可能是簡單的連線(IEEE1149.4將其定義為簡單互連測試),也有可能是無源元件組成的阻抗網絡(IEEE將其定義為擴展互連測試),甚至可能是有源網絡(但這種情況極少,一般都將有源元件集成到IC中了)。本文根據混合信號邊界掃描測試的工作機制,提出了符合1149.4標準的測試方法,并用本研究室開發的混合信號邊界掃描測試系統進行了測試驗證。

2 測試方法

邊界掃描技術支持多種測試操作,不同操作其測試機理有所不同,下面分別加以討論。

2.1 簡單互聯測試

互聯測試,可分為簡單互連、擴展互連和差分互連等。簡單互連測試是指對直接通過導線連接的管腳進行的互聯測試,主要用來測試器件連線間的開路、短路和網絡間的橋接等故障。進行測試時,先用SAMPLE/PRELOAD指令給輸出型的邊界掃描單元預置測試激勵。執行EXTEST指令之后,捕獲該連接線上輸入型邊界掃描單元的測試響應。然后通過比較激勵和響應來判斷、定位故障。

對于數字引腳的簡單互連測試,首先根據PCB(Printed Circuit Board)網表、器件BSDL(Boundary-Scan Description Language)等相關文檔資料選擇合適的互連測試算法,如等權值抗誤判算法和極小權值-極大相異算法,WALK“0”、WALK“1”等,生成互連測試矢量,用SAMPLE/PRELOAD指令將測試激勵施加給輸出型的邊界掃描單元,然后執行EXTEST指令進行互連測試。這樣,互連信號就被捕獲到與之相連的另一邊界掃描器件的相應的輸入型邊界掃描單元中。再通過掃描鏈將邊界掃描寄存器的內容移出則可得到測試響應。不過,必須通過一組測試矢量全集的測試,才能保證故障定位的正確。

在模擬引腳的簡單互聯測試中,為了使模擬管腳的簡單互連測試與數字管腳兼容,IEEE1149.4標準 在ABM(Analog Boundary Module)中增添了VH、VL、VTH三種不同的電平,分別代表高電平、低電平和門闕電平。在控制邏輯的控制下,將VH或VL電平施加到輸出型的模擬管腳上作為預置測試激勵(相當于數字管腳加入高電平或低電平激勵)。執行EXTEST指令之后,通過捕獲該連接線上的輸入型模擬管腳上的電壓,并與VTH門闕電平進行比較,將模擬量數字化為一位數字值“0”或“1”,作為輸入型模擬管腳上的測試響應,交邊界掃描鏈移出。這樣,就可將模擬電路的簡單互聯測試轉化為數字電路的互聯測試。通過對預置測試激勵和測試響應進行比較,就可以分析出該模擬簡單互連線是否發生了短路、斷路、橋接等故障,并且可將故障定位到管腳級。

這里有個問題值得注意,即簡單互連線發生橋接故障就相當于線與,而線與的結果與電路的具體實現方式有關,這在實例分析中可以看到。

2.2 差分測試

從邊界掃描技術角度來看,差分電路可分為數字差分電路和模擬差分電路。差分電路的測試有三種,即數字差分互連電路的測試、模擬差分電路的簡單互連測試和模擬差分電路的擴展互連測試等。對于數字差分互聯測試,顯然,只需將數字差分輸入或輸出的兩個DBM(DigitalBoundary Module)看成兩單獨的DBM,采用數字管腳簡單互連的測試方法即可。

對于模擬差分邊界掃描結構,在進行簡單互連測試時,標準規定其差分輸入端至少須有五種組態:即H-L(High Level-Low Level)、L-H、CD-CD(CoreDisconnect)、CD-G(Ground)和G-CD。所以,在進行差分簡單互連測試時,從差分輸出端所施加的測試激勵不能違反這些規定,除非你確知該測試對象還允許有其它組態。由于差分輸出的兩ABM具備施加VH或VL電平的能力(只是須注意,當一個腳加VH則另一個腳須加VL,或反之),另一端又可捕獲其數字化值,所以可按非差分ABM進行簡單的互連測試,只是激勵的施加稍有不同。

若模擬差分互連是擴展的差分互連,可以采用完全差分測試或非完全差分測試兩種方法。若被測對象只有AT1(Analog Test)和AT2兩根模擬測試線且帶有差分電路,則只能采用非完全差分測試。首先讓差分輸入的一端(如“+”端)連接AB1(Internal AnalogBus)、TBIC(Test Bus Interface Circuit)的S5,通過AT1腳輸入模擬測試激勵,差分輸入的另一端(如“-”端)則通過其ABM控制邏輯連其VH、VL或VG來提供模擬測試激勵。對差分輸出響應的獲取,先是讓差分輸出的一端經AB2、TBIC的S6、AT2輸出,再讓差分輸出的另一端經AB2、TBIC的S6、AT2輸出。然后再反過來,讓差分輸入“+”端接固定電平VH、VL或VG,讓差分輸入的“-”端通過AB1、TBIC的S5、AT1腳輸入原模擬測試激勵,同上面一樣測量兩次。施加兩次激勵及測量四次響應雖然麻煩一些,但IC器件的邊界掃描硬件電路可設計簡單些,從而節省器件成本。

進行完全差分測試,就需要被測試對象有專門的差分測試結構,即有一對差分測試激勵輸入管腳AT1和AT1N,一對差分測試響應捕獲管腳AT2和AT2N及相應的TBIC和內部總線結構。測試時,差分模擬測試激勵通過AT1和AT1N、TBIC、AB1和AB1N、差分輸入功能管腳的兩ABM的兩SB1加載到差分輸入上。其差分輸出響應經差分輸出功能管腳的兩ABM的兩SB2、AB2和AB2N、TBIC、AT2和AT2N輸出給外部測試響應處理器。

2.3 參數測試

參數測試是指管腳之間不是通過簡單的導線連接,而是通過由電阻、電容、電感或由它們組成的網絡而連接的一種互聯測試,即擴展互連測試,如圖1所示。擴展互連測試(即參數測試),由于模擬測試總線和I/O節點間的開關電阻,使得屏蔽測量方法不再適用。

2.3.1 簡單網絡參數測試

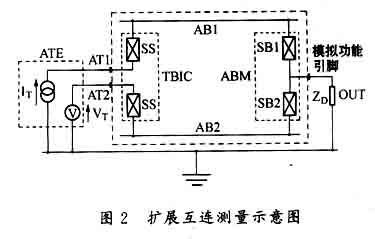

若擴展互連網絡是無源的,參數測試就是要測量出該無源網絡中R、L、C的元件值。ATE(AutomaticTest Equipment)通過ATAP(Analog Test AccessPort)管腳AT1,經TBIC的開關S5、ABM的SB1,就可將一個已知的模擬測試激勵電流IT施加到CUT(Circuit Under Test)上,然后可通過ABM的SB2、TBIC的開關S6、ATAP的管腳AT2,將CUT上的響應電壓由ATE測出,記為VT,如圖2所示。

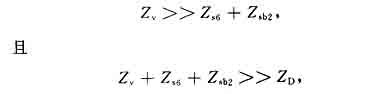

若

則VT就可近似等于CUT的端電壓。注:Zv為ATE中電壓測試系統的阻抗,Zs6為開關S6的阻抗,Zsb2為開關SB2的阻抗,ZD為CUT的阻抗。

若ZD是單個電阻、電感或電容,那么只需已知模擬激勵電流信號的頻率和幅度就可計算出其元件值。若ZD跨接在兩模擬功能管腳之間,它的測量分兩步進行。首先,通過對TBIC和ABM的控制,讓激勵電流信號通過AT1施加到指定F1上,通過AT2腳獲取該F1端的電位。再改變對TBIC和ABM的控制,讓激勵電流信號通過AT1施加到指定ABM上,通過AT2腳獲取該F2端的電位。最后,計算出ZD上的電壓降,結合已知激勵電流信號的頻率和幅度值就可計算出其元件值。若ZD是由多個電阻、電感或電容組成的單端口網絡,那么只需通過施加一組不同頻率的激勵電流,然后測試量對應頻率ZD上的電壓降就可得到一方程組,解此方程組即可求出各元件值。

2.3.2 Delta網絡的參數測試

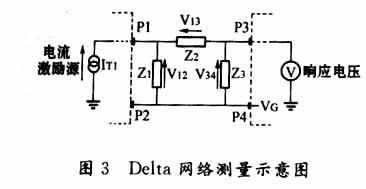

對于Delta互連網絡,如圖3所示,可以采用下面的方法進行測量。

(1)P4腳接VG,P3和P2腳斷開。AT1激勵I1施加到P1腳,通過AT2測量P1腳的電位VP11;

(2)P4腳接VG,P3腳斷開。AT1激勵I1施加到P1腳,通過AT2測量P2腳的電位VP21;

(3)P4腳接VG,P2腳斷開。AT1激勵I1施加到P1腳,通過AT2測量P3腳的電位VP31;

(4)P4腳接VG,P2腳斷開。AT1激勵I1施加到P3腳,通過AT2測量P1腳的電位VP12;

(5)P4腳接VG,P1腳斷開。AT1激勵I1施加到P3腳,通過AT2測量P2腳的電位VP22;

(6)P4腳接VG,P2和P1腳斷開。AT1激勵I1施加到P3腳,通過AT2測量P3腳的電位VP32。

由這些數據足夠解出Z1、Z2、Z3的值〔3〕。當然,若Z1、Z2和Z3又是一無源RLC網絡,通過改變I1的頻率再重復上面的六步測量,總可以計算出和RLC元件的值,對于同種性質的元件(如同為R或L或C)的串并聯,本測試理論只能將其作一個元件來進行測量。

2.3.3 復雜網絡

對于較復雜的電路,可以從電路拓撲的角度來考慮其測試。具體來說有兩種方法。

(1)通過對ABM開關矩陣的控制,可以將其簡化成圖2或圖3的情形。然后按照相應的測試方法分別進行測量。

??? (2)單端口網絡測量法。

對于任一無源單端口網絡(若是多端口網絡,可以通過對相關的ABM開關矩陣進行控制,將其轉換成單端口網絡),由網表文件可以得其拓撲結構、等效支路元件的個數N(等效支路元件的定義:相同性質的兩元件串聯或并聯將被看成一個元件,即等效支路元件),通過在兩端口間施加某一頻率的電流激勵源,再分別測量其兩端電壓,就可以得到該頻率的等效阻抗,從而得一個非線性方程。如在兩端口間施加Q(為了盡量減少測試和解非線性方程組所產生誤差,一般要求Q>N)個頻率不同的電流激勵源,就可以得到Q個非線性方程組。解該非線性方程組就可得這N個等效支路元件的元件值。

以上問題的實質是,由電路網表得到傳輸導納的非線性模型,經施加不少于Q組(不同頻率)的電流激勵,分別測量其端電壓響應。根據此數據表(即激勵響應表)來確定模型中的各參數(即支路導納值),以保證傳輸導納的非線性模型“最佳”擬合這Q組電壓電流數據表。由此看來,這實質是一個非線性的模型擬合問題,即非線性最小二乘問題〔4〕。

雖然計算復雜度有所提高,但這種方法可測出復雜無源網絡的各分立等效支路元件的參數值,且由于該系統使用計算機,因此處理這些數據是不困難的。雖然當互連網絡太大時,這種方法的計算復雜度呈指數增長,但DOT4測試對象是數模混合IC及由其構成的PCB。既然是數模混合IC,留在芯片外的就是用來完成用戶特定功能的、或是校準用的、或是難于集成的。難于集成的元件隨著集成技術的提高,總可以解決,完成用戶特定功能的和校準用的元器件其網絡拓撲結構一般比較簡單,這種方法完全可以勝任。

這里討論的參數測試理論方法還可延伸到非線性無源元件的測量。

邊界掃描支持的測試還有CLUSTER測試、器件錯誤裝配測試、整個掃描鏈本身結構的基礎測試器件功能測試、BIST(Built-In-SelfTest)測試、INTEST測試等。限于篇幅,此處不再作具體討論。

3 實例分析

3.1 簡單互連測試結果

因目前還沒有符合DOT4的器件成品,所以使用了DOT4工作組用于混合信號邊界掃描測試的專用實驗芯片KLIC〔5〕。KLIC實際上是個Mixed-SignalScan I/O。測試對象DEMO板設計原理是在Mixed-Signal Core電路的基礎上插入邊界掃描結構即KLIC,使其構成混合信號邊界掃描CUT。

DEMO板掃描鏈中兩個邊界掃描器件之間直接的互連線有3條,分別從IC1的輸出腳DBM、ABM2、ABM3連接到IC2的輸入腳DBM、ABM2、ABM3。由KLIC的邊界掃描內部結構可知,其在掃描鏈上的互連測試矢量排列如下(其中,“X”為無關量,“V”對應表1中的測試矢量欄,“R”對應響應數據欄):

XVV XXXXXXXXXXXX XXXX XXX XXXVVXXVVXXXXXXXXXXXXXX

與之相仿,掃描測試結果在掃描鏈上的表示為:

XXR XXXXXXXXXXXX XXXX XXX XXXXXRXXXRXXXXXXXXXXXXX

這里我們仿照WALK-1、WALK-0的全集測試矢量方法,測試時,通過故障模擬開關進行了故障設置,并且通過響應測試碼得到了測試報告和測試分析。把DBM與ABM2橋接,本測試系統的測試結果如表1所示。

??? 在這里,有個問題值得注意,數字邏輯“1”與模擬VL電平進行線與操作得到的結果是數字化值“1”,與數字邏輯“1”線與數字邏輯“0”的結果為數字邏輯“0”不同,這主要與器件的實現結構以及其VH、VT和VL三種電青壯年 值及其一茁壯成長SH、SL的結構有關。與美國Corelis公司的Scan Plus數字邊界掃描系統進行了對比測試,所測結果完全一樣。

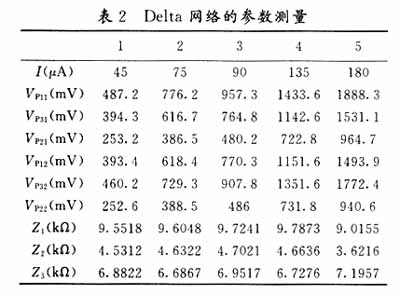

3.2 擴展互連測試

對圖3所示的Delta網絡,用本教研室的混合信號邊界掃描測試系統測得的數據如表2所示。其中,Z1為電阻,其真實值為9.734 kΩ,測量平均值為9.5367kΩ,絕對誤差為-0.1973 kΩ,相對誤差為-2.03%。Z2為電阻,其真實值為4.7 kΩ,測量平均值為4.43 kΩ,絕對誤差為-0.27 kΩ,相對誤差為5.7%。Z3為電阻,其真實值為6.85 kΩ,測量平均值為6.8888 kΩ,絕對誤差為-0.038 kΩ,相對誤差為0.56%。這里的較大誤差是由于程控信號源和數據采集板做得不完善造成的,只要將兩者加以完善,就可以達到IEEE1149.4標準規定的要求。

4 結束語

本文提出了符合1149.4標準的測試方法,并用本研究室開發的混合信號邊界掃描測試系統進行了測試驗證。測試結果表明,不但能測量互連元器件是否存在,而且還可測量其元件值(電阻、電容、電感),當然還可擴充到非線性元件。

混合信號測試總線是測試數字和模擬信號的起點,但不是解決問題的全部方案。對于小電抗的分立元件,或者高頻IC,其測量就較困難。

1 IEEE std 1149.1-2001.IEEE Standard Test Access Portand Boundary-Scan Architecture.IEEE Standards Board,New York,2001

2 IEEE std 1149.4-1999.IEEE Standard for a Mixed-SignalTest Bus.IEEE Standards Board,New York,19993 K P Parker,JE Mcdermid,S Oresjo.Structure andMetrology for an Analog Testability Bus.Proc.,ITC,1993:309~322

4 謝如彪,姜培慶編著.非線性數值分析.上海:上海交通大學出版社,1984

5 http://grouper.ieee.org/1149/4/kllp.html.KLIC.JTAG Analog Extension Test Chip.IEEE P1149.4Working Group

電子發燒友App

電子發燒友App

評論