隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。在過去幾年中已經看到有內置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價格昂貴。

2015-02-02 17:32:52 2204

2204

最近準備采用Xilinx FPGA進行多機通信,即主FPGA芯片將采集到的不同層的圖像數據流分別輸出給對應的4塊從FPGA芯片中,主從FPGA之間的連接機制采用星形拓撲結構。經計算,圖像數據流接口速率需要數百兆比特/秒,因此需要調研FPGA支持的常見IO接口標準,及每種接口的應用場合。

2022-10-17 09:14:18 1626

1626 比特流是一個常用詞匯,用于描述包含FPGA完整內部配置狀態的文件,包括布線、邏輯資源和IO設置。大多數現代FPGA都是基于SRAM的,包括Xilinx Spartan 和Virtex 系列

2022-11-30 10:59:17 733

733 24合1視頻橋接芯片RK628D有哪些優勢呢?24合1視頻橋接芯片RK628D有哪些應用呢?

2022-03-02 09:40:31

6678的pcie和fpga的pcie? TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

?

2018-06-21 15:49:12

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-10-23 07:16:35

更快、更大,每比特的功耗也更低,但是如何實現FPGA和DDR3 SDRAM DIMM條的接口設計呢? 關鍵字:均衡(leveling)如果FPGA I/O結構中沒有包含均衡功能,那么它與DDR3

2019-04-22 07:00:08

大家好,FPGA在媒體流處理方面有哪些優勢,有哪些成熟案例,謝謝!

2009-02-09 20:19:28

,FPGA必須提供符合成本效益的非常小的外形尺寸,以適應現代攝像機對于緊湊外形的要求。 具有完備子LVDS文檔支持的LatticeXP2非易失FPGA系列已被證實解決了圖像傳感器橋接的電氣需求。集成

2011-05-24 14:17:00

對更高密度和更快速度配置存儲器的需求。現代FPGA在配置期間需要加載多達128MB的數據。這些高密度配置比特流需要更長的時間才能從NOR閃存器件傳輸到FPGA。配置接口不僅針對讀取吞吐量進行了優化,還

2021-09-03 07:00:00

嗨,大家好,只是一個簡單的問題。 FPGA編輯器是否有限制為包含嵌入式處理器(如PowerPC)的設計生成比特流?我問的原因是因為我在Project Navigator中創建了一個設計并運行了PAR

2018-10-18 14:44:29

顧名思義,橋接T衰減器具有一個額外的電阻元件,該電阻在標準T焊盤的兩個串聯電阻之間形成了橋接網絡。這種附加的電阻性元件使電路能夠通過所需的衰減來降低信號電平,而無需改變電路的特性阻抗,因為信號似乎

2020-11-18 09:30:08

這幾年有點背,逐漸遠離主流話題,所以有人就有了這樣的問題:DSP會被FPGA取代嗎?小編總結了各個網友的回答: 網友一:獨立的DSP不會被FPGA替代,但是會被增強了信號處理功能的ARM處理器替代

2021-07-16 08:12:03

領域。本文基于雷達實時信號處理的需要,用FPGA實現了多DSP信號處理模板局部總線和基于標準VME總線的計算機進行通信的接口設計。 2 VME總線的功能特點VME總線系統的功能結構可以分為4類:數據傳輸

2019-04-22 07:00:07

問一下你們A40i硬件手冊上核心板的mipi管腳GPIO跟電壓都劃了橫線,是沒有接出來嗎?你們自己的mipi屏幕是接mipi dsi接口還是接lcd的接口的,我看到硬件手冊里面標明Mipi接口寫了TBD,但是你們自己又又mipi屏幕,是怎么回事?

2022-01-05 06:53:42

咨詢一個初級A/D問題:AD9684中DCO時鐘的用法(FPGA控制)。AD9684與FPGA用LVDS模式接口互聯時,FPGA端如何使用?手冊中沒有詳細說明,是DCO上升沿捕獲數據,作為數據同步

2023-12-13 09:01:52

[2018-08-26]-[CentOS]CentOS靜態IP配置(橋接模式)

2020-05-12 08:27:02

在DisplayPort之前,數字多媒體接口標準經歷了多次紛爭,逐漸形成了外部連接(Box-to-Box)與內部連接(Chip-to-Chip)兩塊相互獨立的陣地。在外部連接方面,PC已有DVI;而

2019-04-09 07:00:08

在過去的幾十年的硬件設計里,這個詞對國人來說非常陌生,特別是我們50HZ、60HZ系統。何謂橋接?維基百科中的解釋是關于通訊網絡協議的。橋接是指連接兩個不同系統之間的橋梁,英文簡稱“bridged

2022-02-20 07:00:00

哪位大俠實現過用FPGA實現GPIB接口的 麻煩給小弟些指導,我用的SPARTN2的XILINX的芯片

2013-11-21 17:04:08

LVDS的多媒體特性是什么?LVDS多媒體接口在汽車電子領域的應用前景如何?

2021-05-12 06:51:50

IEEE 802.3 規范提出媒體無關接口(Media Independent Interface,MII)就是為了能夠實現 MAC 層和不同的物理層(PHY)之間的邏輯連接,如圖 10-5 所示

2018-12-27 11:23:20

信息:下載使用24 VAC電源的UART至Wi-Fi橋接 (TIDA-00375) 參考設計,獲得設計指南、電路原理圖、測試數據、設計文件、物料清單等。對于使用RS-485接口的設計,請參見針對24

2019-08-06 04:45:01

富士通微電子(上海)有限公司日前宣布推出業界領先的USB 3.0 - SATA (*1) 橋接(*2)芯片。該芯片支持超速USB和USB 3.0規范(*3),并能在外置存儲器件(如磁盤驅動器HDD)和PC之間進行高達5Gbps的數據傳輸。

2019-08-26 08:28:21

TUSB9261 -- USB3.0轉SATA接口橋接芯片 燒錄指南

2021-01-07 06:26:20

我用的wifi安裝14.04的ubuntu,用橋接可以無線上網。想用橋接有線上網,但是找不到可以橋接到有線網卡的選項。希望大家幫幫,謝謝。

2016-10-13 22:08:48

描述橋接 T 鼓合成器振蕩器這是一個雙橋接 T 振蕩器,可用于使用外部觸發器創建模擬鼓和其他打擊樂合成器聲音。當用脈沖觸發時,輸出將產生一個消散的瞬時正弦波振蕩,通過調整每個振蕩器上的電位器,可以將音高調整為聽起來像低音鼓、木塊等。PCB

2022-07-26 07:56:32

大家好,我在設計中使用了Artix 7。更確切地說,我使用的是XC7A35T-2FTG256I,但是我的資源不足。我想用aXC7A75T-2FTG256I替換它。我有兩個問題:1)它是否真的是替代品,我已檢查數據表,它似乎是。2)如果我用兩個FPGA編譯完全相同的代碼,結果比特流會不同?謝謝,保羅

2020-08-17 06:15:11

低功耗FPGA的開發板,以及LatticeXP公司的高級開發板(見圖2)等。 QuickLogic MAB售價999美元,可以連接到英特爾PXA27x處理器開發套件。這款MAB基于QuickLogic

2012-04-27 14:40:21

嗨,我正在嘗試部分自我重新配置。想法是通過介質將部分比特流發送到FPGA。FPGA接收它(在多個塊中)并將比特流寫入ICAP。當連接發生時,我的FPGA的行為會發生什么發送部分比特流中途消失了?我

2019-02-14 09:40:06

為什么會出現eth3沒有eth0的?我用橋接方式為什么都ping不通用NAT方式 就可以ping通但虛擬機還是和開發板PING不通。

2019-10-24 03:28:16

二三層橋接為何是LTE承載的關鍵技術?

2021-05-24 07:17:37

(Automated Imaging AsSoCiaTIon)開發的相機接口標準。這是一項開放性的標準,它能讓來自不同廠家的攝像機與應用軟件通過吉比特以太網實現相互間的無間合作。Gige Vision

2019-05-05 08:30:00

案例中,這樣的平臺需要進行一定的調整以滿足汽車制造商的需求。而使用FPGA可以快速實現低成本橋接解決方案,使得現有平臺能夠完美應用于汽車領域。

2019-07-23 07:57:39

MAX9286吉比特多媒體串行鏈路(GMSL)解串器接收多達四個GMSL串行器的數據,采用50Ω同軸電纜或100Ω屏蔽雙絞線(STP)電纜,通過四個CSI-2通道輸出數據。每條串行鏈路具有嵌入式控制

2018-02-02 15:10:14

VMware使用橋接模式,已經手動設置ip地址和主機ip同一網段,但是ifconfig顯示的ip地址卻和vmnet8(NAT)同一網段?怎么解決?

2014-10-16 15:06:02

的處理器,優化了性能和成本通過不同的電壓和各種接口,如SPI、I2C、SDIO、PCI和LPC之間的橋接,最大化組件選擇的靈活性萊迪思FPGALCMXO2-640HC-4TG100C可編程邏輯器件FPGA

2019-09-20 15:13:30

本文介紹了一種基于 FPGA 技術的IDE 硬盤接口的設計。該卡提供兩個符合ATA-6 規范的接口,采用FPGA 實現了兩套IDE 接口功能,設計支持PIO和Ultra DMA 傳輸模式,文章側重于介紹用FPGA 實現IDE 接口協議的具體方法。

2011-01-12 14:38:42

`1 背景知識像素是由比特組成的數字。例如,在256級灰度圖像中,每個像素的灰度是由8比特(也就是1個字節)組成。一幅8比特圖像可以認為由8個1比特平面組成,如圖1所示,其中平面1包含圖像中所有像素

2018-08-14 09:07:22

Imaging的HiSPi串行接口至TI DSP并行接口的橋接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解決方案,如圖4所示。該參考設計在輸入端用HiSPi串行接口,在輸出端用TI

2019-06-04 05:00:19

Imaging的HiSPi串行接口至TI DSP并行接口的橋接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解決方案,如圖4所示。該參考設計在輸入端用HiSPi串行接口,在輸出端用TI

2019-06-06 05:00:37

TI DSP并行接口的橋接,LatticeXP2-5非易失性FPGA提供了高效、具有成本效益的解決方案,如圖4所示。圖4 基于FPGA的串行傳感器橋接參考設計示例 該參考設計在輸入端用HiSPi串行

2018-11-05 11:08:31

是一種由AIA(Automated Imaging AsSoCiation)開發的相機接口標準。這是一項開放性的標準,它能讓來自不同廠家的攝像機與應用軟件通過吉比特以太網實現相互間的無間合作。Gige

2013-09-04 12:14:55

移動應用程序設計的圖像傳感器,則需要轉換橋接邏輯。例如,針對嵌入式或數字靜態相機市場的圖像傳感器通常具有子LVDS或不是CSI-2(相機串行接口)的其他專有接口。與CSI-2發送參考設計并行,使設計人

2020-05-01 11:56:40

、100Mb/s和1Gb/s三種不同速度的以太網協議接口控制。本文將主要討論如何使用這兩個TSEC實現吉比特以太網接口。吉比特以太網物理層協議及接口參考文獻上對于網絡協議的介紹往往局限于對協議分層的理論分析

2018-11-30 11:27:55

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

多媒體的FPGA實現PDF

2015-10-26 21:14:05

你好,請有人解釋我如何使用IMPACT在FPGA xilinx中下載比特流先謝謝你以上來自于谷歌翻譯以下為原文hello,please can someone explain me how

2019-01-15 10:08:59

大家好,我想使用USR_ACCESS_VIRTEX4原語來訪問存儲在配置閃存中的其他比特流。情況如下:我有一個主FPGA(Virtex-4FX)和一個從FPGA(Spartan-3A)。從屬FPGA

2020-05-29 10:14:55

如何利用FPGA實現低成本汽車多總線橋接?

2021-04-29 06:51:23

請問如何利用FPGA嵌入式實現多比特自相關器的設計?

2021-05-06 09:47:25

基礎的多路復用器/解復用器應用,現成的標準模擬開關可能就能滿足需求。 但隨著設計人員執行一些更加復雜的橋接任務,如轉換不兼容的接口、組合多個視頻流、或將視頻流拆分至多個接口,基于 FPGA 的可編程橋接

2017-04-06 13:48:17

如何采用RS232總線實現計算機和橋接卡之間的通訊?使用FPGA實現I2C總線時需要建立那幾個模塊?

2021-05-07 06:01:08

你好我有一個在MIcroBlaze上運行linux的設計要求。我能夠在我的Virtex-7 FPGA上下載比特流(在Vivado 2014.4中生成)。我使用Impact來編程我的FPGA。我因此

2020-04-02 10:05:40

我在使用EDK 10.1中的微填充處理器在FPGA中下載比特流文件時遇到問題。我只是將Microblaze processsor比特串文件下載到FPGA中(斯巴達3a dsp)...連接的要求是什么?我有JTAG和一個串口....什么是stepi必須遵循。

2020-03-30 10:07:31

對MOS管的驅動電路形式,常用推挽式電路,增強驅動能力而功率放大的電路形式,常使用全橋或者半橋的電路形式,放大功率同樣是要接外接供電電源,為什么驅動用推挽,功放用全橋半橋?如果交換電路形式呢?謝謝

2020-07-15 01:34:51

對MOS管的驅動電路形式,常用推挽式電路,增強驅動能力而功率放大的電路形式,常使用全橋或者半橋的電路形式,放大功率同樣是要接外接供電電源,為什么驅動用推挽,功放用全橋半橋?如果交換電路形式呢?謝謝

2017-02-16 14:02:13

的時候,一個全新的無線吉比特聯盟(Wireless Gigabit Alliance)悄然成立了,這一無線聯盟僅用不到一年的時間就完成了新千兆無線網絡標準的制定工作,并于2010年5月頒布了

2019-07-03 07:02:27

嗨專家, 我正在使用spartan-6 FPGA進行多重啟動實驗。我發現位文件位于ug380上,如下圖所示。黃金比特流位于閃存的下部塊上,多重引導比特流位于閃存的較高塊上。 因此,如果我想使用保護區

2020-06-09 17:43:26

求解整流橋接法,圖中的這種整流橋怎么接?

2016-10-24 16:40:18

瑞芯微發布24合1視頻橋接芯片RK628D RK628D支持三種輸入接口,九種輸出接口,僅一顆芯片即可實現多達24種視頻傳輸轉換接口的組合。RK628D可應用于六大場景包括多屏商顯、4K大屏轉接

2022-05-31 09:13:25

MIPI CSI-2接收橋參考設計。靈活的MIPI(移動行業處理器接口)CSI-2接收橋 - 允許移動CSI-2(攝像機串行接口)圖像傳感器連接到嵌入式圖像信號處理器ISP。經過測試,在HDR-60

2020-04-29 09:39:43

索尼Sub-LVDS到MIPI CSI-2傳感器橋參考設計。索尼圖像傳感器的橋接解決方案 - 它創建了一個參考設計,將串行Sub-LVDS接口與MIPI CSI-2連接起來,從而使設計人員能夠將

2020-04-30 06:13:19

方案,完成了十接口千兆線路接口卡的設計與實現,研制的千兆線路接口卡完全滿足了T比特路由器項目對十接口千兆線路接口卡設計的功能與性能要求。采用FPGA設計并實現了十接口千兆以太網線路接口卡設計與實現中

2019-04-29 07:00:07

?1.產品概述WK2124是SPITM接口的4通道UART器件,WK2124實現SPI橋接/擴展4個增強功能串口(UART)的功能。擴展的子通道的UART具備如下功能特點:每個子通道UART的波特率

2023-11-24 00:17:37

Altera Stratix IV FPGA繼續廣受全球媒體好評

Altera公司今天宣布,40-nm Stratix® IV FPGA系列最近榮獲電子編輯媒體的多個獎項。Stratix IV系列因其在密度、性能和功耗上的優

2010-02-24 09:44:20 1198

1198 MAX9249 吉比特多媒體串行鏈路串行器,具有LVDS系統接口

概述

MAX9249串行器帶有LVDS系統接口,采用Maxim吉比特多媒體串行鏈路(GMSL)技術。MAX9249串行器與GMSL解

2010-03-28 09:17:58 1067

1067 MAX9249 吉比特多媒體串行鏈路串行器,具有LVDS系統接口

概述

MAX9249串行器帶有LVDS系統接口,采用Maxim吉比特多媒體串行鏈路(GMSL)

2010-05-20 08:51:48 787

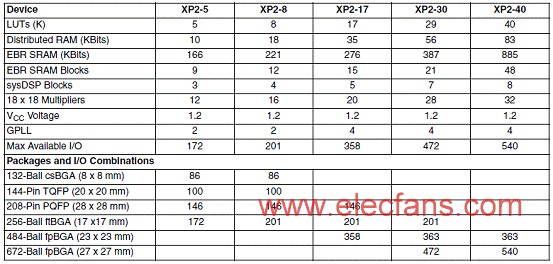

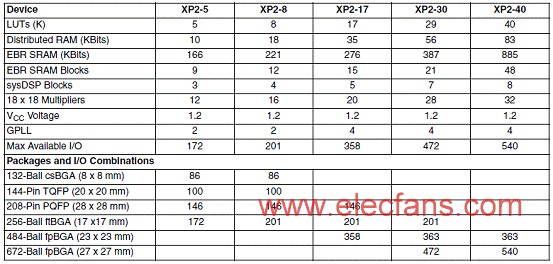

787 本文介紹了LatticeXP2系列主要特性,LatticeXP2-17器件簡化方框圖,LatticeXP2標準評估板主要特性和LatticeXP2標準評估板電路圖。

Lattice 公司的LatticeXP2器件包括基于查找表(LUT)的

2010-08-25 15:06:34 1279

1279

LatticeXP2器件將基于FPGA結構的查找表(LUT)與閃存非易失單元組合在一個被稱為flexiFLASH的架構中。 flexiFLASH方式提供了許多優點

2011-03-28 10:20:17 1354

1354 本文通過對該接口的分析,提出了解決該接口設計難點的方案。以上方案經過FPGA布線后仿真測試,證明是切實可行的。

2012-01-24 18:08:19 708

708 基于FPGA的SDI接口設計,學習FPGA的好資料!!!!

2016-06-06 10:00:46 29

29 Zynq開發板FPGA比特流文件可以通過三種途徑下載: 1. 利用SDK生成的FSBL.elf文件自動加載FPGA比特流配置文件,將比特流文件,FSBL.elf文件和u-boot.elf文件利用

2017-02-08 15:20:09 895

895 基于比特幣的媒體區塊鏈面臨著一個巨大的挑戰。傳統上,比特幣無法像一些區塊鏈開發者和用戶所希望的那樣進行無縫擴展。它在這方面的局限性引發了對比特幣媒體區塊鏈未來的質疑。這還增加了像以太坊這樣的替代區塊鏈在媒體市場上超越比特幣的可能性。在媒體區塊鏈公司在成長過程中,需要將擴展的因素放到他們的考慮計劃中。

2018-09-27 14:41:26 387

387 關鍵詞:Lattice , LVDS視頻接口 Lattice公司的LatticeECP2 7:1 LVDS視頻評估套件采用LatticeECP2 或LatticeXP2 FPGA

2019-03-20 12:50:01 956

956 在FPGA上設計了一種波特率連續可調的UART接口,該接口符合RS-232C通信協議。將波特率轉換為比特持續時間,在固定工作時鐘頻率下通過改變比特持續時間來實現波特率的連續可調,并將比特持續時間

2021-06-01 09:56:05 10

10 FPGA和外圍接口-基礎版

2023-05-22 10:57:24 568

568

? 串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2023-07-27 16:10:01 1565

1565

電子發燒友網站提供《使用加密保護7系列FPGA比特流.pdf》資料免費下載

2023-09-13 15:31:19 0

0

正在加载...

電子發燒友App

電子發燒友App

評論