摘要:IDT7132/IDT7142是一種高速2k×8雙端口靜態(tài)RAM,它擁有兩套完全獨立的數據、地址和讀寫控制線。文中分析了雙端口RAM(DPRAM)的設計方案。并以IDT7132/7142為例介紹了雙端口RAM的時序、競爭和并行通訊接口設計以及雷達仿真平臺中的應用。

??? 關鍵詞:微處理器 雙端口RAM IDT7132/7142

數據獲取及交換是多CPU系統(tǒng)的重要組成部分。在這類系統(tǒng)中,數據交換要求的通訊速率往往很高,平均速率一般在10k左右,有時甚至達100k以上。傳統(tǒng)的并行接口和串行接口設計無論在通信速率,還是在可靠性方面都不易滿足要求。而雙端口RAM則是一個較好的實現方案。它具有通訊速率高、接口設計簡單等特點,因而在設計中得到廣泛的應用。

1 常用雙端口RAM的結構特點

1.1 通用集成電路組成的雙端口

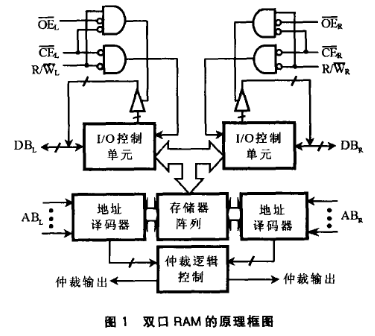

采用通用集成電路組成的雙端口RAM如圖1所示。一般的RAM只有一套地址總線、數據總線和讀寫控制線,因此,兩端CPU芯片的三總線必須經過緩沖隔離才能共享靜態(tài)RAM。具體工作過程是兩個CPU的地址信號和讀寫控制信號全中接入仲裁電路,由仲裁電路判斷訪問雙端口RAM的CPU,并使能相應的總線緩沖器。若兩個CPU在同一段時間內訪問共享的RAM的發(fā)生競爭,則由仲裁電路迫使后訪問的CPU處于等待狀態(tài),一旦前一個CPU訪問結束,再由仲裁電路打開緩沖器,以使后一個CPU接通RAM并進行訪問。

該電路的特點是成本低、簡單且存儲量大,其容量在64k~128k之間。缺點是在兩個CPU發(fā)生競爭時,有一方CPU必須等待,因而降低了訪問效率。

1.2 專用雙端口RAM芯片

目前市場上有多種專用雙端口RAM芯片,如IDT7132/7142、DS1609等。這些芯片有兩套完全獨立的數據線、地址線和讀寫控制線,因而可使兩個CPU分時獨立訪問其內部RAM資源。由于雙CPU同時訪問時的仲裁邏輯電路全部集成在雙端口RAM內部,因而需要用戶設計的電路比較簡單。雙端口RAM內一般都有一個總線搶占優(yōu)先級比較器,只要雙CPU不同時訪問同一存儲單元,那么較先送出地址的CPU將擁有該單元的本次訪問優(yōu)先權,而另一個CPU的地址與讀寫信號將被屏蔽掉,同時通過“busy”引腳告知該CPU以使之根據需要對該單元重新訪問或撤消訪問。

專用雙端口RAM的優(yōu)點是通訊速度快,實時性強,接口比較簡單,兩邊CPU都可主動進行數據傳輸;缺點是成本高,需要克服競爭現象。

以上兩種技術方案各有優(yōu)點,在要求存儲量較大時,一般采用通用集成電路組成的雙端口RAM;在通信實時性要求較高的而通信數據量不大時,一般采用專用雙端口RAM芯片。

在實際應用中,雙端口RAM與并行接口與串行接口相比,它不僅能利用其兩端口異步操作來讀寫數據,而且可用作多CPU微處理系統(tǒng)CPU的數據交換接口,從而簡化了對各CPU之間數據通信規(guī)約的要求,提高了系統(tǒng)數據通信處理的可靠性,同時提高了CPU之間數據交換的實響應速度。

2 IDT7132/7142簡介

2.1 IDT7132/7142結構與連接方式

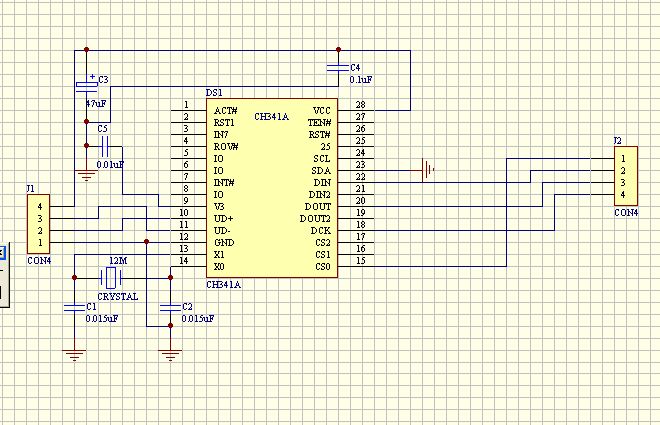

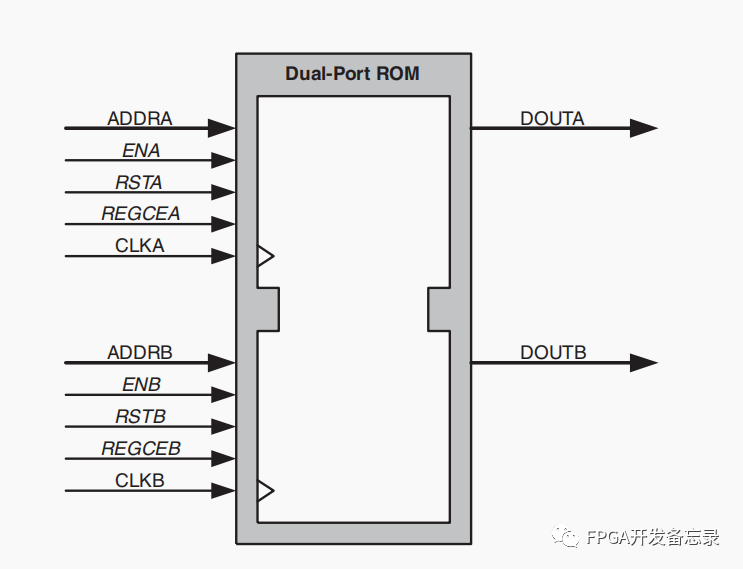

IDT7132/7142是高速2k×8雙端口靜態(tài)RAM,可提供兩個擁有獨立的控制總線、地址總線和I/O總線端口,允許CPU獨立訪問內部的任何存儲單元。當CE引腳出現下降沿時,選中DPRAM即可通過控制OE或R/W來訪問內部存儲單元。IDT32一般被用作8位雙端口RAM,也可以作為主片與DIT7142從片構成主從式16位雙端口RAM。連接方式如圖2所示:

2.2 IDT7132/7142時序圖

IDT7132/7142的時序如圖3所示,它與RAM的讀寫時序非常類似。當CPU選中DPRAM時,CE引腳出現下降沿,當控制紆OE為高且R/W為低時,CPU對內部存儲單元進行寫操作;而當控制線OE為低且R/W為高時,CPU對內部存儲單元進行讀操作。

2.3 競爭現象的處理

當外部CPU通過兩個端口對雙端口RAM內部的同一個存儲單元進行操作時,系統(tǒng)將出現競爭。這種競爭一般有如一兩種模式:

(1)如果兩個端口的總線訪問地址相同,并先于片選信號CE有鏟,則片內控制邏輯將在CEL與CER之間發(fā)生競爭。

(2)如果兩個端口的片選信號CE在地址信號有效之前變低,則片內控制邏輯將在地址信號到達時發(fā)生競爭。

為避免因競爭而導致的通訊失敗,設計者提出了各種解決方案。常見的有三種:

(1)設置標志位:在開辟數據通訊區(qū)的同時,可通過軟件方法在某個固定存儲單元設立標志位。這種方法要求兩端CPU每次訪問雙端口RAM之前,必須查詢、測試和設置標志位,然后再根據標志位的狀態(tài)決定是否可以訪問數據區(qū);有的雙端口RAM本身就個有專用的一個或多個硬件標志鎖存器和專門的測試和設置指令,可直接對標志位進行讀/寫操作。這種方法通常用在多個處理器共享一個存儲器塊時。為了保證通訊數據的完整性,在采用這種方法時往往要求每個處理器能對該存儲器塊進行互斥的存取。

(2)軟件查詢BUSY引腳狀態(tài):雙端口RAM必須具有解決兩個處理器同時訪問同一單元的競爭仲裁邏輯功能。當雙方址發(fā)生沖突時,競爭仲裁邏輯可用來決定哪個端口訪問有效,同時取消無效端口的訪問操作,并將禁止端口的Busy信號置為低電平。因此Busy信號可作為處理器等待邏輯的輸入之一,即當Busy為低電平時,讓處理器進入等待狀態(tài)。每次訪問雙端口RAM時,CPU檢查BUSY狀態(tài)以判斷是否發(fā)生競爭,只有BUSY為高時,對雙端口RAM的操作才有效。

(3)利用硬件解決競爭:將BUSY信號引入READY引腳可在發(fā)生競爭時使BUSY為低,從而使CPU內部總線時序根據READY引腳狀態(tài)自動插入WAIT信號并展寬總線,以達到分時訪問的目的。對于80C196KC和8098等MCS-96系列微處理器,利用這種方法便可通過硬件解決競爭問題。

另外,在使用BUSY信號時必須首先將此信號接上拉電阻,其次應在BUSY信號有效期間使處理器保持讀寫操作經及相應的地址和數據,但是需要說明的是:在BUSY信號變高之前,這種情況下的所有寫操作都是無效的,圖4所示發(fā)生競爭時的時序圖。

3 RAM在雷達仿真平臺中的應用

雷達仿真平臺是用于雷達操作手訓練的仿真設備。該平是一個由計算機、主控CPU(80C196KC)、手輪控制CPU(8098)等組成的多機系統(tǒng)。在主控CPU判斷目標是否進入雷達波瓣作用范圍時,必須將目標理想諸元與雷達的高低角和方位角做比較。在雷達仿真平臺中,雷達的高低角和方位角是通過對高低手輪和方位手輪的軸角轉換而獲得的。主控CPU每隔20ms就向手輪控制CPU發(fā)送一次模擬目標的高低角、方位角、距離以及目標屬性等多組數據(共200字節(jié)),同時接收手輪控制CPU的數據。為了加快通迅速度,簡化通訊,提高通信的實時性指標,系統(tǒng)要用了雙端口RAM(DPRAM)IDT7132/7142來進行CPU之間的數據交換。具體電路見圖5。

80C196KC和8098均有READY引腳,通過80C196KC和8098的時序可知,當READY引腳出現低電平時,CPU可自動插入WAIT等待周期,以延長讀寫和片選信號,因此,設計時將80C196KC和8098的READY引腳與IDT7132/7142的BUSY引腳相連就可在發(fā)生競爭時,自動使80C196KC或8098處于等待狀態(tài)。

??? 在資源分配方面,該設計還劃分了電視跟蹤數據區(qū)、雷達跟蹤數據區(qū)、手輪實測值數據區(qū)和命令狀態(tài)區(qū),并明確規(guī)定了各個通訊區(qū)的任務和性質,從而簡化了通訊程序,提高了通訊速度。

通過雷達仿真平臺控制系統(tǒng)的實時運行實驗證明:主控CPU與手輪控制CPU之間的數據交換速率很高、運行可靠,大大提高了系統(tǒng)的實時性能。目前,該系統(tǒng)已經通過了技術鑒定。

電子發(fā)燒友App

電子發(fā)燒友App

評論