ISPl362在基于FPGA的紅外成像系統(tǒng)中的應(yīng)用

摘要:ISPl362是飛利浦推出的一款USB可編程控制芯片,其內(nèi)部集成了一個高級主控制器,一個外設(shè)控制器,主機(jī)和設(shè)備控制器兼容USB 2.O協(xié)議,支持12 Mb/s的全速傳輸和1.5 Mb/s的低速傳輸;芯片有三種工作模式,即主機(jī)控制器模式、設(shè)備控制器模式和OTG模式。主要針對USB控制芯片ISPl362在基于FPGA的紅外成像系統(tǒng)的數(shù)據(jù)采集中的應(yīng)用,利用Verilog HDL語言完成其在設(shè)備控制器模式下的功能,具有很好的可移植性。

關(guān)鍵詞:FPGA;ISP1362;USB接口;固件;Verilog HDL

O 引言

??? 近年來,紅外熱成像系統(tǒng)已越來越多地應(yīng)用于軍事和工業(yè)上,因此對紅外圖像的研究也成為熱點(diǎn)話題。為適應(yīng)很多實(shí)時圖像處理方法的需求,圖像處理系統(tǒng)對圖像數(shù)據(jù)采集的速度及準(zhǔn)確性的要求也越來越高。而傳統(tǒng)的接口,如ISA接口、PCI接口、PS/2接口等都是非共享式接口,不但體積龐大,而且規(guī)格不一。USB接口克服了傳統(tǒng)接口的上述缺陷,具有高速、雙向、低成本以及兼容性好、通用性強(qiáng)等優(yōu)點(diǎn),已經(jīng)在IT各個領(lǐng)域得到了廣泛的應(yīng)用。與此同時,各種型號的USB接口控制芯片也應(yīng)運(yùn)而生。ISPl362芯片以其成本低、可靠性高、功耗低以及易于擴(kuò)展等優(yōu)點(diǎn),也受到了用戶的廣泛關(guān)注。ISPl362由主機(jī)控制器、設(shè)備控制器、OTG控制器、USB收發(fā)器、OTG收發(fā)器和寄存器等組成。其中,OTG控制器主要提供包括監(jiān)控和轉(zhuǎn)換功能在內(nèi)的所有OTG控制,在OTG模式下,既可用作主機(jī),又可用作外設(shè),并支持主機(jī)通信協(xié)議(Host Neg-otiayion Protocol,HNP)和對話請求協(xié)議(Ses-sion Request Protocol,SRP)。考慮到以后進(jìn)一步完善系統(tǒng)的需要,設(shè)計中選用此款芯片來完成USB接口的設(shè)計。該芯片內(nèi)部沒有集成MCU,設(shè)計中采用Altera的現(xiàn)場可編程門陣(Field-Programmabte Gate Arrav,F(xiàn)PGA)中的EP2C70-F672C6來控制芯片的正常運(yùn)行,操作簡單可靠。EP2C70F672C6具有低功耗、高密度以及低成本等優(yōu)點(diǎn),可提供4 608~68 416個邏輯單元,包括了多達(dá)150個嵌入式18×18位乘法器、專用外部存儲器接口電路,最高操作頻率可達(dá)到260 MHz。基于以上原因的考慮,選用此款FPGA芯片來實(shí)現(xiàn)紅外成像系統(tǒng)中的各項(xiàng)功能。

l 紅外成像系統(tǒng)

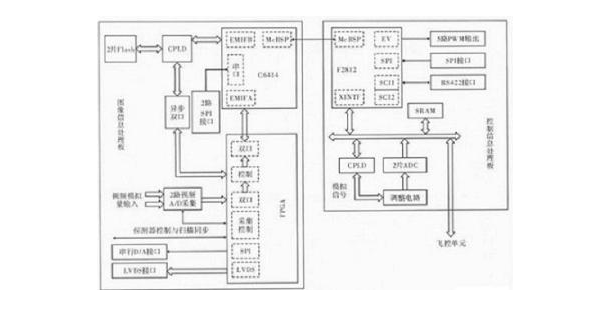

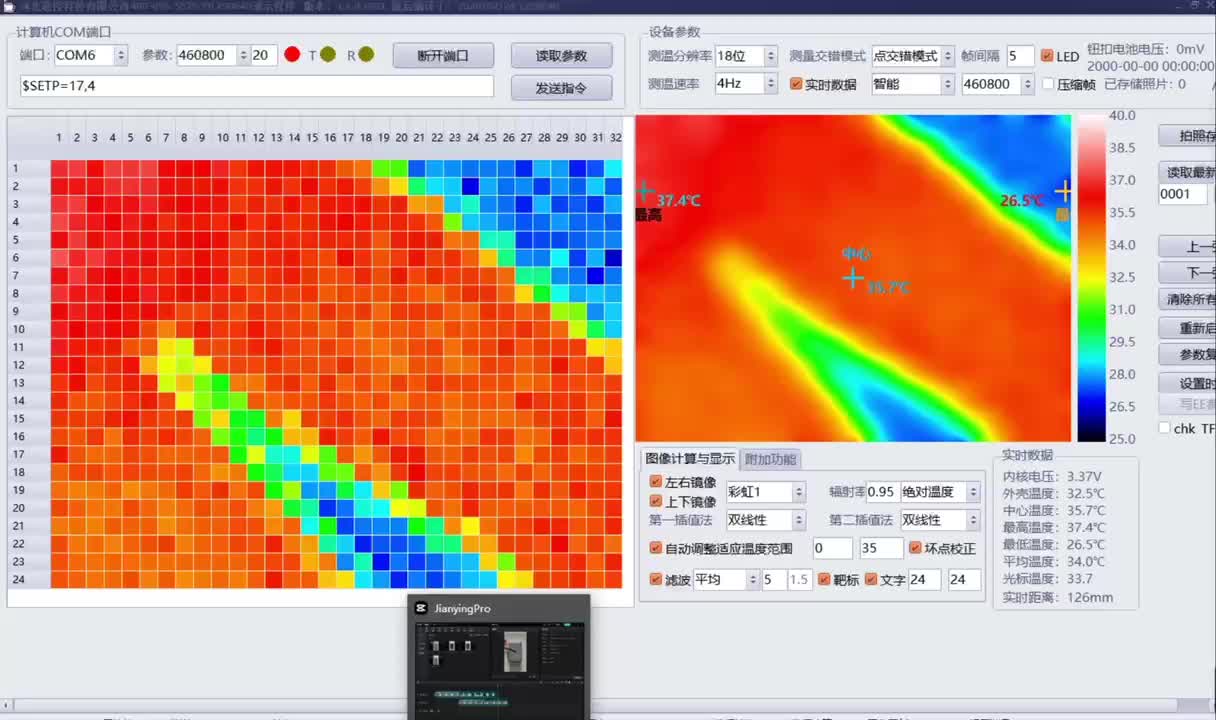

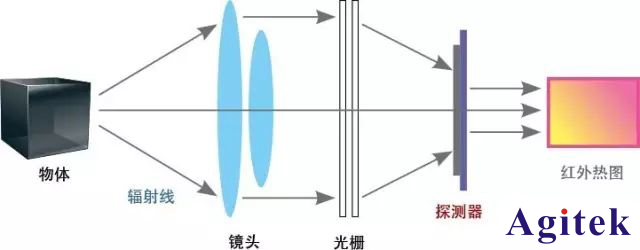

??? 紅外成像系統(tǒng)的功能框圖如圖1所示。整個系統(tǒng)功能在FPGA上實(shí)現(xiàn)。系統(tǒng)上電后,F(xiàn)PGA進(jìn)行配置,紅外焦平面探測器在驅(qū)動信號的作用下響應(yīng)紅外目標(biāo)輻射,將輻射信號轉(zhuǎn)變?yōu)?a href="http://www.1cnz.cn/analog/" target="_blank">模擬電壓信號輸出;A/D轉(zhuǎn)換模塊將模擬電壓信號轉(zhuǎn)變?yōu)?a target="_blank">數(shù)字信號,經(jīng)非均勻性校正、盲元處理等過程,將數(shù)據(jù)存入FPGA外部存儲器中。本工作的主要任務(wù)就是把存儲器中的數(shù)據(jù)通過USB接口傳輸?shù)絇C機(jī),以便于根據(jù)需要對數(shù)據(jù)做進(jìn)一步的處理工作。

2 USB固件結(jié)構(gòu)設(shè)計

??? USB固件結(jié)構(gòu)設(shè)計包括枚舉過程和數(shù)據(jù)傳輸過程。數(shù)據(jù)傳輸過程與枚舉過程中的in中斷的處理方法類似。因此這里主要介紹枚舉過程的固件編寫。

??? 枚舉過程的流程圖如圖2所示。

??? 枚舉過程就是主機(jī)通過向設(shè)備發(fā)送一系列請求來識別設(shè)備的過程。USB一共定義了11種標(biāo)準(zhǔn)USB請求,其中有些請求是必須的。例如,主機(jī)必須通過Get Descriptor請求來獲取設(shè)備的設(shè)備描述符、接口描述符和端點(diǎn)描述符等信息,才能識別設(shè)備;必須通過Set Address請求為設(shè)備分配惟一的非零地址,以便于主機(jī)識別設(shè)備并與設(shè)備進(jìn)行數(shù)據(jù)傳輸;必須通過SetConfiguration請求為設(shè)備分配非零的配置值等。USB請求只能使用控制管道來進(jìn)行傳輸。主機(jī)在沒有識別連上的是何種設(shè)備之前,會為未知設(shè)備分配一個默認(rèn)地址O,主機(jī)通過0地址與設(shè)備通信,直到主機(jī)確定真正有設(shè)備連接了之后,就會為該設(shè)備分配一個惟一的非零地址。在此之后,主機(jī)可通過這個非零地址跟設(shè)備通信,包括獲取該設(shè)備的所有配置信息、接口信息以及完成最后的數(shù)據(jù)傳輸?shù)取?br>2.1 芯片初始化

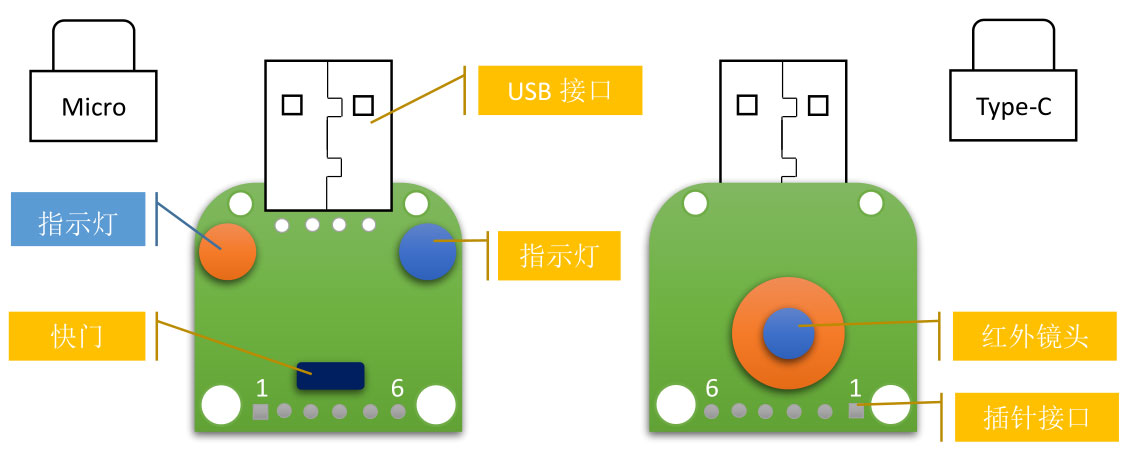

??? 芯片的初始化主要包括工作模式、速度的選擇以及寄存器的配置等操作。工作模式的選擇可通過設(shè)置ISPl362的第62引腳A1為高電平來實(shí)現(xiàn)。這里實(shí)現(xiàn)的是全速的數(shù)據(jù)傳輸。下面主要介紹寄存器的配置。

??? ISPl362設(shè)備控制器內(nèi)部40多個寄存器。編寫代碼時的重點(diǎn)工作就是根據(jù)寄存器每一位代表的意義確定配置值,特別是有些關(guān)鍵位,只有正確配置方能保證芯片的正常工作。在使用ISPl362之前,要先配置的寄存器有模式寄存器、硬件配置寄存器、中斷使能寄存器等,端點(diǎn)配置寄存器可以在任何時刻完成,但僅在枚舉后的初始化后才有效。為了便于程序設(shè)計,在一開始對模式寄存器、硬件配置寄存器、中斷使能寄存器等配置的同時,也對16個端點(diǎn)配置寄存器進(jìn)行配置。端點(diǎn)0為控制端點(diǎn),包括in和out端點(diǎn),這兩個端點(diǎn)大小固定,均為64 B。枚舉過程就是通過這個端點(diǎn)進(jìn)行的。其余14個為可編程端點(diǎn),也可以被配置成雙緩沖端點(diǎn)進(jìn)一步提高吞吐量。設(shè)計中端點(diǎn)1配置為64 B雙緩沖批量in端點(diǎn);端點(diǎn)2配置為16 B中斷out端點(diǎn);端點(diǎn)3配置為16 B中斷in端點(diǎn)等;可以禁能不用的端點(diǎn)。配置模式寄存器時,尤其要注意可以通過第三位來使能所有中斷。對于硬件配置寄存器,要注意中斷輸出管腳INT2的設(shè)置,這里選擇低電平有效的中斷信號模式。對這些寄存器正確配置之后,ISP1362就會進(jìn)入預(yù)期工作模式。

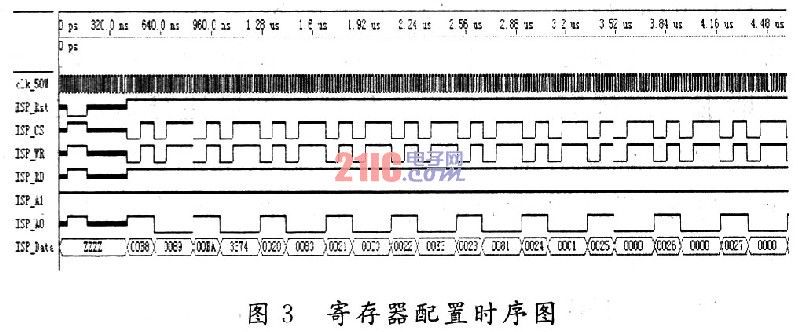

??? 由于ISP1362中需要配置的寄存器很多,因此本設(shè)計中先在FPGA生成一片16位,大小為128 B的ROM,再將需要配置的寄存器的寫命令和配置值按照順序?qū)懭隦OM中,配置時,只需將ROM中的數(shù)據(jù)依次寫入芯片中即可。寄存器的配置時序如圖3所示(為便于觀察,圖3中只截取了部分寄存器的配置情況)。

??? 圖3中信號clk_50M為全局時鐘;ISP_Rst為芯片的復(fù)位信號;ISP_CS,ISP_WR,ISP_RD分別為ISPl362的片選信號、讀信號、寫信號,均為低電平有效;ISP_Al為模式選擇信號,當(dāng)其值為1時,芯片工作于設(shè)備控制器模式,為O時芯片工作于主機(jī)控制器模式;ISP_A0為高時對應(yīng)的ISP_Data為DC的初始化命令,當(dāng)ISP_AO為低時對應(yīng)的ISP_Data為寫入相應(yīng)寄存器的配置值。

2.2設(shè)備接收請求

??? 主機(jī)的每次請求,都是將請求以setup包的形式發(fā)送到out端點(diǎn)的out緩沖區(qū)。當(dāng)out緩沖區(qū)接收到數(shù)據(jù)時,芯片的INT2管腳將會有中斷產(chǎn)生。在模式寄存器、硬件配置寄存器、中斷使能寄存器正確配置之后,當(dāng)有中斷事件產(chǎn)生時,ISP1362內(nèi)部的SIE就能夠檢測到中斷,并置中斷寄存器的相應(yīng)位為高電平。固件通過讀取并分析中斷寄存器的值來判斷中斷類型,再進(jìn)行中斷事件的處理。

??? 固件首先檢測到的是out中斷。這是因?yàn)樵谏想姀?fù)位以后,主機(jī)就向out緩沖區(qū)發(fā)第一個setup請求包。當(dāng)接收到out中斷時,固件首先讀取out端點(diǎn)的端點(diǎn)狀態(tài)寄存器將中斷清除,以便于芯片接收其他的中斷。接著固件再根據(jù)端點(diǎn)狀態(tài)寄存器的值判斷out緩沖區(qū)內(nèi)是否含有setup包,然后固件讀取out緩沖區(qū)。

??? 根據(jù)out緩沖區(qū)的內(nèi)容判斷是何種請求,再決定做何響應(yīng)。in中斷的產(chǎn)生不同于out中斷。in中斷是在in緩沖區(qū)由空變滿之后才產(chǎn)生的,in中斷的產(chǎn)生需要固件進(jìn)行寫in緩沖區(qū)的操作。換而言之,是寫in緩沖區(qū)的操作引發(fā)了in中斷的產(chǎn)生,而不是in中斷的產(chǎn)生引發(fā)了寫緩沖區(qū)的操作。當(dāng)固件檢測到in中斷時,同樣要通過讀in端點(diǎn)的端點(diǎn)狀態(tài)寄存器將中斷清除。

2.3設(shè)備響應(yīng)請求

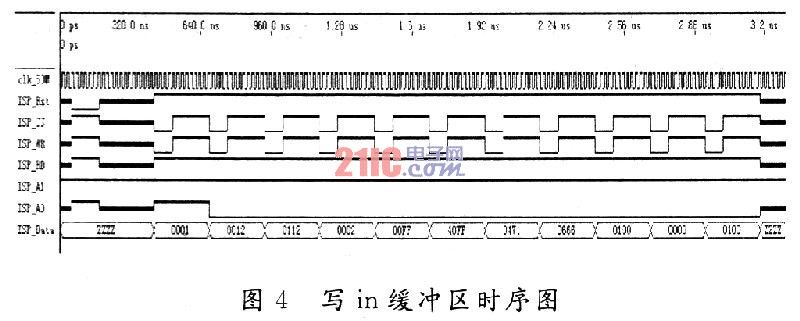

??? 當(dāng)芯片工作于設(shè)備控制器模式下時,設(shè)備端的工作就是被動的執(zhí)行主機(jī)發(fā)來的請求。請求類型的確定是通過讀取out緩沖區(qū)里的setup包來完成的。一個setup包(即請求包)有8個字節(jié),根據(jù)其中第二個字節(jié)能夠判斷出請求類型。由流程圖可以看出,枚舉過程中主機(jī)要發(fā)出獲取描述符、設(shè)置地址、設(shè)置配置等請求,對于獲取描述符的請求,還需要進(jìn)一步判斷是獲取何種描述符的請求,這可以通過請求的第三,四字節(jié)的值來確定。一旦確定了請求類型,設(shè)備就可以確定該如何響應(yīng)請求。當(dāng)確定主機(jī)發(fā)的是獲取何種描述符請求之后,固件就將相應(yīng)的描述符的值寫入in端點(diǎn)的端點(diǎn)緩沖區(qū)。寫in端點(diǎn)緩沖區(qū)的方法與寄存器配置類似,其時序如圖4所示。

??? 圖4中ISP_A0為高時對應(yīng)的ISP_Data(即0001)是寫in緩沖區(qū)的命令,ISP_A0為低時對應(yīng)的ISP_Data為寫入的數(shù)據(jù),其中第一個數(shù)據(jù)即(0012)為要寫入的數(shù)據(jù)的長度,其余為設(shè)備描述符。當(dāng)需要發(fā)送數(shù)據(jù)時,只需使能in緩沖區(qū)即可。若是設(shè)置地址請求,固件的工作就是將地址值取出來寫入設(shè)備地址寄存器,然后再向主機(jī)發(fā)送一個空包。

3 LISB固件代碼實(shí)現(xiàn)

??? 在FPGA上用Verilog HDL實(shí)現(xiàn)上述功能時,難點(diǎn)有:一是多驅(qū)動問題;二是輸入/輸出端口的使用問題。由于程序中有多個模塊同時作用于ISP1362的控制信號線以及數(shù)據(jù)線,如果處理不當(dāng),可能會產(chǎn)生同一時刻對同一信號有兩次或兩次以上的賦值的現(xiàn)象。為了避免這種情況的發(fā)生,就要在適當(dāng)?shù)臅r刻給信號線附上高阻,即當(dāng)一個模塊在驅(qū)動某一信號時,應(yīng)避免其他模塊也在這一時刻驅(qū)動這一信號。芯片的16位數(shù)據(jù)線為雙向,這可以減少管腳的數(shù)量,節(jié)省資源。但在使用時若不注意,同樣容易出錯。inout管腳在使用時一般用三態(tài)門來實(shí)現(xiàn),當(dāng)inout端口不輸出時,要將三態(tài)門置高阻。這在具體的軟件實(shí)現(xiàn)中可以使用一個連續(xù)賦值(Assign)語句來實(shí)現(xiàn),通過連續(xù)賦值語句將一個條件操作符賦值給這個輸入/輸出變量。該設(shè)計的代碼中,雙端口用語句ISP_Data=en? data:16’hzzzz實(shí)現(xiàn)其輸入/輸出功能。當(dāng)en信號為高時,ISP_Data作為輸出信號使用,其值即為data的值;當(dāng)en信號為低時,ISP_Data作為輸入信號使用。因此,程序中就可以根據(jù)需要通過控制en信號的高低來實(shí)現(xiàn)ISP_Data的輸入/輸出使用。

4 結(jié)語

??? 采用高性能的Altera的FPGA中的EP2C70F672C6作為主控器件,實(shí)現(xiàn)了ISP1362在設(shè)備控制器工作模式下的功能,為解決紅外圖像處理系統(tǒng)中的數(shù)據(jù)傳輸問題提供了新的途徑。在具體的軟件實(shí)現(xiàn)中,成功地解決了多驅(qū)動問題和雙向端口的使用問題。驗(yàn)證結(jié)果表明,程序的穩(wěn)定性好、可移植性高,并且容易實(shí)現(xiàn)、易于維護(hù)。在成功地進(jìn)行了枚舉的過程之后,加載上設(shè)備驅(qū)動程序即可實(shí)現(xiàn)數(shù)據(jù)向主機(jī)以12 Mb/s的傳輸。

電子發(fā)燒友App

電子發(fā)燒友App

評論