在目前的DVB-C廣播電視系統的傳輸接口中,有兩種MPEG-2視頻傳輸接口標準:異步串行接口標準 ASI和同步并行接口SPI。SPI一共有11位有用信號,每位信號差分成兩個信號用來提高傳輸抗干擾性

2018-12-07 10:33:21

DVB-C視頻傳輸接口ASI的設計方法在目前的DVB-C廣播電視系統的傳輸接口中,有兩種MPEG-2視頻傳輸接口標準:異步串行接口標準 ASI和同步并行接口SPI。SPI一共有11位有用信號,每位

2009-09-26 17:58:24

DVB-H標準綜述制訂DVB-H標準的主要目的是要通過手持接收機接收IP寬帶流媒體圖象數據,例如:流媒體MPEG4,微軟的WM9等;甚至有些廠家在設想通過在目前第二代2G移動通訊網上面加入DVB

2009-07-17 21:33:27

組成,如圖2所示。圖2 數字電視模塊功能方框圖移動數字電視接收器的輸入是來自于天線的射頻廣播信號,其輸出是MPEG-2傳輸碼流(TS)或IP數據包。它們再輸入到應用處理器進行視頻和音頻的解壓縮,并在

2013-03-26 21:38:27

,采用多協議封裝格式(MPE),它可以將IP內容,時間切片信息和數據節(SECTION)內的糾錯碼,打入到傳輸流當中,為了節省單頻網適配器,GPS時鐘信息也可以通過IP/DVB打包機插入到TS流中。通用

2009-07-17 21:34:33

、支持小范圍和大范圍的單頻網運行(SFN),同一路數字電視節目,可以通過多個發射機的同一頻率同時發射,以提高接收效果。5、DVB-T系統支持6/7/8MHz的帶寬。DVB-T系統中可調節的參數1 內糾錯碼

2008-05-28 13:45:17

DVB-T的擴展DVB-H介紹制訂DVB-H標準的主要目的是要通過手持接收機接收IP寬帶流媒體圖象數據,例如:流媒體MPEG4,微軟的WM9等;甚至有些廠家在設想通過在目前第二代2G移動通訊網

2009-07-17 21:42:28

DVB-T網絡的接收與覆蓋

2008-08-05 13:21:49

,其主要功能為:1, 加入時間切片TIME SLICING,達到剩電的目的。2、在IP/DVB的MPE封裝時加入RS糾錯碼FEC,提高接收機的抗干擾能力。上面所提到的DVB-H的相關功能會影響到

2009-07-17 21:36:34

誰有法國電信的加密碼流?需要DVB制式,最好是加密和不加密的節目在一起的。價格好說。

2008-11-19 13:36:54

后的碼流叫做傳輸流(TS),傳輸流中包括多個節目源的不同信號,為了區分這些信號,在系統復用器上需要加入服務信息(SI),使接收端可以識別不同的節目。 3 DVB-S數字衛星電視系統基本組成 發送端

2010-03-17 08:28:47

DVB條件接收前端系統同密實施執行技術報告

2009-05-08 09:01:39

DVB條件接收同密前端系統結構和同步技術規范

2009-05-08 09:02:09

DVB條件接收標準參考文件

2009-05-08 09:07:28

。 lMulticrypt。圍繞著公共接口規范解析,這個公共接口當被安裝在機頂盒或者電視中的時候允許用戶手工地在CA系統間交換。因此,當收看者面對的是沒有安裝在他的盒子里面的CA系統時,他簡單地交換卡片。 有關DVB標準

2009-07-31 14:48:07

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

PCI型衛星電視信號源DTA-107S2[/td]一、技術特點兼容DVB-S標準EN300 421,DVB-S2標準EN302 307以及ISDB-S內置L波段捷變頻器,輸出頻率:950

2011-08-08 17:34:13

數據通道,雙向數據通路上各有6個FIFO進行數據緩沖,可同時進行高速的數據接收和發送。8個32位Maibox寄存器可為雙向數據通路提供消息傳送。 PCI9054還提供了一個串行EEPROM接口,容量2K

2018-12-05 10:12:42

PCI總線特點是什么?PCI接口開發現狀如何?如何去設計PCI接口?

2021-04-29 07:09:04

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

有哪位大神用過pci ip核,為什么輸入lm_req32請求,pci側沒有reqn請求輸出呢?

2016-06-27 17:56:59

3.4 DVB 條件接收及接口表準 DVB數字廣播系統中有些業務傳送的是加擾

2008-05-30 17:37:37

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

了相應的硬件和軟件設計。 關鍵詞: PCI總線 RTL8139芯片 DSP 嵌入式 基于DSP的嵌入式系統的以太網接口設計一直是熱門領域

2009-09-19 09:43:24

求大神,FPGA內部的PCI的IP軟核實現PCI接口設計?

2013-05-02 16:12:21

Gowin PCI to CAN IP 用戶指南旨在幫助用戶快速掌握 Gowin PCI toCAN 的功能,了解 Gowin PCI to CAN IP 的產品特性、特點及使用方法。

2022-10-10 06:25:17

Gowin PCI to Ethernet IP 主要內容包括特征簡介、功能描述、接口列表以及參數配置,旨在幫助用戶快速了解 Gowin PCI to Ethernet IP 的產品特性及使用方法。

2022-10-10 10:28:35

,國際上只有I-Shou大學的Yu-Jung Huang等人設計了可驅動不同規模LCD的驅動電路IP核,通過在系統中植入嵌入式微處理器來實現這一功能。但是,這種嵌入式微處理器使系統更復雜,而且成本更高

2012-08-12 12:28:42

論壇里面的大神們,有沒有已經完成LDPC碼編譯碼算法的FPGA實現,本人目前在做這方面的項目,時間比較緊,緊急求購IP核。。

2012-04-16 23:43:28

TLP格式,并傳送給發送引擎;接收引擎用于從PCIE IP核接收不同類型的TLP數據,接收DMA控制模塊用于實現存儲器讀請求包的發送流量控制及接收數據位寬的轉換;DMA狀態控制寄存器模塊主要用來解析來自

2019-12-26 10:46:09

的fifo接口),用戶只要操作fifo接口,無需關心PCIE的內部驅動。為了便于讀者更加明白,可以深入了解PCIE,我們將會制作一個PCIE的連載系列。今天,首先說一下自定義AXI4的IP核,至于AXI4

2019-12-13 17:10:42

了該方案的軟件和硬件的設計要點,最后給出了對模擬數據和實際視頻壓縮碼流的傳送實驗結果。關鍵詞:PCI總線 TM1300 以太網通信接口 pSOS+內核 pNA+ 1 概述TM1300是Philips

2019-06-20 05:00:02

USB_OTG_IP核中AMBA接口的設計與FPGA實現

2012-08-06 11:40:55

因實際需求,本人想使用JESD204b的ip核接收ADC發送過來的數據,ADC發送的數據鏈路速率是15gbps, 廠家說屬于204b標準。我看到jesd204b的ip核標準最大是12.5gbps,但是支持的支持高達16.375 Gb/s的非標準線速率。請問我可以使用這個IP核接收ADC的數據嗎?

2020-08-12 09:36:39

摘要:本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA芯片EP1C12和PCI IP核以及高速串行

2012-11-28 15:38:05

什么是雙碼流?雙碼流的性能有什么優點?

2021-05-28 06:10:07

ddr2_controller模塊例化的接口。這里可以分為三大類,第一類為系統類接口,主要是一些系統或PLL的復位、時鐘等接口;第二類為帶“local_*”的接口,是DDR2 IP核與用戶邏輯間的接口;第三類為帶

2016-10-27 16:36:58

嗨,我想在EDK中使用ISE中提供的PCI Express IP核,這意味著我應該將所有ISE IP核的verilog模塊導入EDK。這是可能的,如果可能的話請發送相關文件。謝謝&問候,Madhu.B

2020-03-24 08:14:50

新人想選用PCI的接口芯片,查了一下,有好多種:PCI2040、PCI9052、PCI9054、PCI9080、S5933、還有中國的CH365這么多的接口芯片他們的區別是什么?如果我做PC機PCI接口與DSP6713的接口,應該用哪種比較好呢?

2013-12-05 18:16:17

和朋友開發了幾個基于 FPGA 的高速存儲 IP 核,考慮到工業相機等應用場合需要有文件系統以方便做數據管理,所以將 NVMe 和 exFAT 兩大IP核集成一起,可以實現將數據寫入SSD后,拔下

2022-06-03 11:35:06

本文的應用背景為某一工業測控系統,該系統采用FPGA實現測量數據的采集和控制信號的輸出,通過定制PCI接口IP實現一個32位目標設備的PCI總線接口轉換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級設計集成到單個芯片中即實現片上系統SoC。IP核的復用是SoC設計的關鍵,但困難在于缺乏IP核與系統的接口

2019-06-11 05:00:07

Viterbi譯碼的基本過程,接著根據Viterbi譯碼器IP核的特點,分別詳細介紹了并行結構、混合結構和基于混合結構的增信刪余3種Viterbi譯碼器IP核的主要性能和使用方法,并通過應用實例給出了譯碼器IP

2010-04-26 16:08:39

、不利于系統的升級優化,難于應用。為此,各大FPGA廠商紛紛推出基于各自可編程邏輯器件結構與工藝的PCI IP模塊(軟核、固核或硬核)。 Xilinx,Altera,Actel及QuickLogic等公司

2019-04-17 07:00:06

、不利于系統的升級優化,難于應用。為此,各大FPGA廠商紛紛推出基于各自可編程邏輯器件結構與工藝的PCI IP模塊(軟核、固核或硬核)。 Xilinx,Altera,Actel及QuickLogic等公司

2019-04-12 07:00:11

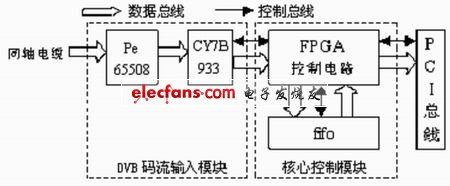

緊湊、接口簡單、性能可靠、易于升級。系統硬件框圖如圖1所示。從圖中可以看出,由于使用了FPGA及PCI IP核,使整個硬件電路顯得特別簡潔。它主要由DVB碼流輸入模塊和核心控制模塊組成。串行DVB傳輸

2018-12-07 10:34:34

發送器上;對于接收端則剛好相反,收到串行碼后,先解碼,然后送給數據鏈路層。在生成PCIE的IP核時,至少選擇2個存儲區,一個是BAR[1:O],用作用戶開發板的擴展存儲區用;還有一個是BAR2,下面所有

2019-05-21 05:00:02

。圖3給出了設置階段的細節。如果數據沒有正確接收設備就會忽略它,而且不返回應答包。 2 USB IP模塊設計和代碼編寫USB接口主要有UTM(USB Transceiver Macrocell

2018-11-21 11:30:06

DVB碼流接收卡系統硬件模塊該如何去設計?

2021-05-27 06:19:20

協議外,還負責解釋設備子類協議,并實現對具體外部應用系統(設備元件)的操作。 從硬件結構分析,基于增強型8051MCU核的 USB2.0設備接口芯片(IP核)應包括以下幾個模塊: (1)USB2.0

2018-12-03 15:24:04

如何用FPGA實現DVB碼流分析功能的嵌入式設計方案?

2021-04-28 06:19:10

HiI致力于研究在FPGA / Spartan 3E上連接打印機的研究項目。我可以獲得打印機接口IP核,或者沒有這樣的核心。如果可能,請幫助我。感激地以上來自于谷歌翻譯以下為原文HiI work

2019-07-04 06:32:58

本文利用Altera公司的Quartus開發工具設計了一個基于Avalon總線接口的UPFC控制器IP核,以便于和NiosII組成一個完整的控制系統。

2021-04-08 06:25:12

`ASI:傳輸的是數字信號,壓縮視頻信號(例如MPEG2-T,里面是H.264碼流),用于廣播電視領域。 在目前的DVB-C系統設備的傳輸接口有兩種MPEG2視頻碼流傳輸接口標準:異步串行接口ASI

2017-06-06 13:32:42

本文介紹了IP核的概念及其在SoC設計中的應用,討論了為提高IP核的復用能力而采用的IP核與系統的接口技術。引言隨著半導體技術的發展,深亞微米工藝加工技術允許開發上百萬門級的單芯片,已能夠將系統級

2018-12-11 11:07:21

怎么實現基于IP內核的PCI總線接口設計?

2021-05-27 06:34:05

如何實現基于IP模塊的PCI接口設計?

2021-04-20 06:28:50

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設計?

2021-04-28 06:10:23

你好我想購買和使用PCI 32位啟動器/目標IP核。我的FPGA是XC3S200AN Spartan3 / AN。我想知道在這種類型的FPGA上有這個IP核功能。這個問題的答案對我來說非常重要。請

2019-07-19 13:49:20

。改變IP首部的IP地址,將數據包送回發送者。 2.2.4 傳輸控制協議TCP TCP協議是面向連接的、端到端的可靠通信協議。它采用了許多機制保證傳輸可靠性,應用于嵌入式系統顯得過于復雜。在嵌入式TCP

2019-04-23 07:00:10

協議的正確執行,具體來說,就是把TCP/IP協議的處理工作放到主程序中對網絡接口的控制芯片采用循環查詢方式,在其他中斷任務的執行間隙處理TCP/IP協議,以犧牲系統的響應時間換取系統的可靠性,再者由于

2019-04-28 09:57:18

、不利于系統的升級優化,難于應用。為此,各大FPGA廠商紛紛推出基于各自可編程邏輯器件結構與工藝的PCI IP模塊(軟核、固核或硬核)。 Xilinx,Altera,Actel及QuickLogic等公司

2019-05-08 07:00:46

結構緊湊、接口簡單、性能可靠、易于升級。系統硬件框圖如圖1所示。從圖中可以看出,由于使用了FPGA及PCI IP核,使整個硬件電路顯得特別簡潔。它主要由DVB碼流輸入模塊和核心控制模塊組成。串行DVB

2019-05-05 09:29:32

; PCI突發方式,133M字節/秒數據峰值傳送; 功能1,2 16C950高速串口IP核設計 完全VHDL源代碼設計,標準接口模塊化設計,可以移植到非PCI接口應用; 軟件兼容16C550

2019-06-20 05:00:02

PCB設計,使用獨立的外部時鐘同步芯片,可以為PCI及其它接口提供穩定的零延遲時鐘系統電路,滿足PCI總線的時鐘要求,使驗證平臺高速,穩定,可靠的工作。 S1500硬件驗證板照片以下為IP核驗證平臺提供

2019-06-12 05:00:07

核處理器NIOSⅡ作為系統的主控制器,結合ARINC429專用器件和其他外圍設備實現數據的收發功能。 ARI NC429接口板由數據收發、存儲器擴展、監控、PCI總線接口等模塊組成。NIOSⅡ控制

2019-04-26 07:00:08

開放核協議—IP核在SoC設計中的接口技術

2019-05-27 09:52:01

控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD/FPGA的規模越來越大,設計越來越復雜,使用IP核是一個發展趨勢。許多公司推薦使用現成的或經過

2019-04-12 07:00:09

DVB條件接收標準參考文件(英文版):DVB條件接收前端系統同密實施執行技術報告DVB條件接收同密前端系統結構和同步技術規范DVB通用加擾算法代理協議藍皮書TS103197V151,在數字電

2009-05-07 21:30:54 0

0 DVB條件接收前端系統同密實施執行技術報告

Digital Video Broadcasting (DVB);Implementation Guidelines of the DVBSimulcrypt Standard

2009-05-07 21:32:14 14

14 DVB條件接收同密前端系統結構和同步技術規范:

Digital Video Broadcasting (DVB);DVB SimulCrypt;Head-end architecture and synchronization

2009-05-07 21:32:57 27

27 制訂DVB-H標準的主要目的是要通過手持接收機接收IP寬帶流媒體圖象數據,例如:流媒體MPEG4,微軟的WM9等;甚至有些廠家在設想通過在目前第二代2G移動通訊網上面加入DVB-H來替代第

2009-07-17 21:31:45 27

27 根據對DVB-H 協議中的關鍵技術—時間切片、多協議封裝及前向糾錯編碼(MPE-FEC)以及相關信道編碼技術的研究,設計實現了基于IP over DVB 的DVB-H 仿真系統。實驗表明,在所設計系統中

2010-01-11 13:54:47 13

13 PCI 9656是PLX公司設計的一款高速PCI I/O芯片,可應用于66MHz、64bit PCI和CompactPCI總線。文章簡述了PCI 9656的主要功能,介紹了一種應用PCI 9656的CompactPCI數據接收卡設計。設計中采用MAXII系

2010-08-06 16:15:13 26

26 瑞薩科技(Renesas Technology)宣布開發符合PCI Express Base Specification Revision 2.0 (PCI Express 2.0)高速串行接口標準之邏輯層與實體層之IP。整合此IP的LSI將能輕易地與其它支持PCI Express 2.0標準之

2009-01-05 16:23:24 553

553 基于PCI IP核的碼流接收卡的設計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統的硬件設計方案及設計要點的分析。該設計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 716

716

DSP與PCI網卡接口設計

基于DSP的嵌入式系統的以太網接口設計一直是熱門領域,目前利用的以太網控制器大多都是ISA接口。隨著PCI總線逐漸取代ISA總線

2009-10-25 15:30:16 1264

1264 什么是PCI接口 PCI是Peripheral Component Interconnect(外設部件

2009-12-25 10:29:55 1772

1772 IP核驗證平臺采用6層板PCB設計,使用獨立的外部時鐘同步芯片,可以為PCI及其它接口提供穩定的零延遲時鐘系統電路,滿足PCI總線的時鐘要求,使驗證平臺高速,穩定,可靠的工作。

2012-01-17 14:02:19 1501

1501

摘 要: 設計了一種基于NiosII處理器的片上系統(SoC),集成了Nios II處理器IP、PCI接口IP、網絡接口IP以及基于Wishbone總線的串行接口IP核、 CAN接口IP核等。系統具有可重配置、可擴展、靈

2012-10-18 16:50:29 2487

2487

Xilinx FPGA工程例子源碼:PCI Express IP核應用參考設計

2016-06-07 14:13:43 14

14 采用IP核的設計方法,將外設組件互連標準(PCI)總線接口與具體功能應用集成在一個FPGA上芯片, 提高了系統的集成度。在對PCI IP核進行概述的基礎上,介紹了IP核的設計方法,實現了PCI總線

2017-11-17 12:27:03 4488

4488

介紹一種基于PCI總線的高效鏈式DMA控制器的設計與實現,用于高速寬帶的計算機外設接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器的數據采集平臺,并成功應用在DVB數據接收卡中。

2017-12-06 13:56:13 2782

2782

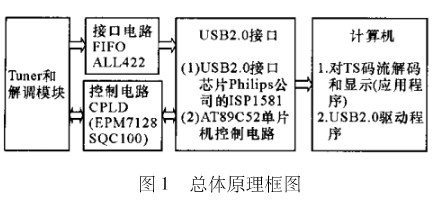

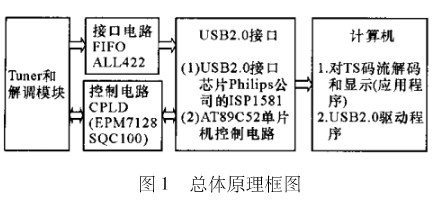

本文所介紹的DVB -T地面數字電視接收系統基于USB2. 0接口,采用DVB-T電子調諧器DT6034、通用串行總線接口器件ISP1581和計算機軟件解碼播放技術,描述了系統的硬件結構和軟件結構。所設計的系統使用方便、結構簡單、便于實現、成本低,且具有良好的市場前景。

2019-07-31 08:00:00 4161

4161

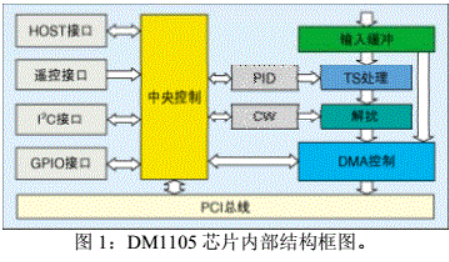

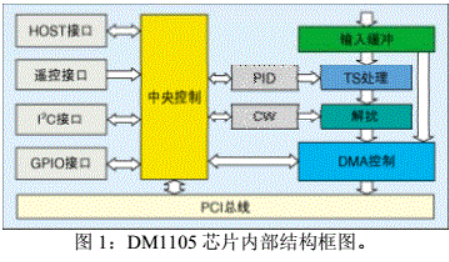

本文闡述了深圳致芯微電子有限公司的DVB TS流接收芯片DM1105芯片構造以及如何基于該芯片構建數字電視接收PCI卡方案。該方案設計簡潔,主要針對DVB-S、DVB-C、DVB-T數字電視接收,是一款實用性、針對性較強的設計。

2020-04-12 11:39:32 3311

3311

電子發燒友App

電子發燒友App

評論