片上系統(tǒng)的出現(xiàn)使得芯片可以實現(xiàn)更加復雜的功能,獲取更高的性能,但同時其內(nèi)部信號也變得越來越難以觀察和控制,相應的測試和調(diào)試工作也遇到了難以克服的時間復雜性困難。國際半導體技術(shù)路線圖( Internat io nal Technolo gy Roadmap for Semico nducto rs,IT RS) 指出,調(diào)試和定位問題所需要的時間將會隨著工藝的進步呈指數(shù)型增長。由于測試和調(diào)試工作的復雜性,其費用往往比設(shè)計費用還要高,大約要占整個SoC 總設(shè)計成本的1/ 3 以上。在整個SoC 的硬件設(shè)計過程中,從第一次投片到最后成功的實現(xiàn)所有功能,硬件調(diào)試的時間已經(jīng)接近整個時間的35%,而且這個數(shù)字隨著集成度的提高還會增加。

在整個片上系統(tǒng)中,微處理器是核心,也是最復雜的模塊,所以各個處理器內(nèi)核的提供商也都投入了大量的研發(fā)力量,在其內(nèi)核中集成了豐富的調(diào)試功能。當今流行的調(diào)試技術(shù)大多采用復用JT AG 的調(diào)試方案,但是這種方法一般都是在目標系統(tǒng)內(nèi)部插入掃描鏈,當處理器高速工作的時候,難免會限制處理器性能的提高。

為此,該設(shè)計提出一種新的調(diào)試結(jié)構(gòu),它不依賴JTA G接口且需要較少的引腳開銷,通過掛接在片上高速總線上來實時監(jiān)測片內(nèi)通信狀況,同時它直接與處理器進行交互,能夠在不影響處理器正常工作的情況下控制處理器以及訪問所有片上存儲單元,用戶可以通過專用的數(shù)據(jù)輸出鏈路進行遠程調(diào)試,發(fā)布調(diào)試指令以及獲取反饋信息。結(jié)合以上特點,該設(shè)計將以文獻[ 3]中提出的一個良好調(diào)試結(jié)構(gòu)所需具備的三個基本特征作為設(shè)計出發(fā)點: 調(diào)試的可觀察性; 調(diào)試的可控制性; 高效的通信效率; 低入侵性。

1 調(diào)試系統(tǒng)構(gòu)成

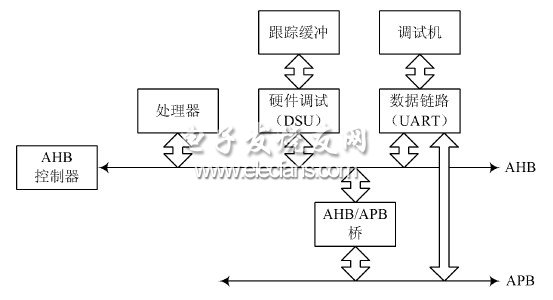

以硬件調(diào)試模塊DSU 為核心,AMBA 2. 0 總線為構(gòu)架,專用UART 為調(diào)試鏈路接口的系統(tǒng)結(jié)構(gòu)如圖1所示。

?

圖1 調(diào)試系統(tǒng)結(jié)構(gòu)圖

調(diào)試主機通過總線接口U ART 對調(diào)試單元發(fā)出調(diào)試指令; 調(diào)試單元將控制系統(tǒng)的調(diào)試狀態(tài),在滿足觸發(fā)條件時將通過與處理器的直接通信來掛起處理器,用戶可以利用調(diào)試主機通過調(diào)試接口訪問片上所有存儲單元,獲取系統(tǒng)狀態(tài)信息; 總線追蹤緩存可以工作在兩種模式下,在正常模式下通過DSU 實時記錄總線通信狀態(tài),而在調(diào)試模式下,將由調(diào)試主機對其進行訪問,尋找問題發(fā)生的根源; 指令追蹤緩存處于微處理器內(nèi)部,用來存儲執(zhí)行過的指令; 調(diào)試接口UART 將為調(diào)試主機和總線之間提供協(xié)議轉(zhuǎn)換服務(wù),實現(xiàn)串行數(shù)據(jù)與并行數(shù)據(jù)的相互轉(zhuǎn)化。

1. 1 AHB 總線

在SoC 設(shè)計中,芯片內(nèi)部總線的設(shè)計往往決定了芯片的性能、功耗與各模塊的復雜度。通常依據(jù)以下兩個方面選取總線: 一是芯片設(shè)計流程其內(nèi)在的需求,二是對交換帶寬、延時和效率靈活性的需求。該設(shè)計采用ARM 公司提出的一種片內(nèi)高速總線協(xié)議AHB,它具有以下特點: 支持突發(fā)傳輸; 支持分塊傳輸; 單周期總線控制權(quán)移交; 單時鐘沿操作; 非三態(tài)執(zhí)行; 寬數(shù)據(jù)總線架構(gòu); 數(shù)據(jù)和地址流水重疊。此外,該協(xié)議還支持靜態(tài)時序分析以及友好的測試插入。

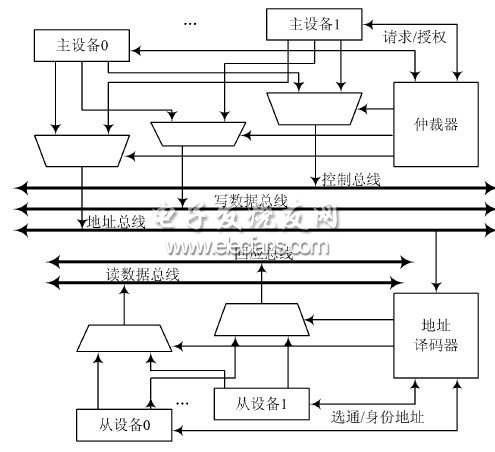

該系統(tǒng)設(shè)計的AHB 結(jié)構(gòu)如圖2 所示,由主從模塊、仲裁器以及地址譯碼器構(gòu)成,采用中央多路選擇器的互聯(lián)方式。作為核心部件,仲裁器接收最多16 個主設(shè)備的總線請求,為實現(xiàn) 可配置!的設(shè)計初衷,采用基于分治的仲裁策略,實現(xiàn)了固定與輪詢兩種優(yōu)先級算法,可以供用戶靈活選用。AHB 采用的集中式地址譯碼機制,有利于提高外圍設(shè)備的可移植性,中央譯碼器根據(jù)地址總線發(fā)來的地址以及各個從機的身份信息進行譯碼以選擇從設(shè)備,該設(shè)計為減少運算邏輯和降低功耗,僅對地址的高端位進行判別。整個AHB 系統(tǒng)由多路選擇器連接起來,避免了采用三態(tài)總線帶來的功耗、速度以及可測性方面的問題,系統(tǒng)所需的控制信號和地址數(shù)據(jù)將由多路選擇器路由到相應的目的設(shè)備,而根據(jù)路由的方向可將多路選擇器分為主模塊到從模塊多路選擇器和從模塊到主模塊的多路選擇器。此外,為了解決在沒有主機請求總線時的總線停靠( bus parking ) 問題,此系統(tǒng)還設(shè)計了一個缺省主設(shè)備( default master) ,其選擇停靠的主機號依賴選取的仲裁算法。split 傳送是AHB 的一個顯著特點,它在防止系統(tǒng)死鎖和充分利用總線方面起到了積極作用,這里為了解決分塊鎖定( split lo cked) 這一矛盾以及地址未命中問題,設(shè)計實現(xiàn)了一個虛擬從設(shè)備( dummy slave) ,當以上問題出現(xiàn)時,將由虛擬從設(shè)備代為發(fā)送回應信號。

?

圖2 AH B 總線系統(tǒng)互聯(lián)結(jié)構(gòu)

1. 2 T race Buf fer

為了實現(xiàn)引言中提到的調(diào)試的可觀察性,本系統(tǒng)中就必須具備能夠記錄總線通信信息以及指令執(zhí)行情況的模塊。AHB T race Buf fer 就是一個循環(huán)緩沖存儲體,被用來存儲AHB 上通信的所有信息。AHB 總線上的地址、數(shù)據(jù)和各種控制信號存儲在其中,并且可以在以后的分析中讀出; 同時在需要調(diào)試寫入的時候也可以通過AHB 寫總線寫入數(shù)據(jù)。本模塊因每個周期需記錄的信息位寬為128 b,所以設(shè)計的AHB TraceBuf fer 存儲器將采用4 個位寬為32 b 的同步SRAM構(gòu)成,深度可配置。若整個Buffer 的容量為1 KB,則每一個SRAM 大小為64 × 32 b,若容量為2 KB,則每一個SRAM 大小為128 × 32 b,依次類推。

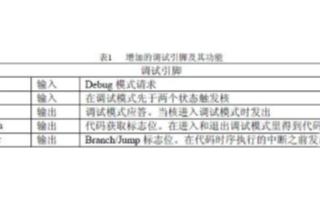

在正常總線通信中,每一筆AHB 傳輸將被循環(huán)存儲到Buffer 中,在處理器進入調(diào)試模式后,AHB TraceBuf fer 被暫時掛起,這時可由外部調(diào)試設(shè)備利用AHB總線訪問Buffer ,通過地址譯碼控制4 塊SRAM 各自的使能信號,進而完成讀/ 寫操作。Buffer 的數(shù)據(jù)輸入端為128 b,包含的有地址、數(shù)據(jù)、控制信號和控制寄存器值等,詳細見表1。

同樣在微處理器內(nèi)部實現(xiàn)一個指令T race Buf fer,用來存儲執(zhí)行過的指令。該部件同樣循環(huán)存儲,位寬128 b,利用4 塊SRAM 構(gòu)成。該存儲器中將記錄指令執(zhí)行過程中指令運行狀態(tài),操作碼、操作數(shù)和操作結(jié)果,以及PC 指針等值,用以方便以后讀出進行診斷定位。

兩塊Buf fer 在系統(tǒng)正常運轉(zhuǎn)時記錄數(shù)據(jù),所以為了保證其內(nèi)容的正確性,僅允許系統(tǒng)進入調(diào)試模式時對其進行讀寫訪問,而正常狀態(tài)下將禁止對其訪問。

表1 AHB Trace Buffer 數(shù)據(jù)分配表

?

1. 3 DSU 單元

對于嵌入式系統(tǒng)而言,其內(nèi)部的大部分信號與微處理器的工作狀態(tài)對于開發(fā)者都是不可見的,本設(shè)計就是通過提高在系統(tǒng)開發(fā)過程中用戶對系統(tǒng)的可觀察性和可控制性從而幫助開發(fā)者更為有效的定位設(shè)計中的錯誤,從而加速開發(fā)周期。為此,本系統(tǒng)必須在片上集成單獨的調(diào)試單元用于監(jiān)測系統(tǒng)運轉(zhuǎn)并能接管處于異常狀態(tài)時的微處理器。

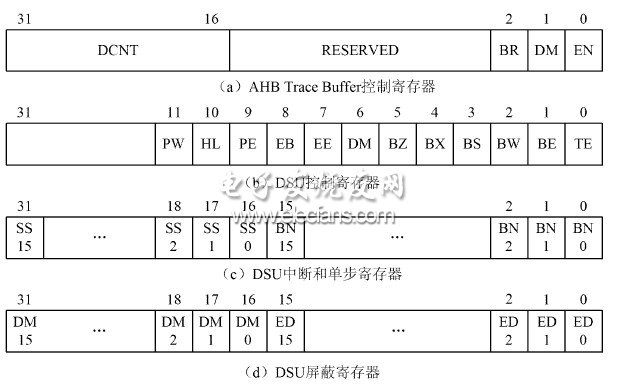

借鑒CPU中程序狀態(tài)字的作用,DSU 中首先需要一些寄存器能夠控制與管理整個調(diào)試單元的行為,它應該能接收來自調(diào)試主機發(fā)布的調(diào)試命令,同時也能夠?qū)ο到y(tǒng)內(nèi)部斷點等觸發(fā)行為做出實時響應以及在任何時刻都能被調(diào)試主機所訪問,為此,該調(diào)試單元設(shè)計了如圖3 所示的部分關(guān)鍵寄存器。

?

圖3 DSU 內(nèi)部寄存器

圖3( a) 為AHB T race Buf fer 控制寄存器。其中EN 位將控制AHB Trace Buffer 的使能; DM 位表示Buf fer 處于延遲計數(shù)模式,設(shè)計這種模式是為了方便觀察斷點發(fā)生前后定長時間內(nèi)系統(tǒng)的運轉(zhuǎn)狀態(tài); BR 位則表示AHB 斷點命中; 高16 位DCNT 表示在延遲計數(shù)模式下的延遲計數(shù)值。AHB 斷點寄存器有兩路,可寫入30 位的精確斷點地址,當AHB 地址總線上廣播的地址與該斷點地址相吻合時,將會立即凍結(jié)AHBTr ace Buf fer,同時清除AHB 控制寄存器的使能位。

電子發(fā)燒友App

電子發(fā)燒友App

評論