在CompactPCI端,PCI 9656提供了66MHz、64bit總線應用所需信號,可依據(jù)CompactPCI規(guī)范連接,通過簡單的外部電路,可實現(xiàn)Hot Swa p功能。

2020-12-08 10:49:58 2369

2369

Computer)的蓬勃發(fā)展密切相關。在處理器體系結構中,PCI總線屬于局部總線(Local Bus)。局部總線作為系統(tǒng)總線的延伸,主要功能是為了連接外部設備。

2022-09-08 14:26:30 4173

4173 PCI9656是PLX公司推出的一種64位、66MHz的PCI接口電路。具有靈活的連接性能和高性能的I/O加速器特性,用于PCI、Compact PCI和嵌入式主機設計。文中主要介紹 PCI9656 的功能、特點及應用,給出

2011-09-29 16:06:56 8076

8076

數(shù)據(jù)采集7、擴展應用實例: 廣播電視ASI信號的輸入輸出,通過J4,J5擴展32bit的EMIF總線和MCBSP0,與后板FPGA相連,實現(xiàn)后板4路ASI輸出,2路ASI輸入的使用8、技術支持

2014-06-11 11:11:47

AHCC2001PCI/CPCI 是能提供 4 路高速串行數(shù)據(jù)通信的模板, 完成系統(tǒng)內(nèi)部計算機網(wǎng)絡與外部多路串行接口的互連功能。它內(nèi)含一片高性能的串行通信控制器,可以用于各種高速數(shù)據(jù)通信場合。每路

2019-04-25 09:40:07

基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發(fā),基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-05-11 17:14:29

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發(fā),基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-14 11:56:15

基于TMS320C6678、FPGA XC5VSX95T的6U CPCI 8路光纖信號處理卡1、板卡概述 本板卡由我公司自主研發(fā),基于CPCI架構,符合CPCI2.0標準,采用兩片TI DSP

2015-09-18 15:24:37

應用的要求,也為每一個工業(yè)自動化系統(tǒng)所渴求。它的實現(xiàn)是:在結構上采用三種不同長度的引腳插針,使得模板插入或拔出時,電源和接地、PCI總線信號、熱插拔啟動信號按序進行;采用總線隔離裝置和電源的軟啟動;在軟件上

2013-01-12 11:46:35

有一個背板,用的CPCI,然后加了一個PCI,插入PCI的IO板卡時,能搜索到IO板卡,但是軟件配置時配置不了IO信號,軟件配置進入不了,是為什么呢?網(wǎng)卡板插入時,也能裝好驅動,但是也通不了,網(wǎng)絡總是被禁用,開啟不了。求解答,大神呀!!!

2017-06-21 11:13:29

PCI9656-BA66BI

2023-04-06 15:30:24

PCI9656RDK-LITE - Rapid Development Kit For PCI 9656 Generic Local Bus Designs - PLX Technology

2022-11-04 17:22:44

總線目標設備實現(xiàn)基本的傳送要求;它有5個局部地址空間和4個局部設備片選信號,局部總線與PCI總線時鐘相互獨立運行。通過配置EEPROM的內(nèi)容可以將PCI9052設定為ISA接口模式,通過8位或16位內(nèi)存

2018-12-17 11:23:00

pci設計的setup和hold時間,這些時鐘的處理可以根據(jù)實際的芯片進行調(diào)整,一般的要求是延時和pci clk的一樣,記住這里的延時不僅僅是指pcb走線的延時。7 、如果你設計的是cpci系統(tǒng),終端電阻

2021-08-12 16:32:28

設計的setup和hold時間,這些時鐘的處理可以根據(jù)實際的芯片進行調(diào)整,一般的要求是延時和pci clk的一樣,記住這里的延時不僅僅是指pcb走線的延時。7 、如果你設計的是cpci系統(tǒng),終端電阻

2018-07-10 15:10:53

。作為主設備需要49條信號線,若作為目標設備,則需要47條信號線,可選的信號線有51條。利用這些信號線便可以傳輸數(shù)據(jù)、地址,實現(xiàn)接口控制、仲裁及系統(tǒng)的功能。PCI局部總線信號如下圖所示。下面按功能分組進行

2012-04-06 14:37:24

PCI總線的信號定義PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數(shù)據(jù)信號、控制信號、仲裁信號、中斷信號...

2022-02-16 06:48:12

本人剛接觸cpci總線,自己做的背板(兩槽),一塊插計算機,一塊自己做的電路板,出現(xiàn)如下

2008-12-29 18:35:26

PCI總線是一種不依附于某個具體處理器的局部總線。從結構上看,PCI是在CPU和原來的系統(tǒng)總線之間插入的一級總線,具體由一個橋接電路實現(xiàn)對這一層的管理,并實現(xiàn)上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送。管理器提供了

2008-12-09 13:46:13

版,不久前又公布了PCIX規(guī)范。PCI的位數(shù)由32位擴展為64位,頻率從33MHz提高到133MHz。該規(guī)范是處理器、存儲器總線至周邊設備擴展的橋梁,根據(jù)PCI橋接的對象可分為Host/PCI橋(北橋

2021-05-12 07:00:00

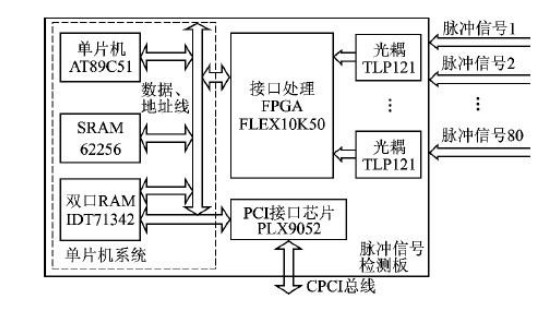

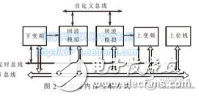

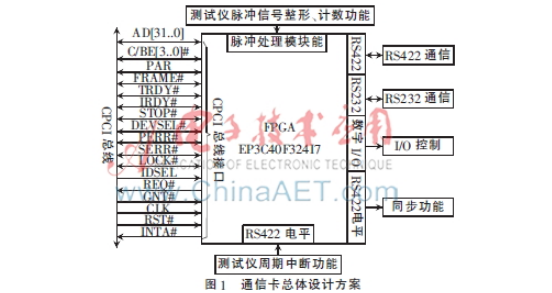

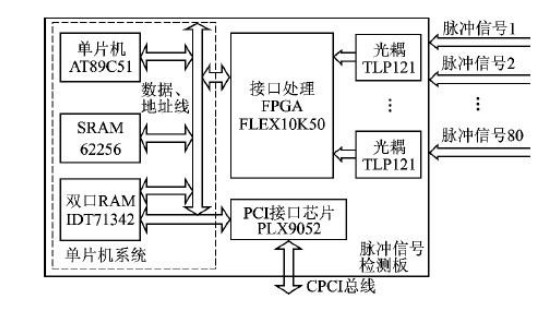

信號的發(fā)生時間及脈沖持續(xù)寬度,要求測量誤差不大于±1ms。 如圖2所示,脈沖信號檢測板的核心部分包括光耦接口電路、接口處理FPGA、單片機系統(tǒng)和PCI接口電路。板卡采用標準的6U尺寸CPCI板卡

2012-09-01 16:09:40

數(shù)據(jù)采集7、擴展應用實例: 廣播電視ASI信號的輸入輸出,通過J4,J5擴展32bit的EMIF總線和MCBSP0,與后板FPGA相連,實現(xiàn)后板4路ASI輸出,2路ASI輸入的使用8、技術支持

2014-06-10 10:16:14

提出一種基于CPCI接口DSP板的C波段雷達目標模擬器。探測回波模擬,采用軟硬件相結合的方法。由主控計算機根據(jù)雷達工作參數(shù)預先設定并計算目標數(shù)據(jù),然后將數(shù)據(jù)加載到硬件電路中。硬件電路實時合成雷達回波

2019-06-03 05:00:08

, 因此如何來實現(xiàn)該監(jiān)控系統(tǒng)中大量數(shù)據(jù)的高效、快速、準確地采集和傳輸成為設計該監(jiān)控系統(tǒng)所面臨的一個主要難題。而本文所研究的基于PCI 總線的高速數(shù)據(jù)通信卡的設計正是解決上述難題的關鍵技術之一。PCI

2010-09-22 08:51:09

。 與此同時,隨著數(shù)字信號處理器(DSP)性價比的不斷提高,其應用領域飛速擴展,從而使基于PCI總線和DSP技術的新型虛擬儀器應運而生。 系統(tǒng)的基本框架 筆者設計的基于PCI總線和DSP技術

2009-04-20 10:51:10

方式。若譯碼后設備被選中,則發(fā)送HIT信號通知狀態(tài)機做進一步處理。表6 支持的PCI總線命令2.4 數(shù)據(jù)通道在總線交易的地址期,數(shù)據(jù)通道鎖存AD總線上的地址信號,并在IRDY#和TRDY#同時

2019-05-29 05:00:02

總線速度提高到了320 MB/s。歷史上,VME總線由于其眾多的功能、強大的兼容性、并行性和高可靠性一直是實時嵌入式系統(tǒng)的首選機型,主要應用于圖像處理、軍事通信、雷達信號處理等眾多領域。本文基于雷達

2019-04-15 07:00:07

與PCI的接口是實現(xiàn)DSP與主機進行通信的關鍵。由于TMS320VC5402 DSP的HPI口是8位并口,所以PCI9052局部總線設定為8位非復用總線模式,并將其LAD[7..0]與DSP的HD

2018-12-17 11:29:06

我想用DSP能夠和CPCI總線連接。C6000系列的。不知道有什么方案?不想用PCI2040

2018-06-21 01:00:59

數(shù)據(jù)通信中應用廣泛。DDS頻率合成技術通過頻率控制字、相位控制字及參考時鐘的控制來實現(xiàn)輸出信號的調(diào)頻調(diào)相,并且輸出信號具有頻率轉換快、頻率分辨率高和相位噪聲低等優(yōu)點。綜合上述特點,設計運用PCI

2019-07-18 06:35:45

PCI9656,通過CPCI 總線經(jīng)J1和J2口傳輸?shù)?b class="flag-6" style="color: red">雷達系統(tǒng)的其他功能模塊。對于并行信號而言,32位帶寬的信號首先通過J3口發(fā)送到F-PGA內(nèi)部寄存器中FPGA接收到數(shù)據(jù)后 將數(shù)據(jù)寫入輸入緩存區(qū),并在完成一幀

2019-05-21 05:00:19

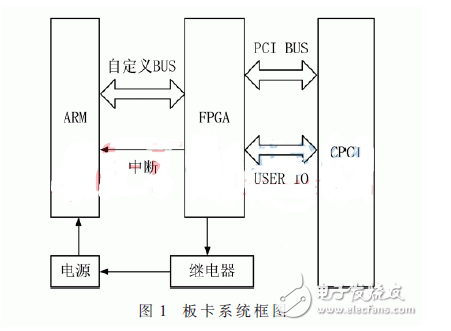

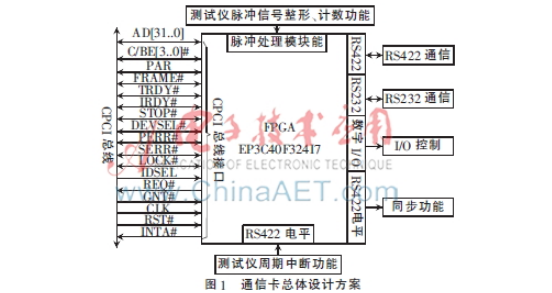

摘 要: 為了提高航空航天領域對信號處理、傳輸?shù)膶崟r性及可靠性,以CycloneIII系列EP3C40F324I7為核心處理器,設計了一種基于CPCI總線的多功能通信卡。結合高效的FPGA算法

2016-01-14 10:59:18

PCI總線是高性能的32/64位同步總線,具有嚴格的規(guī)范保證數(shù)據(jù)傳輸?shù)目煽啃裕?b class="flag-6" style="color: red">處理器與高集成度的外圍設備提供高速安全的接口,是迄今為止最成功的總線規(guī)范之一。由于PCI總線協(xié)議非常復雜,目前實現(xiàn)

2018-12-04 10:35:21

如何實現(xiàn)單片機與PCI總線接口的并行通信?

2021-04-29 07:14:26

CPCI的特點是什么?CPCI總線與Intel 82551是如何連接的?如何去實現(xiàn)一種基于CPCI總線的以太網(wǎng)卡?

2021-06-03 06:49:06

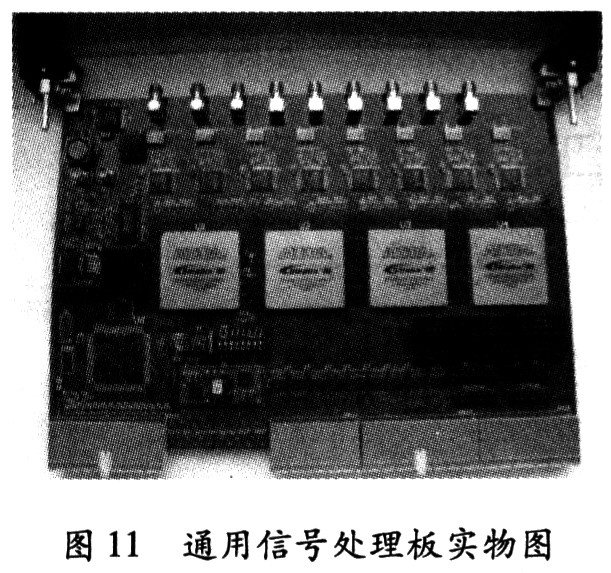

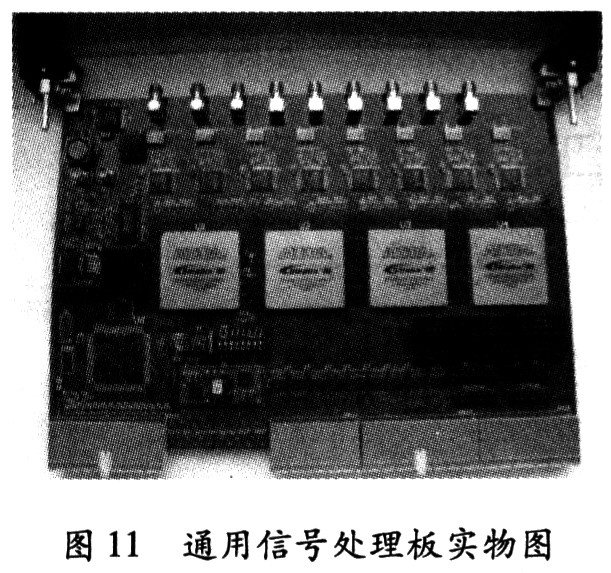

文中采用Ahera公司最新、具有最佳性能、最大密度和最低功耗的高端FPGA StratixⅢ設計了基于CPCI總線的通用FPGA信號處理板,并在某雷達系統(tǒng)中進行了實際應用。

2021-05-07 06:54:25

怎么實現(xiàn)基于CPCI總線的多網(wǎng)口卡設計?

2021-06-02 06:15:08

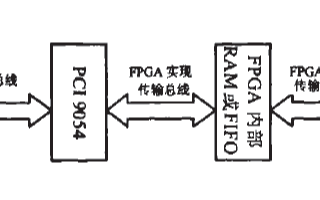

本文提出了一種新的包括PCI9054單周期讀、寫和存儲器映射傳輸?shù)脑O計,并討論了通用PCI總線高速數(shù)據(jù)采集卡的實現(xiàn)方案。

2021-06-08 06:28:30

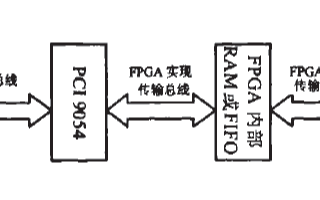

本文設計的系統(tǒng)采用PLX公司生產(chǎn)的CPCI協(xié)議轉換芯片PCI9054,通過Verilog HDL語言在FPGA中產(chǎn)生相應的控制信號,完成對數(shù)據(jù)的快速讀寫,從而實現(xiàn)了與CPCI總線的高速數(shù)據(jù)通信。

2019-08-27 08:24:41

PCI總線的中斷機制PCI總線使用INTA#、INTB#、INTC#和INTD#信號向處理器發(fā)出中斷請求。這些中斷請求信號為低電平有效,并與處理器的中斷控制器連接。在PCI體系結構中,這些...

2022-02-16 06:31:43

我想用tms320c6678作為處理器設計一款CPCI的板卡,可是6678上只有PCIE,沒有PCI,我應該怎么做才能實現(xiàn)6678與上位機之間通信,謝謝!!!

2018-12-28 11:05:42

本文首先介紹了PCI Bridge的工作原理;然后以Motorola公司提供的CPX8000系列工控機為例,討論了兩個SBC是如何基于背板(Backplane)上的CPCI總線,并利用PCI Bridge的地址映射機制,通過互訪內(nèi)存的方式最終實現(xiàn)雙機通信;最后介紹了實際應用時應注意的性能優(yōu)化問題。

2021-06-03 06:45:30

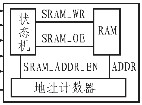

中分別寫入地址和數(shù)據(jù)(兩者是一一對應的)。局部端狀態(tài)機在寫的過程中,根據(jù)PCI9656的blast#信號來判斷單次還是突發(fā)以及突發(fā)是否結束;如果Cache中空余位置少于4個則進入等待狀態(tài)。DSP

2019-05-17 07:00:13

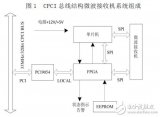

;計算機對結果數(shù)據(jù)進行分析處理、按一定的標準進行判別,將測試結果進行顯示、控制分選機對被測器件進行分選。1 PCI總線及其接口的實現(xiàn)自動化集成電路測試系統(tǒng)(ATE)的結構圖如圖1所示。本設計的接口總線選用

2019-05-30 05:00:02

通信號,MEM_RD用于提供存儲器讀選通信號,MEM_WR用于提供存儲器寫選通信號,上述引腳均為低電平有效。與PCI總線相連的引腳直接與PCI總線對應。4 PCI接口卡的設計和實現(xiàn)4.1 原ISA接口卡

2019-04-29 07:00:09

協(xié)議器件HS3282完成發(fā)送數(shù)據(jù)緩存和串并轉換(接收時串行轉換為并行,發(fā)送時并行轉換為串行),HS3182作為3282的驅動器完成差分信號轉換及傳輸速率調(diào)節(jié)。PC機通過PCI總線與接口板通信,實現(xiàn)對發(fā)送

2019-04-26 07:00:08

Maximum PCI Bandwidth for Your 32-bit Local Bus ApplicationsThe PCI 9656 offers flexible

2008-10-13 11:12:25 73

73 基于FPGA的PCI總線接口設計::PCI是一種高性能的局部總線規(guī)范,可實現(xiàn)各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現(xiàn)PCI總線接

2009-06-25 08:17:18 48

48 本文簡要介紹了PCI 總線的仲裁機制, 完成了PCI 總線仲裁器核心的設計、實現(xiàn)。通過ModelSim 進行了軟件仿真,最后在XILINX 公司的FPGA 上加以了驗證。

2009-09-03 08:18:29 27

27 PCI,PCI-E,CPCI,PC104 板卡說明書:CPCI:全稱:CompactPCI,1997 年8月,PICMG發(fā)布了第一個CompactPCI技術標準PICMG 2.0 Rev. 1.0

2009-09-29 10:43:48 189

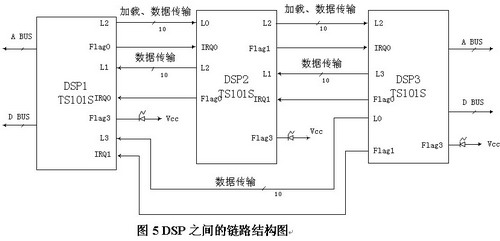

189 CPCI 總線是一種兼容性強、功能全面的計算機總線。文章通過對TI 公司推出的DSP 芯片(TMS320F2812)、FPGA 芯片(EPF10K30A)和CPCI 接口芯片(PCI9054)的功能和特點的深入分析,討論了

2009-12-19 12:08:10 35

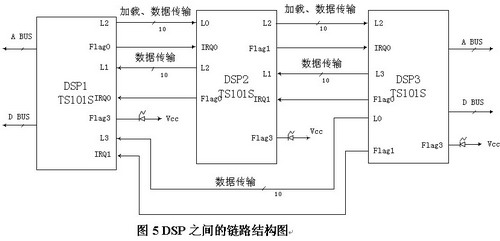

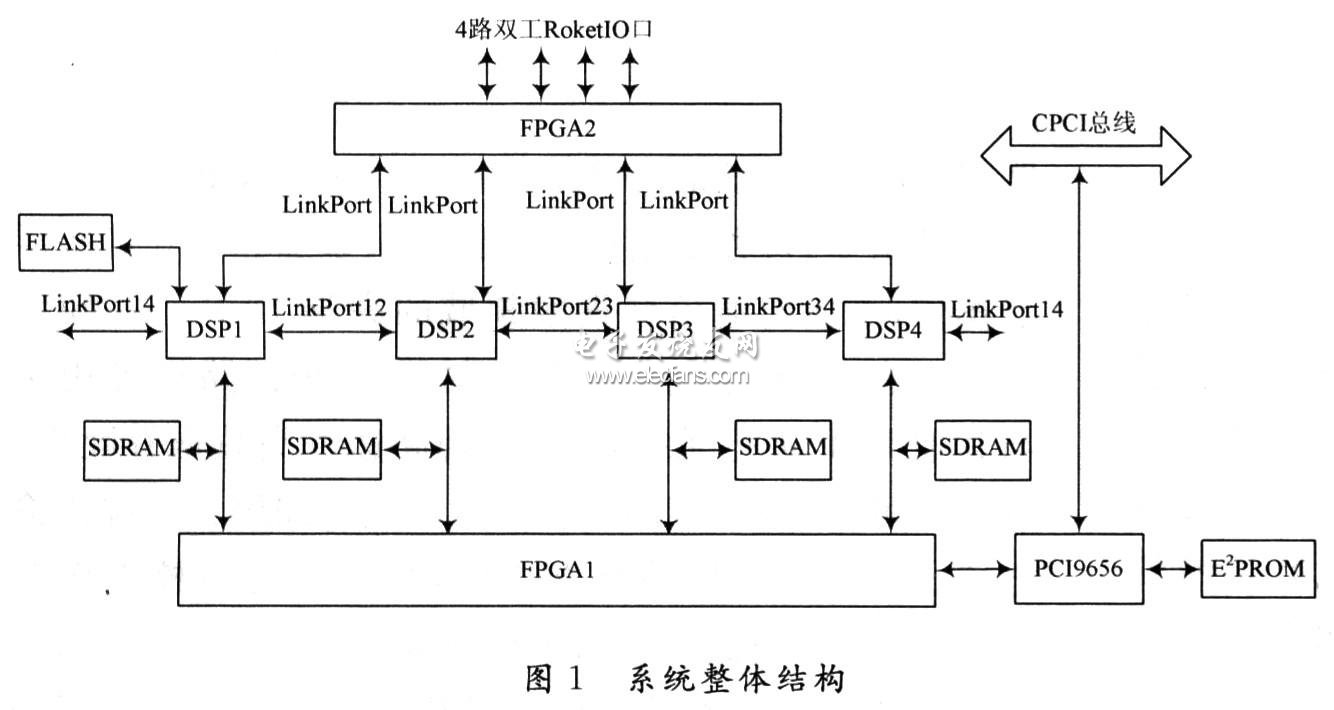

35 本文研究了一種相控陣脈沖多普勒雷達信號處理板的設計及實現(xiàn)。設計基于ADSP21161N組成多處理器系統(tǒng),具有針對相控陣的多通道處理能力,可實時實現(xiàn)脈沖多普勒雷達信號處理中視

2010-01-12 21:39:44 48

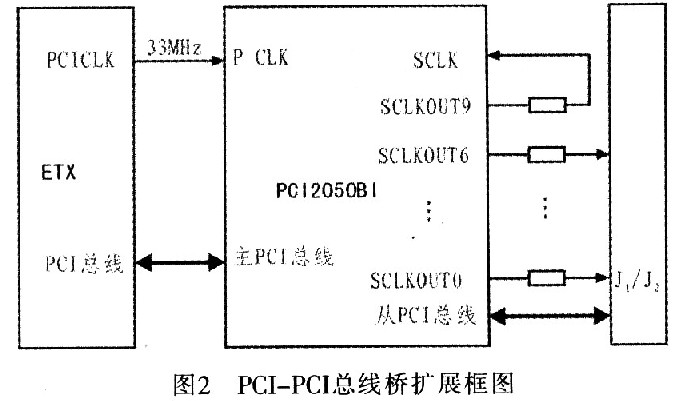

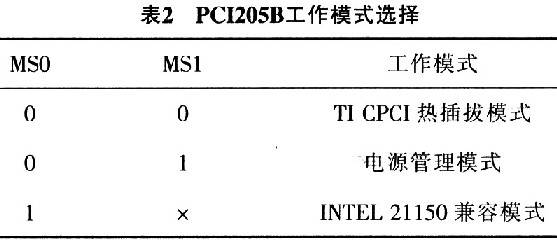

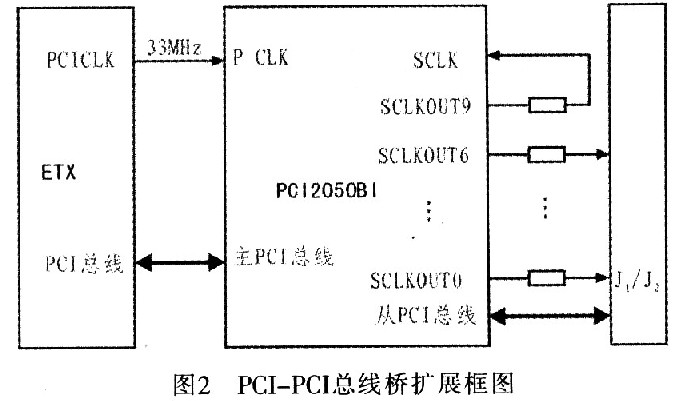

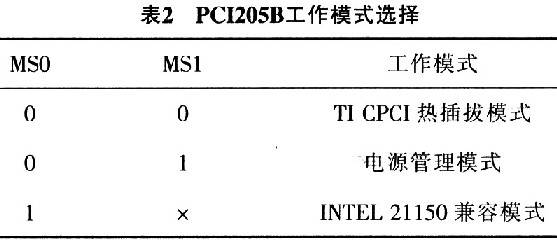

48 提出一種基于CPCI總線插槽的4網(wǎng)口卡的設計方案。運用Intel公司的Intel82551以太網(wǎng)控制器和TI公司PCI2050B PCI-PCI橋器件實現(xiàn)4路10/100 Mb/s自適應網(wǎng)口,重點介紹PCI總線橋的設計要點。該擴展

2010-07-10 15:58:28 28

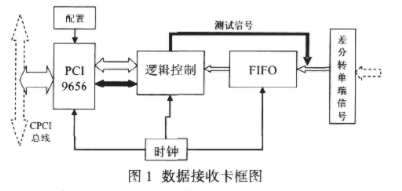

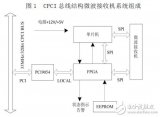

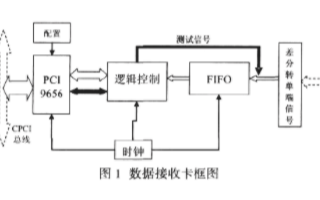

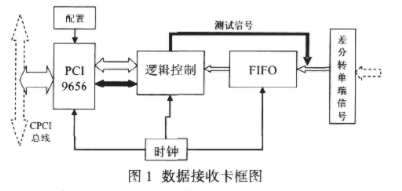

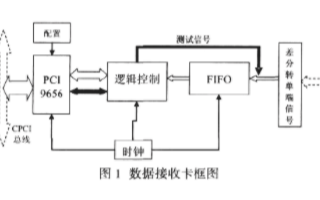

28 PCI 9656是PLX公司設計的一款高速PCI I/O芯片,可應用于66MHz、64bit PCI和CompactPCI總線。文章簡述了PCI 9656的主要功能,介紹了一種應用PCI 9656的CompactPCI數(shù)據(jù)接收卡設計。設計中采用MAXII系

2010-08-06 16:15:13 26

26 基于PCI總線數(shù)字信號處理機的硬件設計

以INTEL公司為主推出的PCI總線規(guī)范。采用PCI總線設備所具有的配置空間以及PCI總線通過橋接電路與CPU相連的技

2009-03-30 12:21:39 566

566

什么是CPCI

Compact PCI是標準PCI總線的工業(yè)版本,采用了抗震的Eurocard封裝。插孔連接器被設計成從正面裝進機架安裝系統(tǒng)。由PICMG指導的

2009-06-13 23:39:28 11783

11783 摘 要 :PCI是一種高性能的局部總線規(guī)范,可實現(xiàn)各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現(xiàn)PCI總線接口的

2009-06-20 13:13:28 936

936

摘 要: 以自行研制開發(fā)的PCI高速總線背板為背景,系統(tǒng)地論述了PCI總線的仲裁機制、總線的缺省占用、仲裁信號協(xié)定及優(yōu)先級仲裁算法,給出了采用EPLD實現(xiàn)仲裁器功能的編程設計

2009-06-20 13:32:20 961

961

基于CPCI總線10/100 Mb/s以太網(wǎng)卡的設計與實現(xiàn)

0 引 言??? 基于PCI總線的以太網(wǎng)控制器是現(xiàn)在以致將來網(wǎng)絡應用方面的一個主要發(fā)展方向。8位ISA網(wǎng)卡目前已

2009-11-11 16:42:25 1161

1161

基于CPCI總線的通用FPGA信號處理板的設計

?隨著雷達信號處理技術的不斷發(fā)展以及現(xiàn)代國防對雷達技術的需求,系統(tǒng)對雷達信號處理的要求也越來越高,需要實時處

2009-11-28 15:07:38 922

922

Compact PCI(簡稱CPCI)總線是“PCI總線工業(yè)計算機制造商組織”推出的一種工業(yè)計算機總線標準,近年來應用發(fā)展最為迅速。它由PC機上的通用總線PCI發(fā)展而來,既有PC

2010-07-21 09:11:40 4981

4981

以太網(wǎng)(Ethernet)作為應用最廣泛的局域網(wǎng)技術異軍突起,已經(jīng)迅速走向工業(yè)自動化控制領域的前臺。CPCI總線系統(tǒng)插槽有限,設計基于CPCI總線的多網(wǎng)口卡可節(jié)省空間,又可以滿

2010-09-10 09:56:34 1601

1601

摘要:針對現(xiàn)代雷達信號處理,介紹了CPCI總線信號處理模塊與主機間的通信方法,分析了Win2000下WDM驅動程序的開發(fā)。借助Win2000操作系統(tǒng),靈活組建了多板卡通用信號處理平臺,可以滿足不同信號處理任務需求。 關鍵詞:信號處理 WDMC PCI 并行處理

2011-02-27 22:42:08 70

70 本文設計的系統(tǒng)采用PLX公司生產(chǎn)的CPCI協(xié)議轉換芯片PCI9054,通過Verilog HDL語言在FPGA中產(chǎn)生相應的控制信號,完成對數(shù)據(jù)的快速讀寫,從而實現(xiàn)了與CPCI總線的高速數(shù)據(jù)通信。

2011-07-16 09:56:33 2027

2027

本文設計的系統(tǒng)采用PLX公司生產(chǎn)的CPCI協(xié)議轉換芯片PCI9054,通過Verilog HDL語言在FPGA中產(chǎn)生相應的控制信號,完成對數(shù)據(jù)的快速讀寫,從而實現(xiàn)了與CPCI總線的高速數(shù)據(jù)通信。

2011-07-17 10:47:57 12055

12055

介紹了嵌入式系統(tǒng)中使用的基于CPCI總線的PowerPC主處理板的設計方法,以目前廣泛應用的G4系列RISC微處理器MPC7410作為核心處理器,以PC107作為控制器,PCI6150作為PCI-to-PCI橋,加上FPGA控制電

2011-07-22 10:53:29 2138

2138

本文利用TMS320C6416T內(nèi)部集成的32位、33MHz PCI主/從接口,給出了6U的CPCI信號處理板卡設計方案,并對其軟件設計特別是DSP的二次引導程序做了說明。

2011-08-25 14:07:10 2733

2733

本文首先介紹了多DSP共享總線的通用信號處理板卡的硬件結構,介紹了基于PCI9054的CPCI總線接口設計和FPGA控制的通用信號處理板的板間通信過程。深入討論了基于Windows2000系統(tǒng)的WDM驅動

2011-09-09 11:51:25 72

72 CPCI總線是一個開放式、國際性技術標準,由PCI總線工業(yè)計算機制造商組織PICMG(PCI Industrial Computer Manufacturer Group)負責制定和支持。CPCI總線具有嚴格的標準和規(guī)范,保證其具有良好的兼

2011-09-09 11:53:16 21

21 文中介紹了PCI9656的內(nèi)部結構和功能,討論了其WDM驅動開發(fā)過程,分析了其局部總線在進行DMA傳輸時的配置時序,提出了一些設計中需要注意的問題。實際應用結果表明,該總線接口性能穩(wěn)定

2011-10-19 14:56:51 31

31 通過在FPGA中編寫Verilog HDL語言控制CPCI協(xié)議轉換芯片,從而實現(xiàn)與CPCI總線之間的高速通信。實驗結果證明,該設計方案工作穩(wěn)定、傳輸速度快、數(shù)據(jù)準確,并可擴展到其他需要通過CPCI總線的

2011-12-07 14:22:06 51

51 文中介紹一種基于

CPCI總線的無源

雷達終端系統(tǒng),滿足了無源

雷達高速、大容量數(shù)據(jù)

處理及傳輸?shù)囊蟆?/div>

2012-04-20 10:59:52 45

45 本文提出了一種兩級測試系統(tǒng)的設計思路,給出了在較寬的范圍內(nèi)兼容不同接口電平的脈沖信號檢測系統(tǒng)的設計方案,采用標準CPCI總線接口設計,具有良好的兼容性和擴展性,適用于產(chǎn)

2013-01-04 14:29:44 3337

3337

實時處理的專用處理器,是實現(xiàn)實時數(shù)字信號處理的有力工具。DSP目前廣泛應用于模式識別,數(shù)字通信,信號處理,工業(yè)控制等領域。TI公司的TMS320C54X系列DSP有著以下的特點:采用先進的修正增強型哈佛結構,片內(nèi)共有8條總線(1條程序存儲器總線,3條數(shù)據(jù)存儲器總線和4條地址總線);高度并行

2017-10-24 16:57:52 0

0 提出了一種基于FPGA的雷達回波實時模擬器的實現(xiàn)方法。該模擬器采用cPCI 標準總線,以FPGA 為核心計算單元,配有高速數(shù)模、模數(shù)轉換模塊,可實現(xiàn)雷達回波信號實時在線注入模擬。該模擬器可實現(xiàn)多種

2017-11-18 13:00:01 2444

2444

CPCI 總線信號到LOCAL 總線信號的轉換是基于PCI9054芯片實現(xiàn)的。PCI9054 是PLX 公司生產(chǎn)的一款基于PCI2.2總線規(guī)范的通用接口芯片,是32 位、33MHZ的PCI總線

2018-07-25 11:02:00 2495

2495

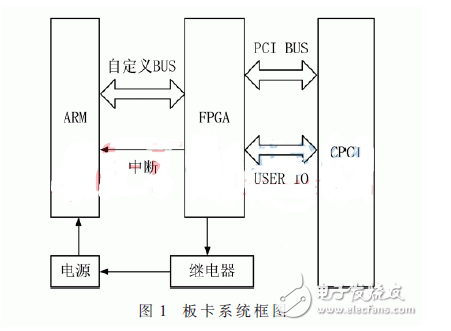

本文提出了一種基于FPGA的CPCI系統(tǒng)的設計和實現(xiàn),使用廉價FPGA芯片實現(xiàn)CPCI通信協(xié)議,同時利用FPGA的可編程特性實現(xiàn)電源控制、靈活中斷、外部觸發(fā)、外部通信等特殊應用的功能,解決了CPCI協(xié)議經(jīng)過CPCI橋時的沖突問題。

2019-01-06 11:37:13 2443

2443

據(jù)傳輸速率為132~264MB/s,是目前使用較為廣泛的一種總線。在高速信號的實時處理中,利用PCI總線將采集數(shù)據(jù)直接傳送到微機系統(tǒng)內(nèi)存,可有效解決數(shù)據(jù)的實時傳輸和存儲,為信號的實時處理提供方便。利用PCI

2019-01-28 18:06:01 355

355 CPCI總線是一個開放式、國際性技術標準,由PCI總線工業(yè)計算機制造商組織PICMG(PCI Industrial Computer Manufacturer Group)負責制定和支持。CPCI

2020-04-09 10:05:34 3001

3001

是2500幀/s的高速CMOS相機天文圖像數(shù)據(jù)的實時采集和處理,并由橋接芯片PCI9656通過PCI總線傳輸給PC機進行進一步處理。

2021-02-04 16:46:00 16

16 為了提高航空航天領域對信號處理、傳輸?shù)膶崟r性及可靠性,以Cyclone III系列EP3C40F324I7為核心處理器,設計了一種基于CPCI總線的多功能通信卡。結合高效的FPGA算法,設計出一款實時性強、可靠性高的多功能通信卡。經(jīng)測試使用,該多功能通信卡各項性能指標均達到要求,已投入實際應用中。

2021-04-05 08:32:00 3376

3376

PCI 9656支持66Mhz、64bit的PCI R2.2規(guī)范,提供了兼容PICMG 2.1 R2.0規(guī)范的CompactPCI Hot Swap接口,其局部總線達到66MHz、32bit(支持

2021-03-23 11:42:57 2114

2114

設計了一種基于CPCI總線標準的PMC接口載板。載板以FPGA為核心,集成了CPCI接口模塊和DPRAM(雙口RAM)模塊,CPCI接口模

2021-05-05 16:56:00 3055

3055

處理,工業(yè)控制等多行業(yè)的廣泛應用,并出現(xiàn)PCI-E。CPCI,PXI等多個擴展改良版本。PCI總線支持其即插即用,中斷共享,高速數(shù)據(jù)傳輸?shù)裙δ埽兄鴱V闊的市場前景。

2021-05-19 09:50:44 3320

3320

基于CPCI總線的四通道總線通訊模塊設計

2021-06-22 16:58:19 16

16 基于CPCI總線的航天器通信信號設備故障檢測

2021-06-23 11:10:27 12

12 PCI總線的信號定義 PCI總線是一條共享總線,在一條PCI總線上可以掛接多個PCI設備。這些PCI設備通過一系列信號與PCI總線相連,這些信號由地址/數(shù)據(jù)信號、控制信號、仲裁信號、中斷信號等多種

2021-07-18 09:55:32 1981

1981 PCI總線的中斷機制 PCI總線使用INTA#、INTB#、INTC#和INTD#信號向處理器發(fā)出中斷請求。這些中斷請求信號為低電平有效,并與處理器的中斷控制器連接。在PCI體系結構中,這些中斷信號

2021-07-18 10:10:40 2450

2450 Component Interconnect)是Intel公司推出的一種高性能32/64位局部總線,最大數(shù)據(jù)傳輸速率為132~264MB/s,是目前使用較為廣泛的一種總線。在高速信號的實時處理中,利用PCI總線將采集數(shù)據(jù)直接傳送到微機系統(tǒng)內(nèi)存,可有效解決數(shù)據(jù)的實時傳輸和存儲,為信號的實時處理提供方便。利用PCI總線進

2023-10-07 14:55:02 289

289 電子發(fā)燒友網(wǎng)站提供《基于CPCI總線CPU主控模塊的設計與實現(xiàn).pdf》資料免費下載

2023-10-18 11:09:18 0

0 ? 產(chǎn)品概述?鍵石 CPCI6320 是一款高品質(zhì)的視頻播放板,該板基于 CPCI 總線,采用 Sigma Designs 公司的 EM8470 流處理器,支持多種音視頻格式,兼容即插即用(PNP)。?在安裝和使用鍵石 CPCI6320 型視頻播放板前,建議您先閱讀本手冊,以便了解如何安裝和使用該產(chǎn)品。?

2023-12-11 14:40:51 0

0 正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論