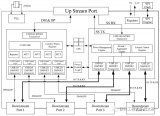

該系統主要實現USB的接口功能,通過它,外設與計算機之間可以實現USB方式的連接。外設接口1用于DMA方式數據的傳送,可與CCD攝像頭等設備相連。外設接口2采用了標準的IDE接口方式,可直接于硬盤等大容量存儲器相連,傳輸海量數據,也可以通過接口轉換,與其他功能的外設相連,具有較廣的適用性。

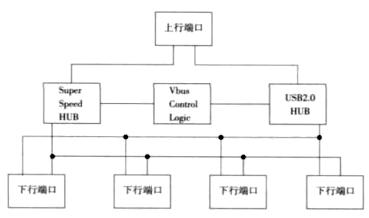

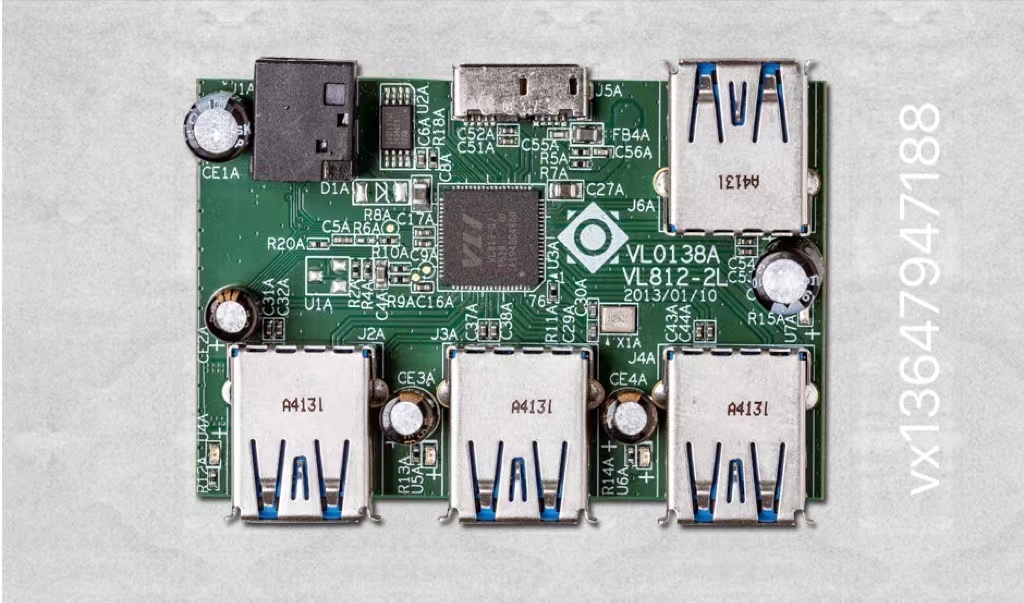

下面說明了此多功能USB接口電路的框圖:

這個框圖顯示了兩種接口方案:普通模式和DMA模式。

(1)方案一:普通模式

圖4-2是該USB接口電路普通模式的框圖,該框圖說明了連接外設的一種簡單模式,所有寄存器和數據的讀寫都是通過8051 的I/O 來仿真的,因此數據吞吐速率較低,適合間歇式數據的傳送。

(2)方案二:DMA模式

數據傳送以DMA方式,直接由D12傳送到計算機里,MCU只完成DMA的初始化工作,傳輸速度快,適合于視頻數字信號等高速實時傳送。

系統詳細的電原理圖和電路板結構圖參見附錄。

4.2 系統主要部件及電路

該系統主要由89C51控制電路、PDIUSBD12 接口電路、數據選擇電路、串并轉換電路、掛起復位電路、IDE擴展接口電路等組成,下面分述各部分的功能和特點。

4.2.1 89C51控制電路

89C51是該接口電路的控制核心,其中P0,P2口用做16位數據I/O口,P1,P3口用做控制。

89C51的晶振頻率為24MHz,每個機器周期為0.5us.

4.2.2 PDIUSBD12 接口電路

PDIUSBD12是一個性能優化的USB器件,通常用于基于微控制器的系統并與微控制器通過高速通用并行接口進行通信,也支持本地DMA傳輸。該器件采用模塊化的方法實現一個 USB接口,允許在眾多可用的微控制器中選擇最合適的作為系統微控制器,允許使用現存的體系結構并使固件投資減到最小。這種靈活性減少了開發時間、風險和成本,是開發低成本且高效的USB外圍設備解決方案的一種最快途徑。 PDIUSBD12完全符合USB1.1規范,也能適應大多數設備類規范的設計,如成像類、大容量存儲類、通信類、打印類和人工輸入設備等,因此,PDIUSBD12 非常適合做很多外圍設備,如打印機、掃描儀、外部大容量存儲器( Zip驅動器)和數碼相機等。現在用SCSI實現的很多設備如果用 USB來實現可以直接降低成本。

PDIUSBD12掛起時的低功耗以及LazyClock輸出符合ACPI 、OnNOW和USB電源管理設備的要求。低功耗工作允許實現總線供電的外圍設備。

PDIUSBD12還集成了像SoftConnect、GoodLink、可編程時鐘輸出、低頻晶振和終端電阻等特性。所有這些特性都能在系統實現時節省成本,同時在外圍設備上很容易實現更高級的 USB功能。

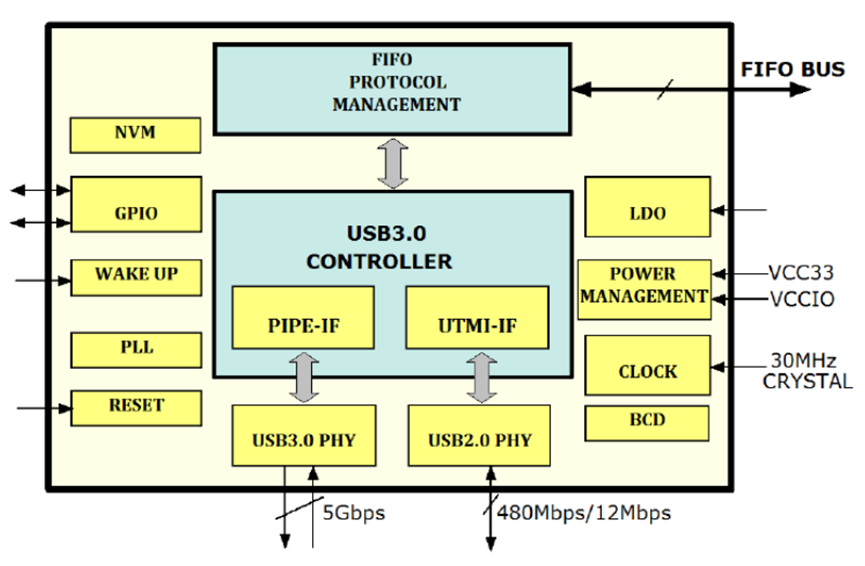

(1)內部結構

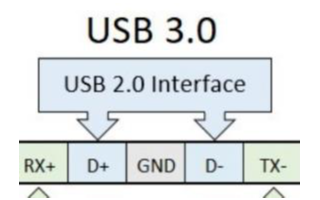

① 模擬收發器。集成的收發器直接通過終端電阻與USB電纜接口。

② 電壓調整器。片上集成的1個3.3 V電壓調整器為模擬收發器供電,也提供連接到外部1.5 kΩ上拉電阻的輸出電壓。作為選擇,PDIUSBD12提供集成1.5 kΩ上拉電阻的SoftConnect技術。

③ PLL。片上集成1個6~48 MHz的倍頻PLL(鎖相環),允許使用6 MHz的晶振,EMI也由于使用低頻晶振而減小。PLL的工作不需要外部器件。

④ 位時鐘恢復。位時鐘恢復電路用4倍過采樣原理從輸入的USB 數據流中恢復時鐘,能跟蹤USB規范中指出的信號抖動和頻率漂移。

⑤ PHILIPS串行接口引擎PSIE。PHILIPS的SIE完全實現USB協議層。考慮到速度,它是全硬件的, 不需要固件(微程序)介入。這個模塊的功能包括:同步模式識別、并 /串轉換、位填充/不填充、CRC校驗、PID確認、地址識別以及握手鑒定。

⑥ SoftConnect。高速設備與USB的連接是靠把D+通過1個1.5 kΩ的上拉電阻接到高電平來建立的。在PDIUSBD12中,這個上拉電阻是集成在芯片 內的,缺省是沒有連接到VDD,這個連接是靠外部 MCU發一個命令來建立的。這使得系統微處理器可以在決定建立 USB連接之前完成初始化。重新初始化USB總線連接也可以不用拔掉電纜來完成。

⑦ GoodLink。GoodLink是靠一個引腳接發光二極管實現的。在 USB設備枚舉時LED指示燈將立即閃亮;當PDIUSBD12被成功枚舉并配置時, LED指示燈將會始終亮;經過PDIUSBD12的USB數據傳輸過程中, LED將一閃一閃,傳輸成功后LED熄滅;在掛起期間,LED熄滅。這種特性可以使我們知道 PDIUSBD12的狀態,方便電路調試。

⑧ 存儲器管理單元MMU和集成RAM。MMU和集成RAM能緩沖USB(工作在 12Mb/s)數據傳輸和微控制器之間并行接口之間的速度差異,這允 許微控制器以自己的速度讀寫USB包。

⑨ 并行和DMA接口。并行接口容易使用、速度快并且能直接與主微控制器接口。對于微控制器,PDIUSBD12可以看成是一個有8位數據總線和1位地址線的存儲設備。 PDIUSBD12支持多路復用和非多路復用的地址和數據總線。在主端點(端點 2)和局部共享存儲器之間也可使用DMA(直接存儲器存取)傳輸。它支持單周期模式和塊傳送模式 兩種DMA傳輸。

(2)PDIUSBD12引腳說明

(3)PDIUSBD12的典型連接

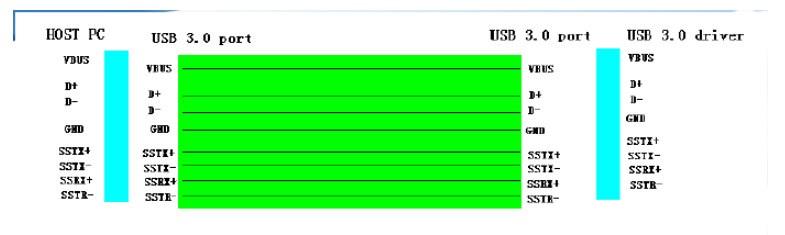

PDIUSBD12與80C51的連接電路如 圖4-6 所示。在這個例子中, ALE始終接低電平,說明采用單獨地址和數據總線配置。A0 腳接80C51的任何I/O引腳,控制是命令還是數據輸入到PDIUSBD12 。80C51的P0口直接與PDIUSBD12的數據總線相連接,CLKOUT 時鐘輸出為80C51提供時鐘輸入。

(4)PDIUSBD12的DMA 傳輸

直接存儲器尋址 允許在主端點和本地共享存儲器間實現數據塊的有效傳輸.使用DMA控制器,PDIUSBD12 的主端點和本地共享存儲器間的數據傳輸可自主進行而不需要本地CPU 的干預.要處理任何DMA傳輸,本地CPU 從主機接收必要的建立信息并對DMA控制器進行相應的編程.典型的對DMA控制器的傳輸模式、字節計數寄存器和地址計數器進行正確的編程。在該模式下, PDIUSBD12 發出請求時開始傳輸,當字節計數器減少為零時終止。在DMA 控制器編程之后,本地CPU 在初始化傳輸時將PDIUSBD12 中的DMA使能位置位。

PDIUSBD12 可編程為單周期DMA或突發模式DMA。在單周期DMA 中,DMREQ在每單個應答后直到被DMACK_N 重新激活之前保持無效。在突發模式DMA 中,DMREQ 在器件中突發編程時一直保持有效。該過程持續到PDIUSBD12 通過EOT_N 接收到一個DMA 終止信息。這時產生一個中斷指示本地CPU ,DMA操作已經完成。

在DMA 讀操作時,DMREQ 僅當緩沖區完全表示主機成功的發送了一個信息包到PDIUSBD12 時才有效。由于具有雙緩沖配置主機可以在第一個緩沖區被讀出時對第二個緩沖區進行填充。這種并行的處理有效的增加了數據吞吐量。當主機沒有完全填滿緩沖區的情況下(單向ISO 配置時小于64 或128 字節)。DMREQ 會在緩沖區的最后一個字節時無效,而不管當前的DMA突發計數。在更新了DMA突發計數的下一個包發送時,DMREQ 再次被激活。

DMA的寫操作與之相似,當緩沖區未裝滿時,DMREQ 一直有效。當緩沖區填滿時,在下一個IN 標志將信息包送入主機。當傳輸完成之后DMREQ 變為無效。同樣的,雙緩沖配置在這也改善了數據的吞吐量。在非同步傳輸中(批量模式和中斷),在數據被發送到主機之前,緩沖區需要通過DMA寫操作完全裝滿。唯一的例外是,在DMA傳輸結束時,EOT_N 接收的信號將會停止DMA寫操作并且在下一個IN 標志置位時將緩沖區的內容傳送到主機。

在同步模式中,本地CPU 和DMA 控制器必須保證它們在一個USB 幀(1ms )中能夠吞吐的最大信息包的規模。DMACK_N 的激活將自動選擇主端點(端點2 )而不管當前選擇的端點。PDIUSBD12的DMA操作可通過普通的I/O 對其它端點的存取實現交叉存取。DMA操作可通過以下方式終止:復位DMA使能寄存器位或EOT_N 加上DMACK_N 以及RD_N/WR_N的激活。

PDIUSBD12 支持單地址模式中的DMA傳輸,也可以在DMA 控制器的雙地址模式中工作。在單地址模式中,DMA 通過DREQ ,DMACK_N,EOT_N,WR_N 和RD_N 控制線實現傳輸。在雙地址模式中,DMREQ,DMACK_N和EOT_N未用,取而代之的是CS_N,WR_N和RD_N控制信號。需要遵循 PDIUSBD12的I/O 模式傳輸協議。在讀周期中對DMAC 信號源進行訪問,在寫周期對目標進行訪問。傳輸需要兩個單獨的總線周期來儲存暫存在DMAC 中的數據。

4.2.3 DMA方式數據傳輸電路

上面詳細介紹了PDIUSBD12芯片的原理和工作方式,下面將介紹接口電路板工作在DMA方式的原理。該傳輸方式的原理框圖參看圖4-3。

當外設接口1接入要求DMA傳輸的設備,51單片機向D12發出DMA傳送的指令,并通過控制口線使157數據選擇電路里74164傳送過來的并行數據直接與D12的并行接口相連,不在進入51單片機,在完成了對D12 DMA傳送初始化以后,MCU不再控制傳送,而由計數器滿8向D12發送一個讀信號,使D12 讀取164內存儲的8個字節的數據,如此反復,整個傳輸過程由硬件完成,不受MCU 的速率限制,從而實現了DMA傳輸。

此工作方式適用于視頻數字信號的傳輸,下面是連接CCD攝像頭的電路示意圖:

CCD_IN為經過A/D轉化或二值化處理的視頻數字信號,CCD_CLK1為脈沖同步信號,CCD_CLK2為行同步信號,CCD_CLK3為場同步信號。計數器對CCD_CLK1進行計數,滿8個脈沖向D12的讀端發一個低電平,通知D12對164里面的數據進行讀取。

4.2.4 數據選擇電路

數據選擇電路是由兩片74H157搭建而成,數據選擇DATA_SEL端連到了51的控制口線上,由51控制D12的并行數據I/O口是和51的P0口相連還是和74HC93串并轉換輸出的并行數據線相連,從而到達了數據選擇的作用。

4.2.5 串并轉換及計數器電路

電路中74HC164起了串并轉換的作用,在DMA工作方式下,通過接入數據同步脈沖,把外設接口1送入的串行數據轉化成并行數據,供D12直接讀取。

計數器74HC93負責對CCD_CLK1進行計數,滿8個脈沖向D12的讀端發一個低電平,通知D12對164里面的數據進行讀取。

電子發燒友App

電子發燒友App

評論