?

ST-BUS總線規范

在電信設備中,模塊互連普遍采用總線架構,其中應用最為廣泛的是ST-BUS(即Serial Telecom BUS,串行電信總線)。電信芯片制造商Zarlink半導體公司根據電信模塊化應用的需要對ST-BUS的信號與時序規范作了明確的定義,該總線在很大程度上簡化了不同模塊間的通信方式,可以傳輸包括音頻、視頻、控制信息等在內的數據信息。

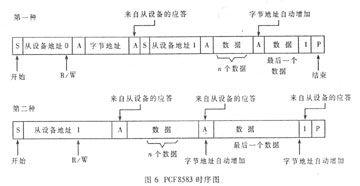

由定義知,ST-BUS是一種傳輸數字信息的高速同步串行通信總線,其總線信號包括幀同步、位時鐘和串行數據,幀同步信號是一個負脈沖,分為兩種類型:類型0的 F0 同步脈沖僅出現在幀開頭的一個位時鐘周期內,它決定著總線上各部件何時開始收或發一幀信息數據流;類型1的 F1 同步脈沖也出現在幀開頭且需維持8個位時鐘周期(即一個時隙周期),在此期間總線上各部件 同時也在收或發信息數據流,相比于類型0,類型1同步方式應用較少。另外,考慮到模塊間通信速率的匹配,ST-BUS定義了四種標準時鐘頻 率 ,即 16.384MHz、8.192MHz、4.096MHz和2 .048MHz,均可用作部件的內部時鐘,且同一時刻只能選擇其一,而自適應系統則采取自動選擇 模式。除了常用的基準時鐘2.048MHz外,其余時鐘頻率總是對應數據速率的兩倍,即ST-BUS支持的最大數據速率為8.192Mbps。假設ST-BUS速據速率為2.048M bps,則時鐘頻率可在2.048MHz與4.096MHz中任取其一。ST-BUS的一個完整 幀周 期為12 5μs,每幀又根據不同數據傳輸速率分為不同的時 隙數。不過,為了與E1信號時隙一一對應,實際應用中ST-BUS常采用每幀32時隙的信號方式。

由于通信系統越來越復雜,為了提高設備兼容性且便于系統或模塊升級,電信設備廣泛采用模塊化設計思想和方法,而ST-BUS正是便于將各功能模塊聯接起來協調工作的總線標準,所以模塊只要具備ST-BUS總線接口就能方便地嵌入特定通信設備。

ST-BUS收發電路與CPLD邏輯設計

ST-BUS收發電路設計

為了實現完整的ST-BUS收發模塊,首先介紹一下ST-BUS收發電路設計。

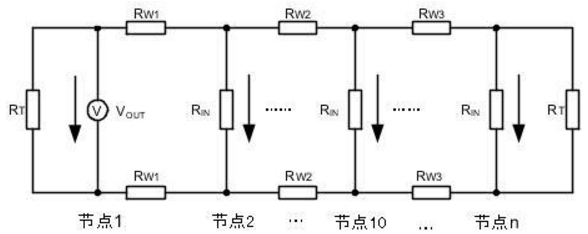

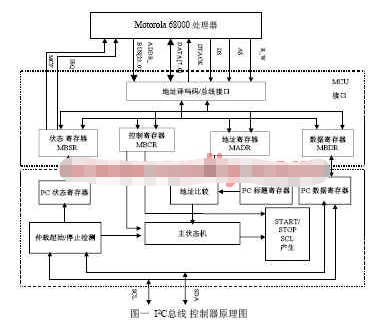

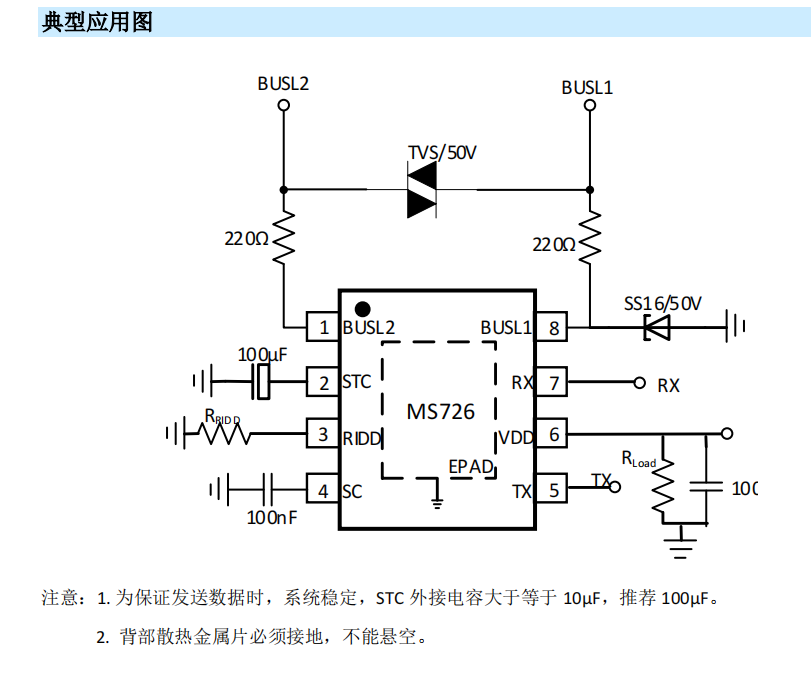

為ST-BUS收發模塊的電路原理圖。這里,ST-BUS收發模塊功能電路以CPLD作為核心元件,CPLD采用全球第二大可編程器件廠商Altera公司MAX7000B系列的 EPM7128SLC84-15(128個宏單元,PLCC84封裝)。

同時考慮到調試與驗證方便,電路模塊采用一個Atmel公司的AT89C51單片機(DIP40封裝,文中不作詳細討論)作為外部控制器。單片機通過四線制SPI接口設置收發模塊的工作模式、時隙參數等,也可通過SPI或并口P0接口讀(或寫)ST-BUS收發模塊接收(或發送)的數據,并通過RS-232C接口與計算機通信。另外,ST-BUS收發模塊還設置了2個中斷輸出信號,并在分別連接到單片機的中斷輸入引腳 INT0 和 INT1 。因此,單片機也可以采取中斷方式來讀取ST-BUS收發模塊接收到的數據。

單片機的外接晶體11.059MHz;CPLD片上系統時鐘由外部4.096MHz有源晶體振蕩器提供,采用10引腳雙列插座的JTAG接口實現CPLD的在線編程;RS-232C與TTL接口電平轉換采用MAXIM公司的MAX232ACPE。

ST-BUS收發模塊設計

ST-BUS收發模塊的功能是實現ST-BUS總線串行數據的可靠收發,接下來就探討 F0 同步模式下ST-BUS總線接收與發送的模塊設計。

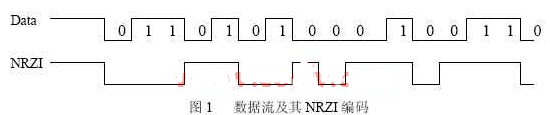

ST-BUS總線數據收發規則為:發送端在時鐘C2上升沿時發送數據,而接收端在C2下降沿時采樣并讀取數據,且 F0 同步脈沖在第0時隙開始的第一個C2上升沿處保持低電平。需要說明的是,實際應用中ST-BUS收發模塊的一端接到各種接口的數據交換單元,且通過外部控制接口設置各路數據所占用的時隙位置參數,不過,在不影響本文討論ST-BUS收發模塊設計的情況下,這里暫不考慮收發數據與其它接口的交換部分,并假定收發模塊各路數據通道占用固定的時隙通道(實際上,這里是由單片機軟件設置的)。

另外,根據時鐘等信號的提供方式,時序電路模塊的工作模式常分為主動模式和被動模式兩種。若電路模塊所需時鐘和同步信號均來自外部,該模塊就處于被動模式;相反,若時鐘和同步信號由模塊內部產生,該模塊就處于主動模式。下面的討論假設模塊處于時鐘與幀同步均由外部提供的被動模式,但討論結果對主動模式同樣成立。

(一)接收模塊

ST-BUS接收模塊的功能原理框圖。從本質上講,ST-BUS接收模塊的功能是根據所設置的ST-BUS時隙位置接收所需數據,再通過特定接口送出接收模塊并維持至少一個位時鐘周期。模塊接收數據時,由于發送端(見后)在上升沿處建立ST-BUS總線上的數據信號,此時位時鐘C2上升沿應僅觸發狀態轉換及計數器計數,因此接收端應在數據穩定期間采樣,即在C2下降沿處讀取串行數據。因此,雙通道接收模塊用Verilog HDL實現時可采用兩個always語句加以描述,部分代碼如下(為了簡化起見,信號和常數聲明略,下同)。

第一個always語句內容為:

if(!f0)begin //同步檢測,同步則置標志并復位計數器

f0_flag<=1;bitcounter<=bitsofbyte-1;bytecounter<=0;end

else if(f0_flag)begin //判斷當前是否處于同步狀態

case(bitcounter) //時隙內位計數處理

0:begin bitcounter<=bitsofbyte-1; //當前時隙末位則位計數器復位

if(bytecounter==(bytes_per_frame-1)) //檢查是否幀末時隙

begin bytecounter=0; //時隙計數復位

if(f0)f0_flag<=0;end / /無同步信號則清除同步標志

else bytecounter<=bytecounter+1;end //非幀末時隙則遞增

default:bitcounter<=bitcounter-1; //正常接收數據時計數器遞減

endcase end

位時鐘C2下降沿觸發數據鎖存并作接收處理,則第二個always語句內容為:

if(f0_flag)begin if(bytecounter==byte_pos1)//檢查當前時隙是否接收數據

begin receive2_flag<=0;din1<=din1<<1;din1[0]<=dr;

if(bitcounter==0)receive1_flag<=1;end

else if(bytecounter==byte_pos2) //多通道接收(同上)

……

end

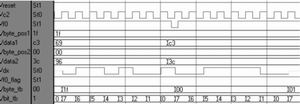

在Altera公司提供的Quartus II 5.0 SP1集成開發環境下,基于MAX7000S系列的CPLD器件EPM7128SLC84-15對上述雙通道ST-BUS接收模塊作綜合,占用資源為27個LC,占用率為21%。再做綜合后時序仿真,結果如圖4(a)。因未討論單片機的控制接口,仿真的通道設置如下:第一通道為0時隙,第二通道為31時隙,這樣設置也是為了驗證幀切換問題。由仿真結果可以看出,接收模塊的功能和時序正確。

(二)發送模塊

ST-BUS發送模塊的功能原理框圖。從本質上講,ST-BUS發送模塊的功能是按照所設置的時隙將待發數據變換為特定的串行格式發送,即將數據信號轉換為ST-BUS總線信號。由前述,發送端在位時鐘C2的上升沿處可以既轉換狀態又發送數據,因此,雙通道發送模塊用Verilog HDL實現時可以采用一個always語句加以描述,相應的部分代碼如下:

if(!f0)begin f0_flag<=1;bitcounter<=bitsofbyte-1;bytecounter<=0;

if(byte_pos1==0) //時隙0為第一通道,發送數據data1

begin dx<=data1[7];dout1<=data1<<1;dout2<=data2;end

else if(byte_pos2==0) //時隙0為第二通道,發送數據data2

……

else dx<=1'bZ; end //非選定時隙,則輸出高阻釋放總線

else if(f0_flag)begin case(bitcounter)

0:begin

…… //狀態轉換,類似于接收模塊

if(bytecounter==byte_pos1-1) //發送第一通道數據

begin dx<=dout1[7];dout1<=dout1<<1;end

else if(bytecounter==byte_pos2-1)//發送第二通道數據

……

else dx<=1'bZ;end

default:begin bitcounter<=bitcounter-1;

…… //同上,發送數據

end endcase end

采用與接收模塊類似的方法,在Quartus II 5.0 SP1開發環境下基于EPM7128SLC84-15器件對雙通道發送模塊作綜合,占用資源為25個LC,占用率為20%。后時序仿真,結果如圖4(b)。仿真時,為了說明雙通道發送模塊的發送時序與通道設置的順序無關,與接收模塊的通道設置相反,發送模塊的第一通道設置為31時隙,第二通道設置為0時隙。由仿真結果可見,發送模塊的功能和時序也正確。

接收和發送模塊的功能原理框圖可知,兩個模塊之間的差異只有數據收發部分,兩個模塊的同步檢測、時隙定位以及位定位都可以共用,因此兩個模塊可以合并為一個收發模塊,如圖3(c)所示,能節省部分器件資源。從綜合結果來看,如果收發模塊相對獨立,那么資源占用將是27+25=52個LC,占用率高達41%。而接收與發送模塊合并后的收發模塊,占用資源35個LC,占用率27%。顯然,有效地節省了CPLD的LC資源。

上面討論并沒有嚴格區分被動模式和主動模式,但是,前面的電路設計已考慮到了雙模式的驗證,CPLD器件的外接晶體振蕩器可以讓ST-BUS收發模塊工作于主動模式。當工作于主動模式時,收發模塊會自己產生時鐘和幀同步等信號,并提供給ST-BUS總線上的其它部件。相反,當工作于被動模式時,收發模塊的收發部分會屏蔽掉本地時鐘,而由外部ST-BUS總線提供時鐘。

基于所選定的CPLD器件EPM7128SLC84-15分析收發模塊最高工作性能可知,接收模塊和發送模塊的最高工作頻率均大于20MHz。這說明,所設計模塊的工作頻率高于前面所述C2幾種工作頻率的最大值,也就是說在C2的各頻率條件下,ST-BUS收發模塊都是適用的。

結束語

文中所討論的ST-BUS收發模塊的實現電路及CPLD內部邏輯設計已成功應用于某專用通信設備的E1接口板,運行性能穩定。基本文中設計的收發模塊,在多種不同規模的可編程器件上已成功實現了ST-BUS與RS-232等多種標準接口單元以及部分自定義接口的順利對接,完成各種 接口與ST-BUS總線間的數據復接通信,工作性能穩定可靠。

電子發燒友App

電子發燒友App

評論