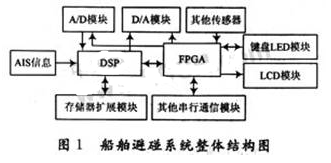

摘要:在雷達信號處理、數字圖像處理等領域中,信號處理的實時性至關重要。由于FPGA芯片在大數據量的底層算法處理上的優勢及DSP芯片在復雜算法處理上的優勢,DSP+FPGA的實時信號處理系統的應用越來越廣泛。ADI公司的TigerSHARC系列DSP芯片浮點處理性能優越,DSP的DSP+FPGA處理系統正廣泛應用于復雜的信號處理領域。同時在這類實時處理系統中,FPGA與DSP芯片之間數據的實時通信至關重要。

TigerSHARC系列DSP芯片與外部進行數據通信主要有兩種方式:總線方式和鏈路口方式。鏈路口方式更適合于FPGA與DSP之間的實時通信。隨著實時信號處理運算量的日益增加,多DSP并行處理的方式被普遍采用,它們共享總線以互相映射存儲空間,如果再與FPGA通過總線連接,勢必導致FPGA與DSP的總線競爭。同時采用總線方式與FPGA通信,DSP的地址、數據線引腳很多,占用FPGA的I/O引腳資源太多。而采用鏈路口通信不但能有效緩解DSP總線上的壓力,而且傳輸速度快,與FPGA之間的連線相對也少得多,故鏈路口方式更適合于FPGA與DSP之間進行實時數據通信。

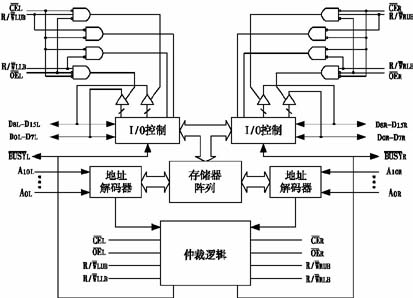

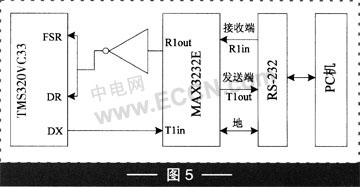

?

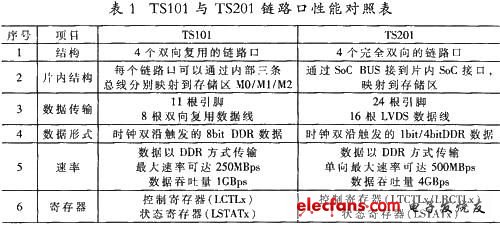

1 TS101和TS201的鏈路口分析與比較

TS101和TS210都是高性能的浮點處理芯片,目前兩者都廣泛應用于復雜的信號處理領域。TS201是繼TS101之后推出的新型芯片,核時鐘最高可達600MHz,其各類性能也相對優于TS101,而且TS201的鏈路口采用了低壓差分信號LVDS技術,功耗更低、抗噪聲性能更好。表1列出了兩種芯片鏈路口性能的詳細比較,其中TS101核時鐘工作在250MHz,TS201核時鐘工作在500MHz。

由于TS101收發端共用一個通道,所以只能實現半雙工通信。而TS201將收發端做成兩個獨立通道,可實現全雙工通信,理論上數據的傳輸速率可以提高一倍。雖然TS201的鏈路口收發通道獨立,但實際上二者的收發機制大體相同,都是靠收發緩存和移位寄存器收發數據。然而FPGA內部的鏈路口設計不必拘泥于此,只要符合鏈路口通信協議并達成通信即可。

2 FPGA與DSP的鏈路口通信

2.1 鏈路口通信協議分析

TS101的鏈路口共有11根引腳,通過8根數據線(LxDAT[7..0],這里x可以是0、1、2或3,代表TS101或TS201的0號-3號鏈路口中的一個,以下同)進行數據傳輸,并采用3根控制線(LxCLKOUT、LxCLKIN、LxDIR)來控制數據傳輸時鐘、通信的握于和數據傳輸方向。其中LxDIR為通知鏈路口當前工作狀態是接收或發送的輸出引腳,可懸空不用。TS201的鏈路口共24根引腳,接收和發送各12根引腳,通過LVDS形式的數據線(LxDAT_P/N[3..0])和時鐘線(LxCLK_P/N)進行數據傳輸,并采用LxACK和LxBCMP#(‘#’代表信號低有效)來通知接收準備好和數據塊傳輸結束。

采用FPGA與DSP通過鏈路口通信的關鍵是令雙方通信的握手信號達成協議,促使數據傳輸的進行。實際上,如果考慮TS201的LVDS信號形式已經被轉換完畢,則TS101和TS201鏈路口傳輸的數據形式是一樣的,都是時鐘雙沿觸發的DDR數據,并且每次傳輸的數據個數都是4個長字(即128bit)的整數倍。鑒于以上兩種芯片鏈路口數據的共同點,所以采用FPGA與兩類芯片通信時,接收和發送的數據緩存部分的設計應該是很相近的,只是通信握手信號部分的設計應當分別加以考慮。下面分別給予介紹。

2.2 基于FPGA的TS101鏈路口設計

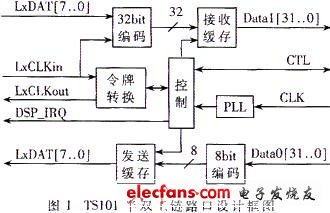

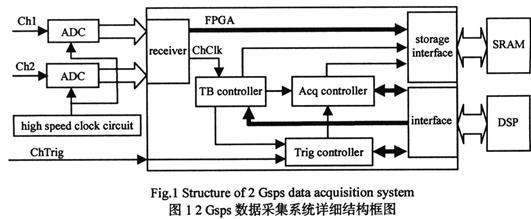

圖1給出了FPCA與TS101進行半雙工鏈路口通信的設計(對LxCLKOUT、LxCLKIN均以FPCA的角度來敘述),該接口由接收、控制和發送三部分組成。本設計FPGA時鐘為40MHz,TS101核時鐘上作在250MHz,鏈路口時鐘設定為DSP核時鐘的8分頻,FPGA與DSP的實際數據傳輸率為62.5MBps。

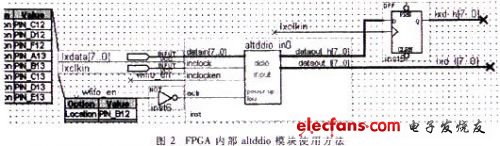

(1) 接收部分:由編碼和緩存兩部分組成。由于鏈路口的數錯是DDR形式的,不方便數據的緩存,本文采用QuartusII Megafunctions中的altddio模塊將上升沿數據和下降沿數據分開。注意這個模塊的下降沿數據輸出會滯后上升沿數據1個時鐘周期,輸出時應該用鏈路口時鐘信號(LxCLKIN)通過D觸發器來將數據對齊。該模塊的inclock一定要用鏈路口時鐘信號以保證數據的正確讀取,如圖2所示。又由于DSP內部數據是32位的長字,所以寫入接收緩存前應該用一組D觸發器將數據進行32bit對齊,這里注意DSP鏈路口先傳輸32位數據中的低8位。

(2) 控制部分:由令牌轉換模塊和控制模塊組成,是整個設計的核心部分,完成對各部分的控制和與FPGA內部進行通信(通過CTL一組信號)。TS101的鏈路口通信握手是靠兩根時鐘信號驗證令牌指令完成,即當發送端驅動原本為高的LxCLKOUT信號為低電平,以此作為令牌請求向接收端發出。如果接收端準備好接收,則接收端驅動LxCLKIN為高;如果令牌發出6個時鐘周期后,LxCLKIN信號仍然為高,則肩動數據傳輸(以上時鐘信號都以發送端視角分析)。本設計中,令牌轉換模塊負責驗證令牌和發送令牌。這里要注意,由于用來驗證令牌低電平個數的時鐘信號(PLL_32ns)是由FPGA時鐘信號(CLK)通過鎖相環倍頻得到,與DSP鏈路口時鐘異步,故驗證令牌時,當計數器計到5個低電平時即可認為已達成通信握手,否則可能會丟失數據。達成握手后通知控制模塊向接收或發送緩存輸出控制信號,其中接收控制信號包括寫緩存時鐘和寫使能。發送控制信號包括讀緩存時鐘、讀使能和DSP中斷信號(DSP_IRQ),其中寫緩存時鐘通過對鏈路口時鐘分頻得到,讀緩存時鐘由鎖相環倍頻FPGA工作時鐘得到。

(3) 發送部分:與接收部分類似,也南編碼和緩存兩部分組成,相應的設計基本相同,這里不作過多介紹。由于DSP鏈路口每次傳輸數據個數的最小單位是4個32位字,即8個鏈路時鐘周期,所以發送時鐘廊該每8個時鐘周期一組,以湊夠128bit,避免傳輸錯誤,其中多余無效的數據DSP可以自行舍去。發送部分采用DSP外部中斷方式而不是鏈路口中斷方式通知DSP接收數據。

TS101的鏈路口通信協議要求鏈路口接收端在傳輸啟動一個周期后,將其LxCLKOUT拉低,若可以繼續接收,在下一個周期再將其拉高,以此作為連接測試。實際運行中發現,當FPGA接收數據時,可將LxCLKOUT信號一直驅動為高,不必做特殊的連接測試也能正確接收數據。另外,發送鏈路口數據時,由于發送緩存中已經對應仔好了要發送的8bit數據,故可以使用對FPGA時鐘信號(CLK)倍頻得到的PLL_16ns信號來讀發送緩存,讀出的數據即鏈路口發送數據,再對PLL_16ns信號的下降沿分頻得到鏈路口的發送時鐘信號。

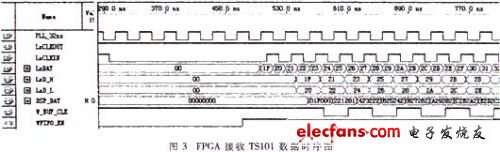

限于篇幅,本文只給出FPCA接收TS101數據的時序圖,如圖3所示。LxCLKIN、LxDAT[7..0]是DSP的鏈路口輸出時鐘和數據,LxCLKOUT是FPGA的回饋準備好信號。仿真中鏈路口數據采用1F-3E(十六進制)的32個8bit數據,即從2221201F到3E3D3C3B的8個32bit數據;PLL_32ns信號是FPGA內部鎖相環產生的與DSP鏈路口時鐘異步的32ns時鐘信號,用來校驗令牌指令;W_FIFO_EN信號足寫緩存使能信號,當令牌驗證后使能接收緩存;DSP_DAT信號是DSP通過鏈路門傳輸的32bit數據,通過對鏈路口數據的編碼得到;W_BUF_CLK信號由鏈路口時鐘分頻處理得到,將上升沿對應的32bit DSP數據寫入接收緩存,完成接收過程。

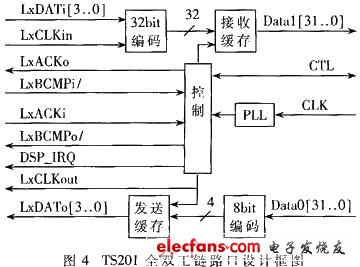

2.3 基于FPGA的TS201鏈路口設計

圖4給出了FPGA與TS201進行鏈路口通信的設計框圖。由于TS201的握手信號較多,所以相對TS101的鏈路口設計容易些。本設計FPGA時鐘50MHz,TS101核時鐘500MHz,鏈路口時鐘為DSP核時鐘的4分頻,采用4bit方式,單向實際數據傳輸速率為125MBps。

TS201的鏈路口數據和時鐘采LVDS信號,具有速率高、功耗低、噪聲小的優點。Cyclone系列芯片不僅支持LVDS信號,還集成了LVDS轉換模塊,這給設計提供了很大方便。應該注意的是,在硬件設計時LVDS信號兩極的PCB走線要匹配,并且注意匹配電阻網絡的接入。

TS201的鏈路口有1bit和4bit兩種傳輸方式,本文以4bit為例進行設計。圖4給出的信號都是經LVDS轉換后的信號。由于TS201的收發做成了兩個單獨的通道,FPGA的設計也應該相應地設計為兩個通道,真正做到全雙工通信,收發互不影響。接收與發送部分與TS101的設計基本相同,發送部分也采用外部中斷方式通知DSP接收鏈路口數據。TS201的通信握手信號有ACK和BCMP#信號。其中ACK信號用來通知接收準備好,在實時信號處理中,一般不允許數據傳輸的等待,故將這個信號置為準備好。BCMP#信號用于通知數據塊傳輸的結束,當能確定DMA傳輸數據個數時,可以將此引腳懸空。

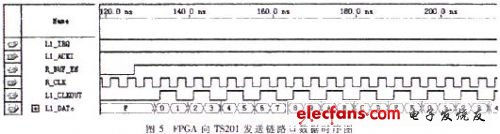

TS201鏈路口的收發機制非常相似,本文僅給出發送數據時序圖,如圖5所示。L1_IRQ是FPGA發給DSP的外部中斷,用來通知DSP收數據;L1_ACKI是DSP的接收準備好信號;R_BUF_EN是讀發送緩存使能信號;鏈路口時鐘L1_CLKOUT是以讀緩存時鐘R_CLK下降沿的二次分頻,對應從緩存中讀出的4bit鏈路口數據L1_DA-To。注意這里讀緩存及時鐘分頻時會有納秒級的延遲。

3 DSP的相應設置

TS101和TS201的鏈路口都配置了控制寄存器(LCTLX)和狀態奇存器(LSTATx)兩組寄存器。LCTLx用來控制鏈路口的傳輸,LSTATx用來通知鏈路口的工作狀態。TS101鏈路口時鐘頻率可以是核時鐘的8、4、3或2分頻,通過設置LCTLx中的SPD位米完成,本文設計將SPD位置000,即為核時鐘8分頻。由于TS201的接收發送通道獨立,所以其控制寄存器分為接收控制寄存器(LRCTLx)和發送控制寄存器(LTCTLx)。TS101鏈路口發送時鐘頻率可以與核時鐘相同或為其4、2、1.5分頻,通過設置LTCTLx中SPD位來完成。本文設計將SPD位置100,即為核時鐘4分頻,并將LRCTLx/LTCTLx中(接TDSIZE位置1,設置成4bit傳輸方式。如果BCMP#信號懸空,注意一定要將LRCTLx巾RBCMPE位置0。

有兩種方法啟動DSP的鏈路口DMA傳輸:利用鏈路中斷和利用DSP的四個外部中斷(IRQ0-IRQ3)。兩種中斷方式都需要在中斷服務程序中對DMA的TCB寄存器進行配置來啟動鏈路口的接收DMA通道。鑒于外部中斷的優先級高于鏈路口中斷,可以避免數據丟失,本文設計的通信方式均以外部中斷方式通知DSP接收數據。在DMA的TCB寄存器配置過程中,為了保證程序不被其他中斷打斷,可以在中斷服務程序開始時就把所有其他中斷屏蔽掉,存中斷服務程序返回之前再把屏蔽掉的中斷位還原。

本文對TigerSHARC系列的兩種典型DSP芯片的鏈路口進行了分析和比較,并給出了FPGA與這兩種DSP芯片進行鏈路口通倍的具體方法。在FPGA內部實現了DSP鏈路口的設計,同時給出了DSP進行鏈路口通信的具體設置方法。由于實時處理中數據的重發會嚴重影響處理的實時性,故本文的鏈路口通信設計沒有對所傳輸的數據進行校驗。本文給出的基于FPGA路口設計具有很強的通用性,可以應用于基于TS101/TS201的多種應用系統中,提高系統內部的通信能力,也可用于板間DSP的數據傳輸,提高系統外部的通信能力。

電子發燒友App

電子發燒友App

評論