串行(chuan xing)是中文“通用串行總線”的簡(jiǎn)稱(chēng)。英文為USB(Universal Serial Bus)是1995年Microsoft、Compaq、IBM等公司聯(lián)合制定的一種新的PC串行通信協(xié)議。USB協(xié)議出臺(tái)后得到各PC廠商、芯片制造商和PC外設(shè)廠商的廣泛支持。USB本身也處于不斷的發(fā)展和完善中,從當(dāng)初的0.7、0.8到現(xiàn)在廣泛采用的1.0、1.1,2.0版本以及已經(jīng)被采用,即將被量產(chǎn)應(yīng)用的3.0版本

串行數(shù)據(jù)與并行數(shù)據(jù)是相對(duì)的一對(duì)概念。串行數(shù)據(jù)是指?jìng)鬏斶^(guò)程中各數(shù)據(jù)位按順序進(jìn)行傳輸?shù)臄?shù)據(jù),并行數(shù)據(jù)則是各數(shù)據(jù)位同時(shí)傳送的數(shù)據(jù)。串行通信是指使用一條數(shù)據(jù)線,將數(shù)據(jù)一位一位地依次傳輸,每一位數(shù)據(jù)占據(jù)一個(gè)固定的時(shí)間長(zhǎng)度。其只需要少數(shù)幾條線就可以在系統(tǒng)間交換信息,特別使用于計(jì)算機(jī)與計(jì)算機(jī)、計(jì)算機(jī)與外設(shè)之間的遠(yuǎn)距離通信。

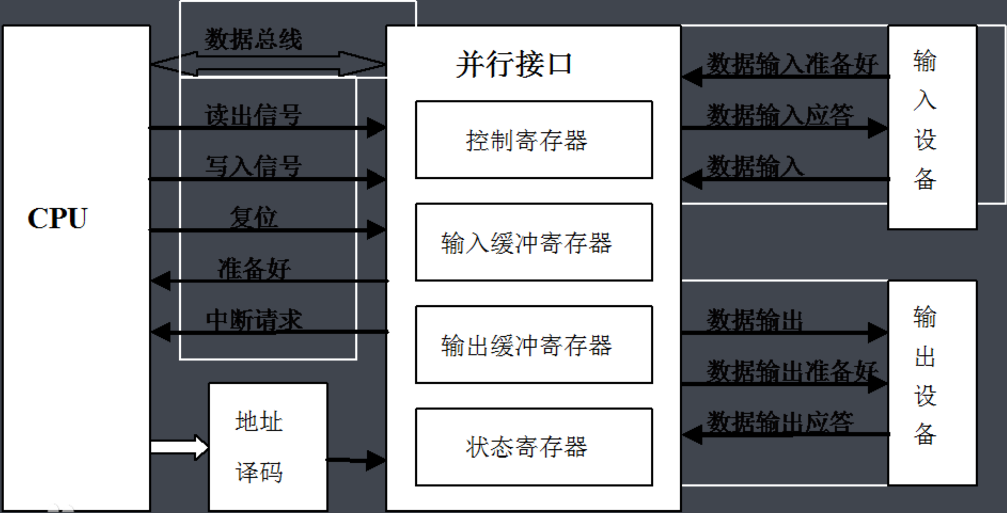

數(shù)據(jù)并行的含義是計(jì)算機(jī)內(nèi)包含一組處理單元(PE),每一個(gè)處理單元存儲(chǔ)一個(gè)(或多個(gè))數(shù)據(jù)元素。當(dāng)機(jī)器執(zhí)行順序程序時(shí),可對(duì)應(yīng)于全部或部分的內(nèi)部處理單元所存的數(shù)據(jù)同時(shí)操作。

數(shù)據(jù)級(jí)并行依賴(lài)于并行處理機(jī),它屬于SIMD系統(tǒng)內(nèi)的并行。并行處理機(jī)的特點(diǎn)是重復(fù)設(shè)置許多個(gè)同樣的處理單元,按照一定的方式相互連接,在統(tǒng)一的控制部件作用下,各自對(duì)分配來(lái)的數(shù)據(jù)并行地完成同一指令規(guī)定的操作。

控制部件實(shí)際上是一臺(tái)高性能單處理機(jī),它執(zhí)行控制指令和只適用于串行處理的操作指令,而把適用于并行處理的指令傳送給所用的處理單元,但僅有那些處于“活動(dòng)”狀態(tài)的處理單元才并行地對(duì)各自的數(shù)據(jù)進(jìn)行同一操作。為了實(shí)現(xiàn)快速有效的數(shù)據(jù)處理,數(shù)據(jù)應(yīng)在各處理單元之間合理分配與存儲(chǔ),使各處理單元主要對(duì)自身存儲(chǔ)器內(nèi)的數(shù)據(jù)進(jìn)行運(yùn)算。

串行數(shù)據(jù)轉(zhuǎn)換并行數(shù)據(jù)的原理圖

module UART_Receiver(

Serial_in,

istartofpacket,

iendofpacket,

clk,RSTn,

Data_Bus,

datavalid,

oempty,

oendofpacket,

ostartofpacket

);

parameterNum_counter_bits=4;

parameterNum_state_bits=3;

parameterword_deepth_size=7;

parameterdeepth_counter_size=3;

parameteridle=3‘b001;

parameterreceiving=3’b010;

parametersending=3‘b100;

output[word_size-1:0]Data_Bus;

output

oendofpacket,ostartofpacket;

oempty,datavalid,

inputSerial_in;inputclk;inputRSTn;

inputistartofpacket;inputiendofpacket;

reg[word_size-1:0]RCV_datareg[word_deepth_size -1:0];

reg[word_size-1:0]RCV_shftreg;

reg[Num_counter_bits-1:0]bit_count;

reg[deepth_counter_size-1:0] deepth_count1,deepth_count2;

reg[Num_state_bits-1:0]state,next_state;

reginc_bit_counter,clr_bit_counter;

regclr_deepth_counter1;

regclr_deepth_counter2;

regclr_deepth_counter2;regshift,load_datareg;regoutputstart,outputend;regsend_word;

regoendofpacket,ostartofpacket;regoempty;regdatavalid;

reg

[word_size-1:0]

Data_Bus;

clr_deepth_counter1=0;clr_deepth_counter2=0;clr_bit_counter=0;inc_bit_counter=0;shift=0;

load_datareg=0;outputstart = 0;outputend = 0;send_word =0;

next_state

=state;

if(istartofpacket==1)next_state=receiving;shift =1;begin

end

idle:

inc_bit_counter =1;shift = 1;begin

endif(bit_count != word_size-1)

clr_bit_counter =1;load_datareg =1;shift = 1;begin

endif(deepth_count1!=word_deepth_size-1)

load_datareg =1;clr_bit_counter =1;

clr_deepth_counter1 = 1;next_state = sending;begin

end

end

end

send_word = 1;outputstart = 1;begin

end

if(deepth_count2 == 0)

outputend = 1;send_word = 1;

clr_deepth_counter2 =1;next_state = idle;begin

endelse if(deepth_count2 == word_deepth_size-1)

send_word = 1;

else

sending:

next_state=idle;

default:

endcaseend

state《=idle;bit_count《=0;deepth_count1《=0;deepth_count2《=0;RCV_shftreg《=0;ostartofpacket 《= 0;oendofpacket 《= 0;Data_Bus 《= 0;begin

endif(RSTn == 0)

state《=next_state;oempty 《= 0;

bit_count《=0;

if(clr_bit_counter == 1)

bit_count《=bit_count + 1;

else if(inc_bit_counter == 1)

deepth_count1《=0;if(clr_deepth_counter1 == 1)deepth_count1《=deepth_count1 + 1;

else if(load_datareg == 1)

RCV_shftreg《={Serial_in,RCV_shftreg[word_size-1:1]};

if(shift == 1)

begin

else

begin

always @ (posedge clk)

RCV_datareg[deepth_count1] 《=RCV_shftreg;if(load_datareg == 1)

deepth_count2《=0;if(clr_deepth_counter2 == 1)

deepth_count2《=deepth_count2 + 1;else if(send_word == 1)

ostartofpacket 《= 1;if(outputstart ==1)

ostartofpacket 《= 0;

else

oendofpacket 《= 1;if(outputend == 1)

oendofpacket 《= 0;

else

Data_Bus 《= RCV_datareg[deepth_count2];datavalid 《= 1;begin

endif(send_word == 1)

Data_Bus 《= 0;datavalid 《= 0;begin

endelse

end

endendmodule

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論