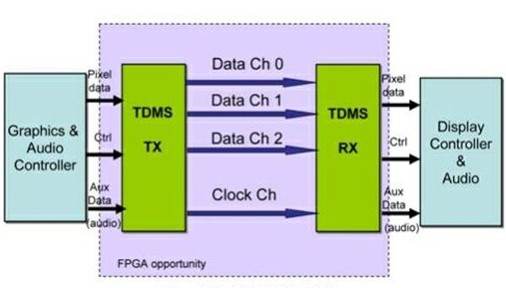

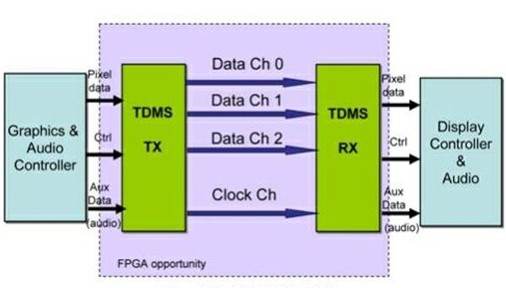

利用內置的SERDES和可以從萊迪思半導體公司得到的參考設計,ECP2M可以成功地實現接收和/或傳送DVI/HDMI接口功能。通過使用FPGA技術和參考設計,設計人員能夠很快地實現設計的其余部分,并無縫地連接到一個DVI/ HDMI接口,以滿足他們自己的特殊要求。

2013-04-16 10:56:45 4625

4625

隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。在過去幾年中已經看到有內置SERDES 的FPGA 器件系列,但多見于高端FPGA芯片中,而且價格昂貴。

2015-02-02 17:32:52 2204

2204

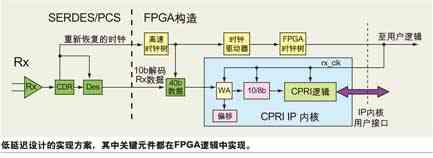

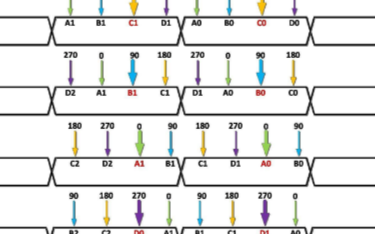

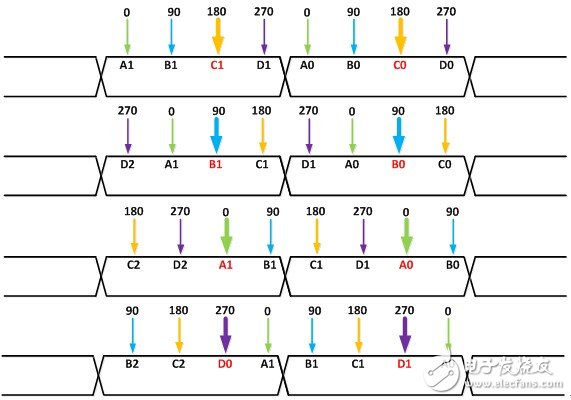

SERDES恢復出的數據進入FPGA有一個解復用和時鐘域轉換的問題,Stratix GX包含了專用電路可以完成8/10bit數據到8/10/20bit數據的Mux/Demux,另外SERDES收端到FPGA內部通用邏輯資源之間還有FIFO可以完成數據接口同步,其電路結構如圖所示。

2018-04-08 08:46:50 9421

9421 GMII、SGMII和SerDes的區別和聯系? GMII和SGMII區別,上一篇已經介紹了,這一篇重點介紹SGMII和SerDes區別。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29958

29958

及的底層輸入-輸出 PHY 技術是串行器-解串器 (SerDes) 技術。FPGA 作為一項技術從一開始就很復雜且具有挑戰性,甚至在考慮高速接口之前也是如此。SerDes PHY 設計本身就很復雜且具有

2023-02-22 13:37:54 1151

1151 SERDES是英文SERializer(串行器)/DESerializer(解串器)的簡稱。

2024-01-04 09:04:02 495

495

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-10-23 07:16:35

的設計者面臨著一個不同以往的挑戰:提供一個不僅能滿足這些集成電路對互連帶寬的要求,而且還能支持不同接口協議的可編程接口。解決方案是可編程硬件I/O模塊。這些可編程硬件模塊位于FPGA的I/O路徑內。硬件模塊

2018-11-26 11:17:24

本人剛入門FPGA,不知道如何實現FPGA+DSP,FPGA+ARM接口設計,網上查詢有的說FPGA+DSP可以通過EMIF,IP核實現,FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

后,將電路板上電運行。然后把下載電纜接到JTAG接口上,在主機中運行Quartus II軟件,并打開Programmer編程器,單擊其中的“Auto Detect”按鈕進行FPGA下載鏈路自動檢測。若能正確檢測到FPGA,說明配置電路是正確連接的。

2012-08-12 11:52:54

,整板硬件包括FPGA電路, DDR3電路,外圍接口電路,加上時鐘和控制邏輯等輔助電路,形成一個完整的、一體化的數字系統硬件平臺。能夠快速接入FC-AE網絡,實現光纖總線終端的數據通訊。課程提供項目

2021-11-17 23:12:06

類型也更多,而且內部還集成了一些特殊功能單元,包括: SERDES:高速串行接口。將來 PCI-E、XAUI、HT、S-ATA 等高速串行接口會越來越多。有了 SERDES 模塊,FPGA 可以很

2020-09-08 22:43:16

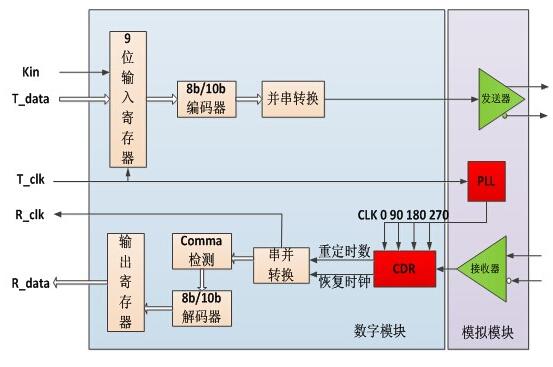

的時鐘域中選擇數據位,例如檢測電路確定從時鐘域A中采樣的數據有效,那么將時鐘域A中采樣的數據通過輸出端輸出。 3 結束語: 通過對純數字電路的CDR電路,在沒有硬核的支持下,完成了FPGA上SERDES的接口設計,并通過實驗的傳輸測試,在HR03的FPGA上,可完成100~200Mbps的數據傳輸。

2019-05-29 17:52:03

親愛的Xilinx論壇,我正在實現基于SERDES協議的序列化傳輸。我需要在Kintex7上接收8個差分對,這些差分對承載由另一個Kintex7串行化的64位字,主時鐘為100MHz。將托管FPGA

2020-03-17 09:53:11

用戶在產品選型和方案設計之初,對于硬件接口資源分配不熟悉,不遵守芯片規范使用導致項目出現問題,造成了嚴重損失。本期我們就此系列平臺的SerDes資源分配做一篇文章。LS系列產品的資源不可為不豐富,其中最讓人頭暈的當屬于SerDes協議。百度百科這樣解釋,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。從PCI到PCI Express, 從ATA到SATA,從并行ADC接口到JESD204, 從RIO

2021-07-28 07:02:12

SerDes的發送端TX的均衡原理是什么?怎樣利用高速接口SerDes去實現芯片間信號的有線傳輸?

2021-06-17 07:15:16

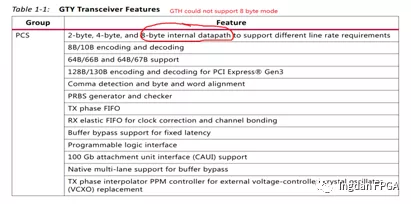

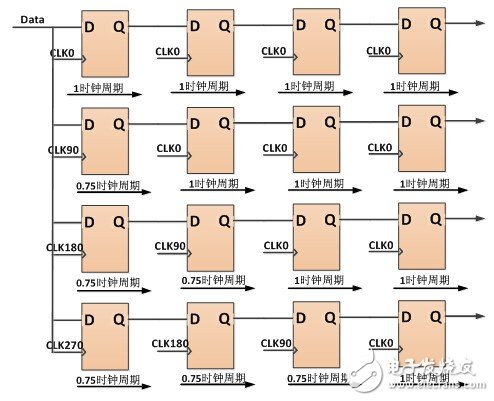

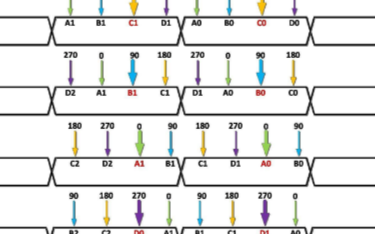

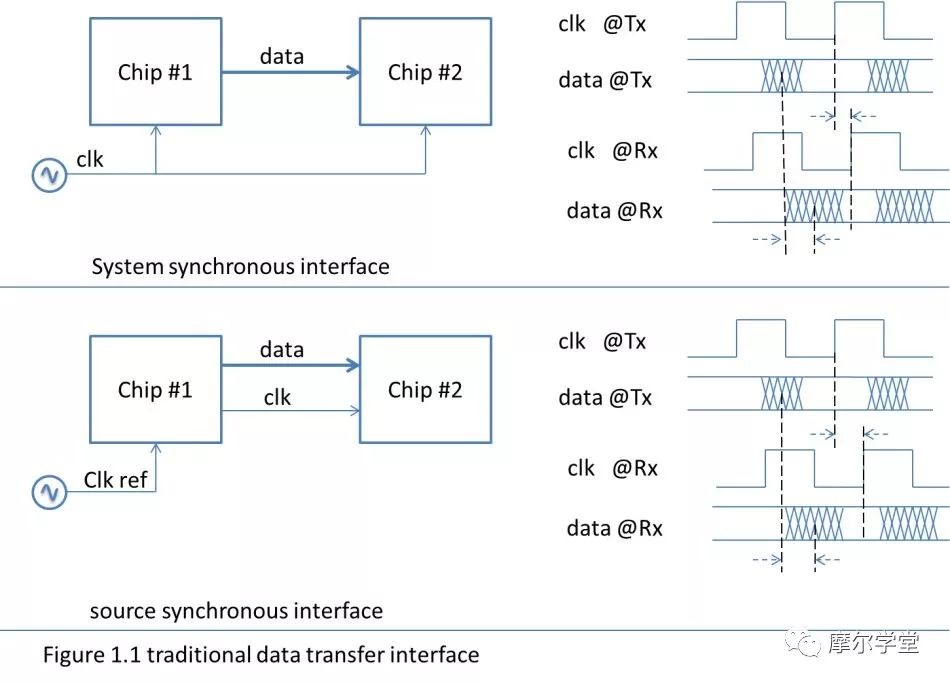

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了有效數據窗口寬度的繼續增加。a)、時鐘...

2021-07-28 08:35:42

我的印象是 Serdes 到 Serdes 10G 以太網連接是 T2080 上的一個功能選項。當嘗試通過光纖或跨背板時,這會失敗。memac 統計數據顯示沒有八位字節輸出,狀態寄存器指示 LI

2023-04-27 06:01:25

如題,9176DAC的PLL鎖上了,證明時鐘應該沒問題,但是為什么DLL和serdes PLL鎖不上呢?配置順序,我是按照手冊的START-UP SEQUENCE進行配置的。

2023-12-01 06:54:09

SerDes在93000平臺上量產測試。本文將介紹Nautilus UDI方案是如何實現高速SerDes測試的,包括UDI結構,輸入時鐘設計,Load board設計,socket選型等多個測試環節。

2021-05-10 06:58:55

、MIPI接口的硬件設計注意事項。 本視頻教程利用MiniStar開發板進行講解,視頻課程注重基礎知識和設計思路的講解,幫助剛接觸高云FPGA的硬件工程師快速了解DDR3、HDMI、MIPI接口在硬件上的注意事項,也歡迎大家與我們交流在高云FPGA硬件設計上的問題。

2021-04-16 17:55:29

接口;能獨立承擔硬件FPGA設計項目,按照項目計劃要求完成任務,能夠獨立進行FPGA需求分析、芯片評估、器件選型,并完成相關硬件系統設計,代碼設計,仿真和調試;熟悉硬件設計流程,熟練應用Protel

2017-06-29 13:47:39

大家好, 在一個I / O塊中有一個主serdes和一個slave serdes。如果我使用主設備,奴隸不能使用,是不是?謝謝。最好的祝福。

2020-06-08 15:03:22

什么是SerDes?

2021-06-24 07:52:02

很好的應用筆記,用于在spartan fpgas中實現serdes但是對Virtex5沒什么用?任何人都可以指出我使用V5 fpgas正確實現serdes(lvds)的一些資源。我將從主設備向10個從

2020-07-13 15:54:49

具有可重復的確定性延遲。隨著轉換器的速度和分辨率不斷提升,JESD204B接口在ADI高速轉換器和集成RF收發器中也變得更為常見。此外,FPGA和ASIC中靈活的串行器/解串器(SERDES)設計正逐步

2018-10-16 06:02:44

CAUI電接口的轉換。FPGA不僅有軟件的可編程性和靈活性,同時又有ASIC高吞吐和低延時的特性。另外由于FPGA有高速SERDES等豐富的接口,而且能靈活控制實現的粒度和操作數據,因此在通信行業得到

2017-05-04 14:53:41

字信號處理、硬件數字濾波器、各種算法等,或者利用FPGA來擴展I/O接口,如實現多路PWM(脈寬調制)輸出、實現PCI接口擴展等。通過合理的系統軟硬件功能劃分,結合優秀高效的FPGA設計,整個嵌入式

2019-05-06 09:18:16

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立的ASSP 或ASIC 器件。

2019-10-14 06:39:42

如何在Serdes_0 (s32g274a) 上使用sgmii模式?

2023-05-09 07:41:26

我們在Artix-7上運行了一個1.0625 Gb / s鏈接進出Serdes。在接收方,如果我們拉光纖斷開鏈路然后重新連接光纖,Serdes將不斷指示rxbyterealign并且從不同步到輸入

2020-08-21 11:05:45

總線的FPGA接口? FPGA必須插在服務器主板上嗎?它可以與普通的服務器主板連接嗎?我的問題是我只能在電路板底部表面的過孔處點擊QPI信號,并需要某種連接器來連接FPGA。謝謝!

2020-03-13 10:05:34

HSDI接口的硬件結構以及接口信號的時序和功能操作基于FPGA實現HSDI接口的設計

2021-04-09 06:40:16

的模數轉換器(ADC)和數模轉換器(DAC)支持最新的JESD204B串行接口標準,出現了FPGA與這些模擬產品的最佳接口方式問題。FPGA一直支持千兆串行/解串(SERDES)收發器。然而在過去,大多數ADC

2021-04-06 09:46:23

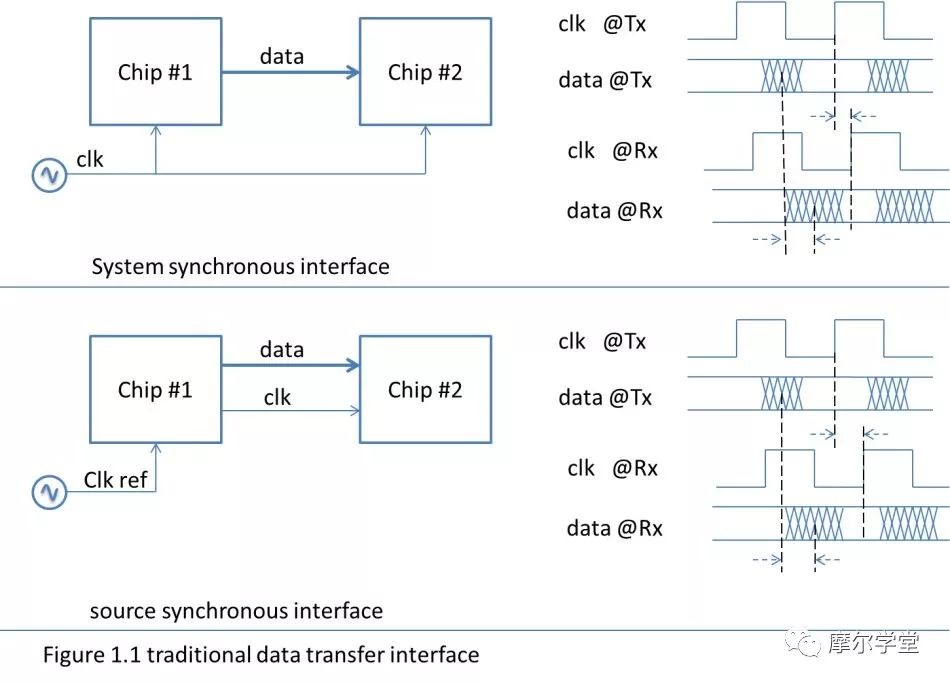

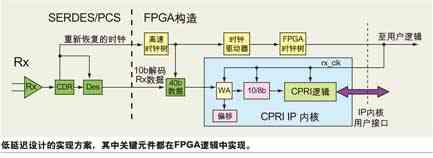

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data

2019-10-21 07:09:44

如果不使用FPGA自帶的SERDES,可否適用LVDS接口實現其功能?

2023-05-08 17:37:48

SerDes的基本結構是由哪些部分組成的?怎樣去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有傳輸時鐘信號嗎?

2021-10-18 08:53:42

新手接觸fpga 硬件接口 求推薦好書

2013-04-01 21:09:25

SERDES的作用有哪些?SerDes的主要構成可以分為哪幾部分?

2021-10-18 09:25:08

賽靈思 Artix-7 FPGA 是業界唯一的在低端器件上整合了高速收發器的方案,該方案提供了自適應均衡、2D 眼圖以及IBIS-AMI仿真模型來簡化針對成本敏感型應用的高速串行設計,觀看視頻,4分鐘教您搞定高速SerDes端口設計。

2016-07-27 17:29:59

6678中的srio的serdes和以太網的serdes是共用還是各自有自己的serdes?

2018-08-02 06:11:31

是整個溫控系統的硬件基礎,其中涉及到溫度采集,與微處理器通信,串口輸出,控制數模轉換芯片等多個組成部分。本文提出一種高效實用的FPGA接口設計,它能夠完成協調各個組成部分有序工作,準確、快速實現數據傳輸

2020-08-19 09:29:48

或者同時送兩個接口。送往B口的數據包經過MAC幀格式拆封和B口格式封裝后輸出到轉發模塊,送往F口的數據經過數據寬度和時鐘頻率的變換后輸出到協議FIFO。第二、線路接口卡上電初始化時,輸入FPGA通過板級

2019-04-29 07:00:07

SERDES內的時鐘和數據恢復(CDR)電路完成這個處理。CDR電路將每個串行的T M D S通道轉換至10位,并將具有同步時鐘的數據傳送至FPGA接口,然后在FPGA中進行數據處理達到同步。這要求有

2019-06-06 05:00:34

用戶在產品選型和方案設計之初,對于硬件接口資源分配不熟悉,不遵守芯片規范使用導致項目出現問題,造成了嚴重損失。本期我們就此系列平臺的SerDes資源分配做一篇文章。LS系列產品的資源不可為不豐富,其中

2020-10-28 17:15:14

用戶在產品選型和方案設計之初,對于硬件接口資源分配不熟悉,不遵守芯片規范使用導致項目出現問題,造成了嚴重損失。本期我們就此系列平臺的SerDes資源分配做一篇文章。?LS系列產品的資源不可為不豐富,其中

2020-11-01 20:21:02

Guide,能指導版圖工程師進行電路版圖設計;6. 具有深亞微米電路設計經驗;7. 有良好的英語溝通能力,良好的團隊合作。 Serdes PCS職位描述:1. 負責高速數字電路IP算法、協議、接口、控制

2017-11-13 14:46:14

SERDES結構是怎樣構成的?高速SERDES接口在網絡方面有哪些應用?

2021-04-28 07:19:38

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

去偏移和包重組是在FPGA中實現SPI-4.2接口的核心難點,在分析偏移和包重組原理的基礎上,給出基于FPGA的SPI-4.2接口的設計與實現方案,并對關鍵部分給出了硬件原理圖,在線測試結

2009-04-10 09:43:35 32

32 當前的路由器或交換機產品都提供多端口千兆以太網接口。采用高性能FPGA 設計十端口千兆以太網接口, 闡述了系統平臺的硬件設計及主要單元模塊的功能,并對FPGA 內部程序設計的

2009-08-29 09:30:59 51

51 利用現場可編程門陣列FPGA 實現單片機的外設接口電路可以簡化單片機系統的硬件電路,提高系統的集成度、可靠性和系統設計的靈活性。本文介紹了基于FPGA 的單片機外設接口電

2009-12-26 16:43:27 80

80 串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統的帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

38 本文介紹了一種FPGA和IPX2805之間的SPI4.2接口模塊設計的方法,對硬件設計進行了說明,著重闡述了FPGA內部SPI4.2接口模塊設計。該設計簡單、高效,解決了商用芯片不能滿足高速轉發的系

2010-07-28 16:56:32 33

33 本文討論利用帶嵌入式SERDES收發器和CPRI鏈路IP內核的低成本FPGA,來實現電信

2010-10-09 16:48:05 1165

1165

SERDES在數字系統中高效時鐘設計方案,無論是在一個FPGA、SoC還是ASSP中,為任何基于SERDES的協議選擇一個參考時鐘源都是非常具有挑戰性的。

2012-02-16 11:23:43 5383

5383

電子發燒友網: 本文主要講述的是 LatticeECP4 高速可配置SERDES。 LatticeECP4 FPGA系列結合了高性能 FPGA 結構、高性能I/O和多達16個通道的嵌入式SERDES,帶有相關的物理編碼子層(PCS)邏輯。每

2012-06-12 10:41:35 1439

1439

電子發燒友網: 本文主要介紹FPGA設計中功率計算的技巧。隨著工藝技術的越來越前沿化, FPGA器件擁有更多的邏輯、存儲器和特殊功能,如存儲器接口、 DSP塊和多種高速SERDES信道,這

2012-07-02 09:32:54 1638

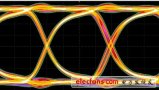

1638 FPGA SERDES的應用需要考慮到板級硬件,SERDES參數和使用,應用協議等方面。由于這種復雜性,SERDES的調試工作對很多工程師來說是一個挑戰。

2013-03-15 14:55:13 10359

10359

基于FPGA的SDI接口設計,學習FPGA的好資料!!!!

2016-06-06 10:00:46 29

29 隨著更多的模數轉換器(ADC)和數模轉換器(DAC)支持最新的JESD204B串行接口標準,出現了FPGA與這些模擬產品的最佳接口方式問題。FPGA供應商多年來一直支持千兆串行/解串(SERDES

2017-11-18 01:48:02 1277

1277 。另外,用戶還可以使用NI VeriStand,通過基于FPGA 的I/O接口創建用戶自定義的I/O硬件。本文說明了使用基于FPGA I/O接口的益處,以及如何同NI VeriStand一起使用它們。

2017-11-18 07:47:35 8845

8845

這個文件包含執行指令(串行/ SERDES接口on the tms320c6474)基于DSP器件。包括串行RapidIO?(SRIO),天線,和串行千兆比特媒體獨立接口(sgmii)接口。

2018-04-17 09:38:01 3

3 本文檔的主要內容詳細介紹的是FPGA教程之FPGA硬件最小系統設計的詳細資料說明包括了:1.FPGA最小系統概念以及硬件系統的構成,2.FPGA主芯片電路設計,3.JTAG下載與調試接口,4.高速

2019-04-04 17:18:48 101

101 本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data

2019-05-24 15:33:25 4072

4072

隨著通信技術的飛速發展,高速數據傳輸系統成為了當前研究的熱點,而高速 SERDES 接口芯片的研究則是其中一個重要的組成部分。SERDES 接口芯片的主要功能是將低速的并行信號轉換成為高速低壓差分信號(LVDS)并通過串行鏈路發送,同時能夠接收串行輸入 LVDS 數據并正確的轉換為低速并行信號。

2019-06-24 08:00:00 12

12 只要SERDES接口的高級架構是合理的,SERDES總線的成功實現就歸結為“實現細節”。

2019-08-14 17:57:00 2615

2615 串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。

2020-05-18 10:51:18 2964

2964

總線而成為高速接口設計的主流。 如今,隨著SerDes接口的廣泛應用,許多高端的FPGA都內嵌有SerDes接口硬核。在FPGA中內嵌的SERDES的硬核,可以大大地擴張FPGA的數據吞吐量,節約功耗,提高性能,使FPGA在高速系統設計中扮演著日益重要的角色。 國產

2020-07-28 12:05:16 1128

1128 芯片功能的增加和數據吞吐量的要求, 促使芯片行業從較低數據率的并行連接, 轉向較高速度的串行連接。SERDES(Serializer-Dese rializer ,) 是經高速差分對,而不是經較低

2020-10-09 17:25:07 18

18 因為攝像頭輸出的LVDS信號速率會達到600Mbps,我們將不能夠通過FPGA的I/O接口直接去讀取這么高速率的信號。因此,需要使用Xilinx FPGA內的SerDes去實現高速數據的串并轉換。

2020-12-30 17:24:00 39

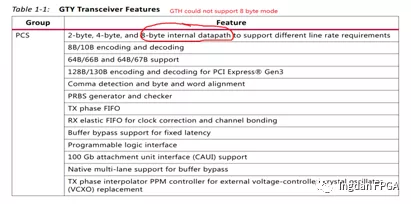

39 我在2015年底到2016年初的時候,使用7 Series FPGA Transceivers完成了TS流數據的傳輸,當時使用的傳輸速度為3.125G,SerDes選取的是8b/10b編碼方式

2020-12-30 17:24:00 31

31 本文檔的主要內容詳細介紹的是Xilinx 7 系列FPGA中的Serdes總結。

2020-12-31 17:30:58 25

25 偏移和包重組是在FPGA中實現SPI一4.2接口的核心難點,在分析偏移和包重組原理的基礎E,給出基于FPGA的SPI一4.2接口的設計與實現方案,并對關鍵部分給出r硬件原理圖,在線測試結果證明該方案可以實現SPI一4.2接口的功能。

2021-01-25 14:51:21 13

13 為了學習xilinx serdes 原語的使用,以及交流學習經驗,在工程項目中方便的應用SERDES進行設計,故編寫此文檔。

2021-02-26 10:04:00 37

37 產品上市的速度。 如今,PCIe、HDMI以及USB這樣的高速接口已變得不可或缺,但20年前的情況并不是這樣,過去的20年中,串行接口應用數量經歷了爆炸性的增長。 從上世紀九十年代末開始,SERDES二十年的革命之路。本文將通過一些底層技術的簡單介紹,嘗試解釋下為什么串行接口(以SERDES為代表)

2021-07-23 11:21:19 3986

3986 SERDES的優勢 引腳數量和通道優勢 SERDES最明顯的優勢是具備更少的引腳數量和線纜/通道數量。對于早期的SERDES,這意味著數據可以通過同軸電纜或光纖發送。 對于現代的SERDES來說

2021-07-23 11:59:46 3794

3794 在Serdes流行之前,芯片之間的數據傳輸主要靠低俗串行接口和并行接口,存在諸如傳輸速率低、占用IO數量多、硬件連接復雜化等弊端。Serdes的出現簡化了數據傳輸接口的硬件設計,大大提升了數據傳輸

2022-08-02 11:28:14 4854

4854

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。

2022-10-31 11:28:41 1349

1349 SERDES:高速串行接口。將來PCI-E、XAUI、HT、S-ATA等高速串行接口會越來越多。有了SERDES模塊,FPGA可以很容易將這些高速串行接口集成進來,無需再購買專門的接口芯片。

2023-01-03 16:23:35 626

626 FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是器件的標配了。從PCI發展到PCI-E,從ATA發展到SATA,從并行ADC接口到JESD204,從RIO

2023-03-16 10:28:11 1915

1915

利用源同步接口,數據的有效窗口可以提高很多。通常頻率都在1GHz以下。在實際應用中可以見到如SPI4.2接口的時鐘可以高達DDR 700MHz x 16bits位寬。DDR Memory接口也算一種源同步接口,如DDR3在FPGA中可以做到大約800MHz的時鐘。

2023-03-28 15:51:15 849

849 同時介紹一種采用光電集成技術的,即采用光SerDes而非電SerDes的高速收發器。

2023-04-01 09:28:58 1078

1078 首先我們要了解什么是SerDes,SerDes的應用場景又是什么呢?SerDes又有哪些常見的種類?

2023-06-06 17:03:55 4706

4706

? 串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2023-07-27 16:10:01 1565

1565

FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是器件的標配了。從PCI發展到PCI-E,從ATA發展到SATA,從并行ADC接口到JESD204,從RIO

2023-10-16 14:50:37 558

558

盡管設計和驗證很復雜,SERDES 已成為 SoC 模塊不可或缺的一部分。隨著 SERDES IP 模塊現已推出,它有助于緩解任何成本、風險和上市時間問題。

2023-10-23 14:44:59 449

449

電子發燒友App

電子發燒友App

評論