1、 引言

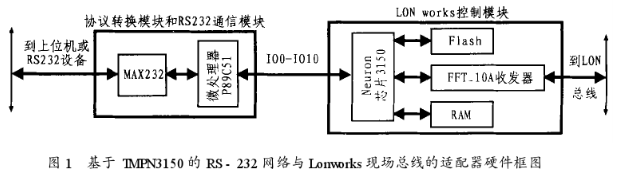

在傳統(tǒng)的工業(yè)控制中,現(xiàn)場的傳感器與控制器之間總是以4~20mA的直流電流或1-5V的直流電壓來傳遞信息的。隨著工業(yè)控制技術(shù)的不斷發(fā)展,工業(yè)控制系統(tǒng)正向著數(shù)字化、智能化、網(wǎng)絡(luò)化和開放化的方向發(fā)展。因此,模擬傳輸漸漸被數(shù)字傳輸所取代。而現(xiàn)場總線(FieldBus)則可以很好地適應(yīng)工業(yè)控制技術(shù)發(fā)展的趨勢,是對成熟控制系統(tǒng)結(jié)構(gòu)的根本變革。LonWorks總線是美國Echelon公司于1991年提出的一種現(xiàn)場總線,它采用面向?qū)ο蟮脑O(shè)計方法,通過網(wǎng)絡(luò)變量把網(wǎng)絡(luò)通信設(shè)計簡化為參數(shù)設(shè)置。LonWorks技術(shù)的核心是神經(jīng)元(Neuron)芯片,這個神經(jīng)元片中有三個8位的CPU,它們不僅可以用作LonWorks總線的通信處理器,而且還可以用作采集和控制的通用處理器。本文介紹具有串行口的A/D芯片TLC0832與作為通用處理器的神經(jīng)元芯片的兩種接口實現(xiàn)方法。

2、 Neuron芯片和TLC0832的基本特性

2.1 Neuron芯片的基本特性

LonWorks網(wǎng)絡(luò)是由節(jié)點構(gòu)成的,每個節(jié)點包括一片Neuron芯片、傳感和控制設(shè)備、收發(fā)器和電源。其中,Neuron芯片是節(jié)點的核心,它具有3個CPU:CPU-1是介質(zhì)訪問處理器,CPU-2是網(wǎng)絡(luò)處理器,CPU-3是應(yīng)用處理器。Neuron芯片家族中的最初成員是Neuron 3120xx和Neuron 3150芯片。3120xx芯片中包括EEPROM、RAM、ROM存儲器,而3150芯無內(nèi)部ROM,但擁有訪問外部存儲器的接口,其尋址空間可達(dá)64kB,可用于開發(fā)更為復(fù)雜的應(yīng)用系統(tǒng)。

Neuron芯片通過11個引腳(IO-0~I(xiàn)O-10)與外部硬件相連。這11個引腳可定義34種I/O對象,用戶可根據(jù)實際應(yīng)用需要在應(yīng)用程序中定義不同的I/O對象,如直接的I/O對象、并行I/O對象、串行I/O對象和定時器/計數(shù)器輸入/輸出對象等。

2.2 TLC0832的基本特性

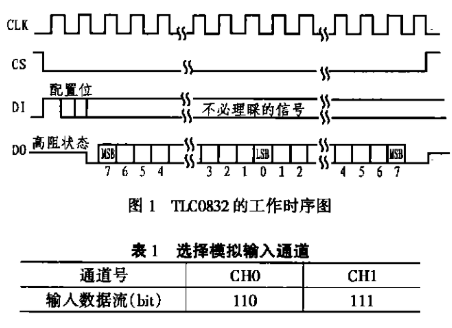

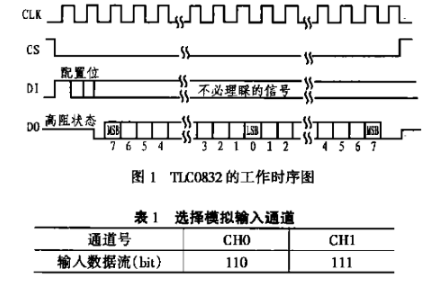

TLC0832是八位逐次逼近模數(shù)轉(zhuǎn)換器,它有兩個可選擇的輸入通道。TLC0832的特點如下:

*8位分辨率;

*可和微處理器接口或獨立使用;

*可滿量程工作或使用5V基準(zhǔn)電源;

*具有單通道或多路器選擇的雙通道,并可選擇單端或差分輸入;

*采用單5V供電,輸入范圍為0~5V;

*輸入和輸出與TTL和CMOS兼容;

TLC0832處于工作狀態(tài)時,置CS端方可啟動轉(zhuǎn)換,并使所有的邏輯電路使能。CS在整個轉(zhuǎn)換過程中必須置為低電平,接著從處理器接受一個時鐘。當(dāng)一個時鐘的時間間隔被自動插入后,可以使多種轉(zhuǎn)換器選定的通道穩(wěn)定。而當(dāng)DO脫離高阻狀態(tài)時,可提供一個時鐘的時間間隔的前導(dǎo)低電平,以使多路器穩(wěn)定。SAR比較器用于對電阻梯形網(wǎng)絡(luò)輸出的逐次信號和輸入模擬信號進(jìn)行比較,比較器輸出則用于表示劉大于還是小于電阻梯形網(wǎng)絡(luò)的輸出。在轉(zhuǎn)換過程中,轉(zhuǎn)換的數(shù)據(jù)同時從DO端輸出,并以最高位(MSB)開頭。在經(jīng)過8個時鐘后,轉(zhuǎn)換完成,CS變高,內(nèi)部所有寄存器清零,此時,輸出電路變?yōu)楦咦锠顟B(tài)。如果希望開始另一個轉(zhuǎn)換,CS必須有一個從高到低的跳變,且后面應(yīng)緊跟著輸入地址數(shù)據(jù)。TLC0832的輸入配置可在多路器尋址時序中進(jìn)行,多路器地址通過DI端移入寄存器。用多路器地址選擇模擬輸入通道的方法如表1所列,其工作時序圖如圖1所示。

3、 Neuron和TLC083的兩種接口方法

3.1 基于Neuron芯片Neurowire I/O模式方案

如上所述,Neuron芯片TMPN3150的11個I/O腳有多種I/O模式,這里用的是Neurowire模式。這種方式把TMPN3150的I/O腳定義為Neurowire I/O對象,即同步全雙工串行通信模式,它每次最多可傳送255比特的數(shù)據(jù)流。Neurowire I/O對象可配置為主控方式和被控方式。當(dāng)為主控方式時,IO8為移位時鐘信號輸出端,IO9為串行數(shù)據(jù)輸出端,IO10為串行數(shù)據(jù)輸入端,IO0~I(xiàn)O7可任選一個作為片選信號線。若Neuron芯片的輸入時鐘為10MHz時,則IO8的輸出時鐘頻率可選為1、10或20kb/s;當(dāng)為被控方式時,IO8為移位時鐘信號輸入端,IO0~I(xiàn)O7可任選一個作為時間溢出信號引腳。

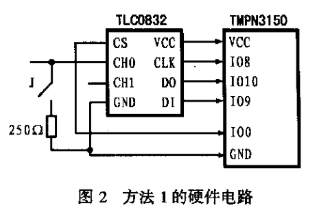

a. 方法1的硬件實現(xiàn)

基于Neuron芯片的Neurowire I/O模式的硬件電路如圖2所示。圖中,IO0輸出片選信號。圖1中的輸入只畫了一路CH0,另一路CH1與CH0相同。當(dāng)輸入為電壓信號時,J斷開;輸入為電流信號時,J連通。

b. 方法1的軟件實現(xiàn)

神經(jīng)元芯片的編程是采用Neuron C語言來完成的。Neuron C是專門為Neuron芯片設(shè)計的編程語言,它有著豐富的函數(shù)庫,可直接完成許多復(fù)雜的任務(wù)。

基于Neuron芯片的Neurowire I/O模式的A/D接口程序如下:

//////// IO Objection ////////

//定義為Neurowire主模式,A/D芯片的主選信號由IO0輸出初始化為1

IO-8 neurowire master select (IO-0) ioA2D;;

IO-0 output bit ioA2Dselect =1;

IO-1 input bit start_adc;

# pragma ignore_notused ioA2Dselect

//////// function declare////////

unsigned long adc(unsigned long analog_addr);

////////function definition////////

//A/D轉(zhuǎn)子函數(shù)

unsigned long adc(unsigned long analog-addr)

//形參analog_addr傳遞要選擇的通道,選擇CH0時,analog_addr=0x06,選擇CH1時,analog_addr=0x07

{

unsigned long adc_info;

unsigned long digital_out;

adc_info = (analog_addr 《《 13);

io_in(ioA2D,&adc_info,16); //選擇通道,同時接收轉(zhuǎn)換的結(jié)果

digital_out=adc_info & 0x0ff0;

digital_out=digital_out 》》4;

return digital_out;

}

由于eurowire I/O對象是雙向的,即輸入、輸出同時進(jìn)行。因此,調(diào)用io_in(ioA2D,&adc_info,16)時啟動了16位的雙向數(shù)據(jù)傳輸,該命令可將adc_info中的數(shù)以比特流的形式從IO-9輸送到TLC0832,同可時通過IO10從TLC0832的DO腳讀入16位數(shù)并放入adc_info。由TLC0832的工作時序圖(圖1)可以看出,接收到的16位數(shù)中的第5位到第12位就是轉(zhuǎn)換結(jié)果,所以做了后面的處理。

3.2 基于Neuron芯片的比特I/O模式方案

TMPN3150和TLC0832的第二種接口實現(xiàn)方法是把TMPN3150的I/O腳定義為比特I/O對象,它可用以監(jiān)控與Neuron芯片相連的I/O設(shè)備中某個引腳上的邏輯狀態(tài),其中“0”為低電平,“1”為高電平。

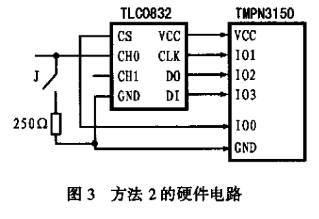

a. 方法2的硬件實現(xiàn)

方法2的硬件電路如圖3所示。圖中,輸入通道只畫了一路CH0,另一路CH1與CH0相同。當(dāng)輸入為1-5V的電壓信號時,J斷開;當(dāng)輸入與4-20mA的電流信號時,J連通。

b. 方法2的軟件實現(xiàn)

Neuron C語言是從ANSI C中派生出來的,相對于ANSI C而言,它進(jìn)一步擴展了用以支持由Neuron芯片中的固件提供的各種運行特性。

方法2的A/D接口程序如下:

////////IO Objection////////

//將IO腳定義為比特IO對象,

IO-2 input bit io-do;

IO-0 output bit cs;

IO-3 output bit di;

IO-1 output bit clk;

////////function declare////////

int adc(int adc-addr);

///////function definition//////

//A/D轉(zhuǎn)換子函數(shù)

int adc(int adc_addr)

//形參analog_addr傳遞要選擇的通道,選擇CH0時,adc_addr=0x60;選擇CH1時,adc_addr=0x70//

{

int adc_inbit,digital_out=0;

io_out(cs,0);

io_out(di,0);

for(i=0;i《3;i++)//選擇通道

{

io_out(clk,0);

adc_addr=adc_addr《《1;

if(adc_inf0 &0x80)==0x80

io_out(di,1);

else

io_out(di,0);

io_out(clk,1);

}

io_out(clk,0); //一個時鐘的間隔

io_out(clk,1); //以使多路器穩(wěn)定

for(i=0;i《8;i++) //接收轉(zhuǎn)換結(jié)果

{

io_out(clk,0);

if(io_in(io_do)= =1)

{

adc_inbit=1;

adc_inbit=adc_inbit《《(7-i);

digital_out=digital_out+adc_inbit;

}

io_out(clk,1);

}

io_out(cs,1)

return digital_out;

}

4、結(jié)束語

Neuron芯片不同于普通的微處理器,本文介紹的神經(jīng)元芯片與A/D芯片TLC0832的兩種接口實現(xiàn)方法各有利弊,具體表現(xiàn)如下:

(1)方法1是Neuron芯片所特有的,而方法2較通用,它不僅適用于Neuron芯片,而且適用于各種有I/O腳的微處理芯片;

(2)方法1的硬件要求比較嚴(yán)格,可選的I/O腳只有一個,即片選信號輸出腳,而方法2腳把幾個與TLC0832相連的I/O腳視為普通的I/O腳,隨便哪個I/O腳都可與TLC0832相連(如果Neuron芯片的IO8、IO9或IO10已用,那只能選方法2了);

(3)方法1編程較短,但不但于調(diào)試,而方法2則編程較長,但較為直觀,而且便于調(diào)試;

(4)方法1的CLK占空比和時鐘速率較為穩(wěn)定,而方法2的CLK占空比與指令執(zhí)行時間有關(guān)。對于常用單片機的人來說,方法2較易上手,則方法1則更專業(yè);方法2的硬件接法更靈活,但編程較長……總之,使用這兩種方法應(yīng)根據(jù)實際情況靈活地作出選擇

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評論