數據采集系統中,通過微機COM端口的RS-232串行通訊及通過微機并行端口的并行通訊具有開發使用方便的特點,前者可與工作于11.0592MHz晶振下的8052單片機在波特率115200時,實現10ksps(samples per second)的連續數據采集和傳輸而不丟失數據,若要達到更高速率的數據采集,可以通過并行口通訊方式實現。當前微機均可通過配置CMOS,將基地址為 378H的并行口設置為EPP模式以支持通過數據口雙向傳輸通訊,并由芯片硬件自動產生握手信號,實現高速傳輸的目的。

為充分實現EPP模式的高速特性,外設應當及時響應EPP的握手信號,當數據采集系統工作于非實時多任務的WIN98操作系統環境下,為實現數據高速、均勻性采樣,還需要在外設配置必要的數據緩沖存儲器。如果數據采集速率低于EPP模式數據讀入平均速率,就可能實現數據的連貫有效性。有資料說明在 EPP模式,可實現500kBytes/s以上的傳輸速率,這表明通過EPP模式,可以實現500ksps的數據采集系統。通過對EPP模式的深入實驗分析,發現要實現500ksps,外設硬件及微機軟件程序均要采取一些策略:硬件上必須配置FIFO數據緩沖存儲器,才能協調數據采集嚴格的時間間隔要求與數據傳輸給微機的非實時、非均勻性之間的矛盾;軟件程序方面應當采取雙字讀的方法,否則EPP模式下僅能實現250kBytes/s數據讀取可行性。

1、 EPP模式讀取速率的實驗分析

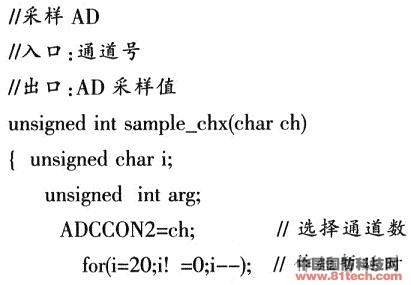

圖1為實驗EPP模式讀取速率的電路,實驗程序為

圖1

Delphi結合內嵌匯編語言,涉及EPP讀取的關鍵代碼如下:

VAR

STARTTIME,STOPTIME,DELAY:INT64;

NUMBERONGWORD;

QUERYPERFORMANCECOUNTER(STARTTIME);

FOR NUMBER:=0 TO 999999 DO

BEGIN

ASM

MOV DX,$37C

IN AL,DX

MOV RESULT,AL

END;

END;

QUERYPERFORMANCECOUNTER(STOPTIME);

DELAY:=STOPTTIME-STARTTIME;

END;

此為循環1000000次讀取EPP數據口程序,循環僅為方便用計時及示波器觀察而設,并在執行前后分別讀取系統計數值,DELAY值除以1.2后為執行花費的時間(單位為微秒),執行前先通過對地址379H的D0位寫入高,使該位為低(注意:對該位寫入低通常不能達到使該位變為低的目的,只有采取寫入高才能使該位變為低),以清除EPP超時位,當A、B點均為低時,可實現最快的EPP握手,若A為高、B為低時,由于EPP周期開始時滿足WAIT為低的要求,EPP自動在DATASTB處輸出低,但因WAIT沒有出現表示應答的高狀態,EPP在延時10μs后,將DATASTB恢復為高以結束該次EPP訪問過程,并置超時位。稍后因WAIT為低再次開始一次EPP訪問過程,如果B為高,則WAIT為高,不能滿足EPP的開始條件,故DATASTB保持為高,EPP在延時10μs后結束該次EPP訪問過程,并置超時位。在發生超時情況下,數據仍然可正確讀入(這一特性與所查資料有出入),此結論可通過對比循環前后時間差來及實際讀入數據值證實。

圖2

注意程序循環中并未執行清除EPP超時位的指令,根據筆者實驗,即使已發生EPP訪問超時,也不影響下一次的EPP讀周期(包括對37BH的地址讀及對 37CH的數據讀),但超時對EPP寫周期有影響,在清除超時位之前,EPP寫周期無效(因本文不涉及EPP寫周期的內容,此處不再展開探討)。在圖2所示意波形中,當有正確握手的EPP讀周期執行時間約為1.5μs,此時間是字節模式下一次有效EPP訪問所需最短時間,在這段時間內,“IN AL,DX”這一條指令占據了約90%以上的訪問時間,驗證此點僅需臨時屏蔽“IN AL,DX”指令,并比較所花費的時間差別即可。1.5μs相當于接近700kBytes/s的數據讀速率。如果以“IN EAX,DX”替代“IN AL,DX”指令,可以充分利用EPP模式下硬件將4個8位數自動合并為1個32位數的特性,在一次I/O訪問中由硬件自動產生4個DATASTB負脈沖從而實現4個字節的輸入。因為一次字節模式的I/O訪問所費時大約間需要1.5μs,減少這類指令的執行次數有利于實現更高速的EPP訪問過程,經實驗發現以4字節方式訪問的EPP過程可以在3.2μs內讀取一次,即平均每字節需0.8μs,相當于1.2MBytes/s,此實驗結果是基于外設可以連續不斷的輸送數據理想前提,實際上要實現有效的數據傳輸,可得到的速率要低于該值。

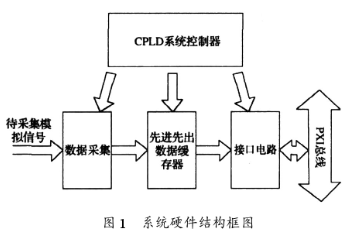

2、 WIN98下高速EPP接口的構成

在WIN98環境下,由于非實時多任務的特性,運行于RING3的應用程序頻繁被操作系統打斷,這決定了靠軟件無法實現連續均勻的數據采樣,只有在硬件上配置數據緩沖存儲器并及時傳入微機以免數據緩沖存儲器溢出。只要保證一定深度的數據緩沖存儲器,且滿足數據傳輸平均速率大于數據采樣速率,就能將所采集的數據傳入微機的大容量內存,以備處理。在硬件構成方面,為以較低代價獲得大容量的FIFO數據緩沖存儲器,采取CPLD器件結合512KB的SRAM方式,實現,由CPLD器件完成讀寫控制的FIFO特性及EPP模式的應答握手信號。接口結構及CPLD內部功能模塊見圖3所示,數據在CPLD控制下,以 2μs 的固定速率存入SRAM環狀連續增量地址,因為EPP模式讀取速率與數據采樣的固定速率是異步的,控制邏輯為保證2μs 的固定采樣速率,當采樣時間點到達時,不論當前是否處于EPP應答處理期間,優先執行數據采樣,因為處理是在系統時鐘脈沖驅動下的硬件行為,僅存在固定的傳輸延時,故兩次采樣間隔是嚴格保證的。

圖3

EPP模式的讀取平均速率必須高于數據采樣速率,一旦FIFO數據讀空必須讓微機正確處理,由前述實驗可知,每次字節方式I/O執行時間約為1.5μs,如果通過在EPP的狀態口(379H)的保留位輸入代表FIFO讀空的信號,則每完整讀取均要執行兩次I/O指令:EPP數據讀及EPP狀態讀,至少需 3μs完成讀取一個字節,這也是通常方式能達到的最快有效讀取速率。當采用雙字讀讀及EPP狀態讀的方式時,需4.8μs完成4個數據字節讀取,但此方式需要處理的一個問題:由于雙字方式EPP數據讀由硬件自動產生4個EPP數據讀周期,當其執行完畢,執行EPP狀態讀發現FIFO已空,微機軟件無法判別在從第幾個EPP數據讀周期開始FIFO為空,從而影響對數據隊列的正確排序,故CPLD邏輯應當在FIFO隊列還有至少4個未讀數據時必須發出讀空信號,微機程序應當在每次EPP開始前執行讀取狀態口的指令,以決定是否可以開始EPP數據讀周期,從上分析可以看出為實現有效的EPP數據讀取,平均每字節至少需要1.2μs,即可以獲得最快約800kBytes/s的數據傳輸速率。因500ksps的數據采集設計速率僅略低于800kBytes/s的數據傳輸速率,考慮WIN98工作環境,配置大容量的FIFO十分必要,采用大容量SRAM與CPLD器件構成FIFO,具有成本較低的優點,通過使用VHDL的行為描述,經CPLD器件開發軟件的編譯、綜合、仿真、適配、下載,實現所需要的控制邏輯。根據設計,當數據鎖存輸出的下一個時鐘脈沖(即83ns后),WAIT將輸出為高電平,EPP在此時讀取數據口信號,如果不采用外部緩沖驅動器,數據上升過程將耗時80ns,對EPP數據接收可靠性有不容忽視的影響,為減小電纜電容的影響,數據輸出使用了74ALS574芯片作緩沖,其高電平輸出能力達15mA,是ispLSI1032高電平輸出能力的3.5倍,在電纜電容有100pF 時,23ns可達到3.5V的邏輯高電平,保證數據接收可靠性。

仿真波形參見圖4,出于方便,仿真時鐘設置為12.5MHz。系統每24個時鐘脈沖產生一次數據采集,仿真采樣速率521ksps。數據由 DIN[7:0]輸入,通過CPLD內部數據輸入觸發時鐘(該時鐘同相緩沖后形成RAMOE脈沖,持續寬度為兩個系統時鐘)的上升沿鎖存,并控制地址選擇器將寫地址輸出到ABUS上,在RAMOE為高期間,DBUS開放三態數據觸發器輸出使能,使被鎖存的8位數據經DBUS輸出,數據輸入觸發時鐘過后一個系統時鐘,RAMWR產生一個系統時鐘寬度的負脈沖,控制SRAM將DBUS上的數據寫入,再下一個系統時鐘的上升沿,RAMWR變高,RAMOE變低使 SRAM輸出有效,三態數據觸發器恢復為高阻狀態,ABUS變為待讀數據地址,完成一次數據采集、存儲過程。微機軟件執行EPP數據讀前先讀取狀態口(379H)以判別READ_EN是否有效,當READ_EN為高時,可以執行EPP數據讀周期,CPLD在同步DATASTB_IN的下降沿后,產生一個寬度的OUTCLK輸出鎖存脈沖,其上升沿將相應待讀地址的SRAM數據鎖存于外部74ALS574,下降沿使WAIT_OUT上升,形成EPP模式的應答握手信號。WAIT_OUT在DATASTB_IN的上升沿異步復位以響應下一次EPP模式訪問。數據寫入優先于數據讀取,當到達固定的采樣間隔點時,CPLD總是推后OUTCLK及WAIT_OUT 的執行,待采樣并存儲完畢才繼續被暫緩的EPP應答,在設計中,數據的采樣及存儲需要兩個系統時鐘周期共167ns,遠低于EPP的超時參數,故有充分的時間正確地完成EPP握手。圖4仿真了數據讀空狀態,在圖中部,READ_EN信號存在一個低電平區域,此負脈沖前,根據RAMWR個數可知當時采樣了 11個數據,根據OUTCLK個數可知讀取了8個數,剩下3個數不足以提供EPP執行雙字讀的操作,如果此時微機需要訪問EPP,在其對狀態口的讀取中,因得知READ_EN無效而暫緩EPP的執行,當再次完成一次數據采樣后,達到至少存在4個未讀數據的條件,READ_EN重新變為有效,可供微機讀取。

為與微機接口,附加部分其它口線,其中RESET使CPLD全局復位,74ALS574的OE腳由微機控制輸出是否為高阻,在程序設定數據端口作為輸入使用前,保持該腳為高電平,使74ALS574輸出為高阻態,雖然使用的是EPP模式的地址選通信號腳作控制,但程序中并無EPP模式的地址讀寫指令,此腳的變化直接由EPP端口的控制口(37AH)的D3位控制,另外一般D5位為讀寫方向控制,將該位置為高,使數據端口作為輸入使用。SYN與RAMWR有固定(芯片編程時設定)的相位關系,作為數據采集的同步控制用,當選用MAX114芯片且配置為流水線模式(Pipelined Mode)時,MAX114的WR及RD腳共同連接至SYN腳,此信號波形是與RAMWR同步下降但持續時間為500ns的負脈沖信號,由A/D芯片 MAX114與SRAM及CPLD等器件可構成EPP模式下500ksps的連續數據采集接口。

微機的數據接收是個環狀循環體后臺程序,頻繁對端口的訪問占據大量CPU時間片,為保證對用戶操作的響應,應采取多線程方式的程序結構。微機軟件部分采用 Delphi程序設計語言,端口訪問使用內嵌匯編語言,程序中開辟一塊20-100M字節或更大的環型數據區,可根據實際需要考慮。

責任編輯:gt

電子發燒友App

電子發燒友App

評論