介紹了PXI總線儀用模塊的結構和特點,描述了低成本FPGA器件開發模塊的各種功能。

重點描述了PXI儀用模塊必須具有的PCI/PXI總線接口、精密時基和觸發控制器的實現,最后探討了PXI儀用模塊針對EMC應采取的措施。實際應用表明所設計的PXI儀用模塊完全符合PXI硬件規范,達到了設計要求。

PXI規范定義了一種功能強大的儀器平臺,用于測量和自動化領域。PXI是基于CPCI平臺、并附加儀器規范(如EMI/RFI、機械接口、冷卻、觸發、設備同步、軟件接口等)所構成的儀用平臺。測試系統的同步和控制是眾多功能測試應用的先決條件,它們依賴于事件檢測、激勵/響應或相位相關,而PXI提供了滿足這種要求所需的電氣擴展信號,包括用于儀器同步的系統參考鐘PXI_CLK10、PXI TRIG總線、時間非常精密的PXI_STAR觸發總線以及用于相鄰單板通信的局部總線。PXI儀用系統較GPIB、VXI等儀器系統具有較好的性價比,因而越來越多地被從事自動測試測量的工程技術人員選用或開發PXI儀器。如何設計符合PXI規范特別是儀用要求的PXI模塊就成了關鍵。本文在PXI規范及PXI硬件規范的基礎上,借助多通道高速數據采集模塊的設計及其應用,揭示PXI儀用模塊的設計需要的關鍵技術。

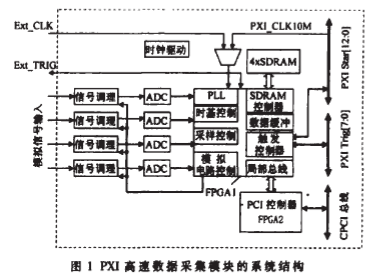

1、 PXI總線數據采集模塊的結構

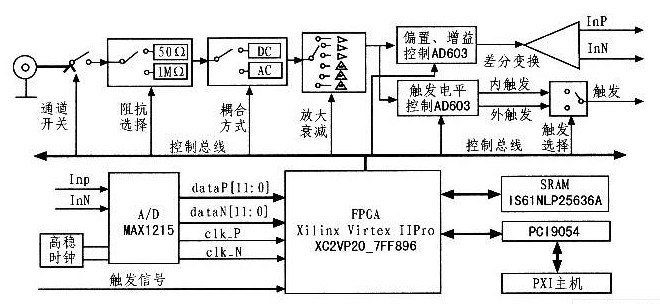

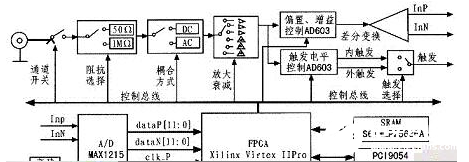

PXI總線四通道高速數據采集模塊是高速、高精度的自動測試模塊。整個采集模塊從電路上可分為模擬信號調理及A/D轉換、系統控制器、PCI總線接口等幾個部分。系統控制器包括模擬信號的控制與設置、時基源控制、觸發源設置、觸發模式設置、采樣控制、數據緩沖、數據存儲、數據傳輸等。

PXI高速數據采集模塊結構如圖1所示。信號調理(Conditioning)及A/D轉換部分決定了模擬信號采集的性能,時基控制電路為模塊和其他PXI模塊提供采樣和同步基準鐘,觸發控制器用于接收或發送觸發信號,數據緩沖和SDRAM控制器用于數據在板緩存,局部總線控制器用于主機與各控制器進行通信。各控制器均采用Verilog HDL實現。

其中,ADC選用AD9235-65,FPGA1、FPGA2分別選用ALTERA公司的EP1C6Q248和EP1C6Q144,在板數據緩存選用Microchip公司的MT48LC8M16A2。

采集模塊有四個模擬通道,每個模擬通道都有獨立的信號調理電路、ADC和在板數據緩存。在系統控制器FPGA1的控制下,當滿足預設的觸發條件時,將A/D轉換后的數據送入SDRAM,然后計算機將數據讀入進行分析和保存。

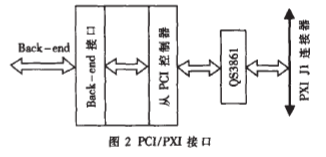

2 、PCI/PXI接口的實現

PCI/PXI接口需要設計PCI控制器、Back-end接口,并且需要滿足CPCI規范的電氣要求。這些電氣要求包括電源解耦、信號分支(stub)終結、信號分支長度約束、熱插拔、3.3V/5V信號環境等。多通道高速數據采集模塊采用Verilog HDL在EP1C6Q144中實現32位Slave PCI控制器、Back-end接口,通過它來實現儀器模塊與計算機之間的通信。

通常為滿足電信等應用,當CPCI單板出現故障時,要求在整個系統不停機的情況下允許帶電拔出故障板并插入備份板進行維護。一般情況下PXI儀器不需要熱插拔,3U尺寸的PXI卡外形又很小,布局布線不便。本設計沒有采用熱插拔。

PXI模塊的PCI信號應能兼容PCI 3.3V/5V信號環境。如果PXI底板的碼鍵是鎘黃色則是3.3V信號環境,亮藍色則是5V信號環境,沒有碼鍵則為3.3V/5V通用信號環境。本設計采用IDT的電平轉換芯片QS3861,以兼容PCI 3.3V和PCI 5V信號環境。同時,芯片導通時的典型阻抗為10Ω,滿足信號stub終結電阻的要求。

3 、PXI儀器同步機制的實現

被測對象(DUT)可能有數個緩變信號、混合信號,或眾多個相互關聯的信號。數個緩變信號的測試只需簡單測試設備就可以完成,實時時鐘也可以保證時間精度。混合信號和眾多相互關聯信號的測試,既有測試也有激勵,需要一臺或多臺儀器,所構成的測試系統就是綜合測試系統,系統中的每個模塊必須具有精確的同步和控制以達到同時操作。從這個角度考慮,通常要求儀器底板提供一個精密的系統參考鐘、一套觸發總線、通過前面板提供接收或發送到其他儀器的時鐘和觸發信號接口。PXI底板包括系統參考鐘、PXI觸發總線、星形觸發總線等資源。開發人員可以利用這些資源設計精密而靈活的時基和觸發控制器,以實現多臺儀器的同步和控制。

(1)PXI底板提供了一個公共的參考時鐘,每個外設槽都有一個PXI_CLK10 TTL鐘,從鐘源到每個槽的布線等長,兩槽之間的信號偏移小于1ns。

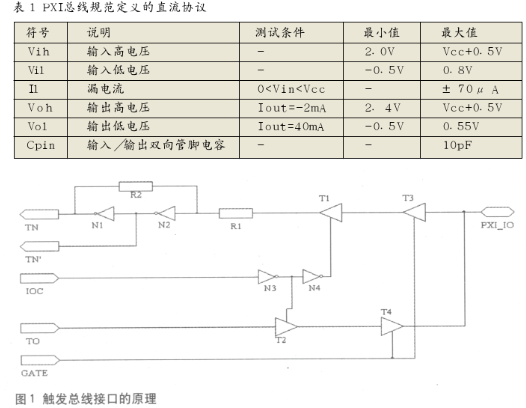

(2)PXI 規范定義了八個觸發信號用于模塊間的同步和通信,時鐘、觸發和握手信號共享這個觸發總線,覆蓋一個總線段。PXI TRIG總線允許傳輸不同頻率的采樣時鐘,多個模塊可以直接共享這個采樣時鐘,其時鐘脈沖的傾斜精度小于10ns。PXI規范建議采用PXI_TRIG[7]信號線,用于發送或接收采樣時鐘。在上電時,這些信號應處于高阻態。

(3)PXI提供了一個超高性能的星形觸發總線,同參考時鐘一樣,星形觸發信號是由位于第一外設槽的星形觸發控制器將信號點對點沿著等長的信號線傳送給其他外設槽,其信號抖動小于1ns,覆蓋兩個總線段。

對于PXI儀用模塊的設計,應考慮其在綜合測試系統中的應用,前面板至少需要一個時鐘輸入、一個雙向觸發線,結合儀器本地自洽的時鐘和觸發總線,方能建立一套完備的同步機制。

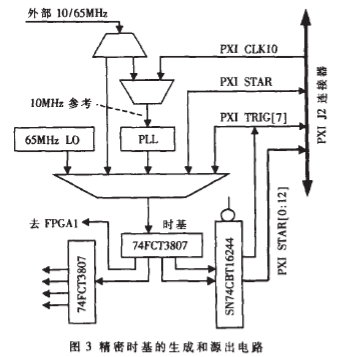

3.1 PXI儀用模塊精密時基的設計

通常一個PXI儀用模塊應有三個時基源: PXI_CLK10參考時鐘、外部(前面板)10MHz參考時鐘或65MHz時基、PXI_TRIG[7]或PXI_STAR提供的采樣鐘。模塊精密時基的設計包括時基的生成和傳送。由于A/D轉換器的采樣時鐘頻率為65MHz,所以模塊的時基頻率可以定為65MHz。如果利用10MHz參考時鐘,還必須通過PLL進行倍頻,顯然倍頻系數不是整數。當不同的模塊利用PXI_CLK10獲取65MHz采樣鐘作為時基時,不同模塊間的采樣鐘很難達到相位同步。為了保證所有模塊同步,如前所述,可將這個采樣鐘通過PXI_TRIG、PXI_STAR[0:12]傳送給其他外設槽。對于多臺儀器的同步應用,最好通過用戶前面板由外部提供時基源。

由于有多個時基源,且通常時鐘的電平是TTL電平,可采用5V耐壓的電平轉換多路復用/解復器進行選擇。這里選用SN74CB3T3253和SN74CBT16244,其傳播時延均小于0.25ns。EP1C6Q248內部有兩個PLL,一個PLL用來從10MHz參考鐘獲取時基,一個用于獲取數據傳輸和SDRAM控制器的80MHz時鐘。精密時基的獲取和源出電路如圖3所示。時基源的選擇和時基信號的源出由用戶通過軟件進行配置。

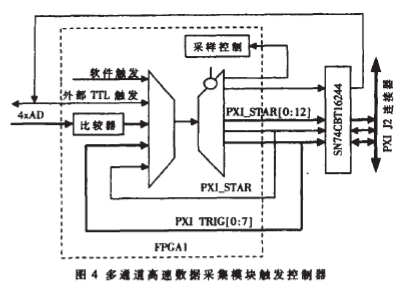

3.2 觸發控制器的設計

除了上述的精密時基,儀器同步機制的另外一個關鍵是觸發系統。不論是簡單測試系統還是綜合測試系統,一個測試系統的動作起點(epoch)依賴于一定的事件。事件有簡單的,如一個信號電平的變化,較為復雜的是多個信號的組合變化,如熟知的邏輯分析儀。對于綜合測試系統,激勵信號和測試信號就更多,而且是相互關聯的,一般意義上,激勵信號集和測試信號集可以用狀態空間來描述和分析,而事件就是狀態空間的某種遷移,單個信號的變化和數個信號的組合變化則是狀態空間遷移的特例。在對同一個被測對象進行測試時,為保證儀器的某個模塊上所發生的事件能同時通知到其他模塊或儀器,通常采用一套硬件觸發機制或精密時鐘協議來實現,如最新架構的LXI儀器采用PTP來實現儀器的同步。實際上硬件觸發機制只有硬件延遲,而采用協議實現同步的儀器的精度很難做到ns級,如LXI的同步精度為亞微秒級,故LXI規范仍保留了硬件觸發機制即A類LXI來滿足對同步精度要求較高的應用。PXI是通過硬件觸發機制來實現儀器同步動作的,通過PXI_STAR總線、PXI TRIG總線實現儀器系統中各模塊發生的事件的相互通知。根據觸發電路的實現方式不同分為PXI同步觸發和PXI異步觸發,同步觸發的參考鐘為PXI_CLK10,有一定的時序要求。

PXI儀用模塊的觸發源有:用于不同儀器同步的外部TTL觸發源(同步觸發或異步觸發)、外部模擬電平變化觸發源(上升沿觸發源或下降沿觸發源)、PXI_STAR觸發源、PXI TRIG觸發源、軟件觸發源等。多通道高速數據采集模塊通過PXI_STAR總線或PXI TRIG總線傳送給其他模塊或通過外部雙向觸發信號線傳送給其他儀器的觸發源采用PXI同步觸發,由于采樣時鐘頻率遠高于PXI_CLK10頻率,在不違背PXI同步觸發時序要求的前提下,同步觸發的參考時鐘可以是儀用模塊的時基,這樣構建的綜合測試系統的同步精度可以達到理想的情況。多通道高速數據采集模塊的觸發結構如圖4所示。最終處理的觸發信號送給FPGA1中的采樣和存儲控制模塊,有選擇地通過PXI觸發總線送給其他PXI模塊,以及通過外部觸發信號送給其他儀器。

此外,根據相對于事件的同步時機的不同,觸發分為負延遲觸發(Pre-trigger)、零延遲觸發(Post-trigger)、正延遲觸發(Delay-trigger)等模式,通過硬件和軟件共同實現。實測表明,當信號發生器的同一個信號輸出到不同采集模塊上,在不同觸發模式下,其波形在時間上完全重合,達到了儀器的同步要求。

4 、EMC設計

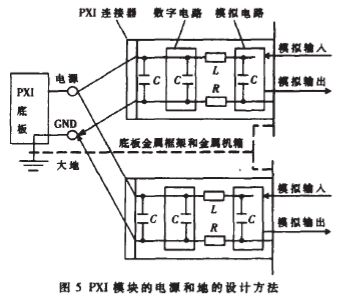

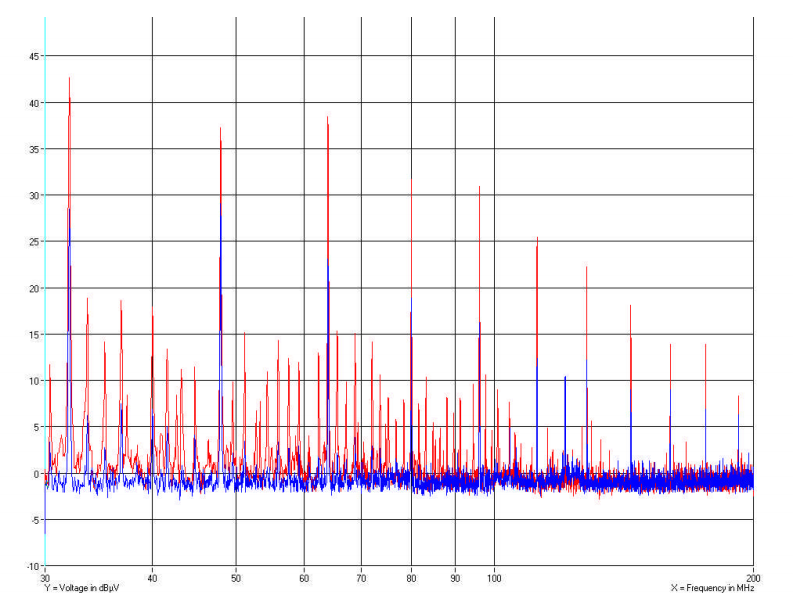

PXI是個儀用平臺,對機箱環境已經做了充分的EMC設計,PXI底板通過PXI J1、J2連接器向PXI模塊供電。PXI模塊通常分為模擬和數字兩個部分,模擬部分靠近前面板,數字部分靠近PXI連接器。為了增強PXI儀用模塊的抗干擾性能并避免對其他模塊的干擾,PXI模塊還需要針對PXI機箱的結構特點精心設計電源,特別是參考地平面的安排。

由于儀用模塊通常是模/數混合電路,將模擬地與數字地隔離,模擬地與前面板相連,則數字電路的電流回路通過PXI連接器回到底板地,模擬電路的電流回路只能通過前面板→PXI底板的金屬框架(或者金屬機箱)這一通路直接流回大地,有效地避免了數字電路通過電源或地對模擬電路的干擾,如圖5所示。但兩個地若完全隔離,熱拔時前面板與PXI底板和機箱的聯結將脫離,模擬電路的電流回路斷開,造成靜電無法釋放,因此在兩個地平面之間串上一個比數字地到底板地之間的阻值高得多的電阻來解決模擬電路的靜電釋放問題,這個電阻值通常在10Ω~100kΩ之間選擇。模擬電源采用π型濾波,電感兩端的解耦電容分別與數字地和模擬地相連。

電源和地平面的精心設計以及其他EMC技術在設計中的應用可以將噪聲限制在很低的程度,實測表明,模擬電路的系統噪聲只有±1LSB,即±0.09mV。

本文結合PXI高速數據采集模塊的具體設計,揭示了設計與開發符合PXI規范的PXI儀用模塊需要解決的關鍵問題,以及低成本、開發靈活的實現方法。所設計的PXI高速數據采集模塊在簡單測試系統以及導彈綜合測試系統中均得到了很好的應用。

責任編輯:gt

電子發燒友App

電子發燒友App

評論