1. I2S簡介

I2S全稱Inter-IC Sound, Integrated Interchip Sound,或簡寫IIS,是飛利浦在1986年定義(1996年修訂)的數(shù)字音頻傳輸標準,用于數(shù)字音頻數(shù)據(jù)在系統(tǒng)內部器件之間傳輸,例如編解碼器CODEC、DSP、數(shù)字輸入/輸出接口、ADC、DAC和數(shù)字濾波器等。除了都是由飛利浦定義外,I2S和I2C沒有任何關系。

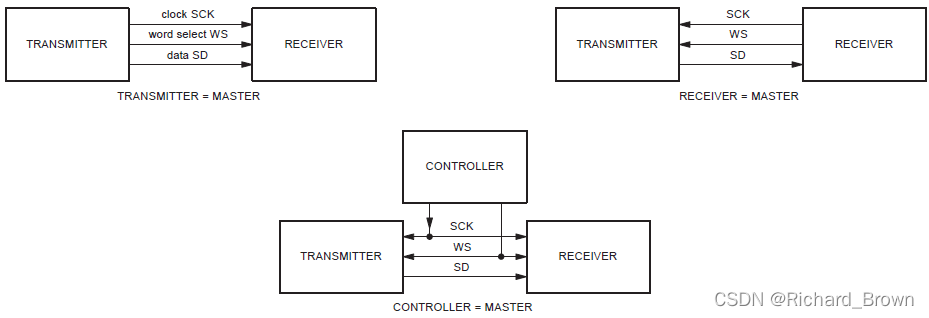

I2S是比較簡單的數(shù)字接口協(xié)議,沒有地址或設備選擇機制。在I2S總線上,只能同時存在一個主設備和發(fā)送設備。主設備可以是發(fā)送設備,也可以是接收設備,或是協(xié)調發(fā)送設備和接收設備的其它控制設備。在I2S系統(tǒng)中,提供時鐘(SCK和WS)的設備為主設備。圖3是常見的I2S系統(tǒng)框圖。在高端應用中,CODEC經(jīng)常作為I2S的主控設備以精確控制I2S的數(shù)據(jù)流。

I2S包括兩個聲道(Left/Right)的數(shù)據(jù),在主設備發(fā)出聲道選擇/字選擇(WS)控制下進行左右聲道數(shù)據(jù)切換。通過增加I2S接口的數(shù)目或其它I2S設備可以實現(xiàn)多聲道(Multi-Channels)應用。

2. 信號定義

在I2S傳輸協(xié)議中,數(shù)據(jù)信號、時鐘信號以及控制信號是分開傳輸?shù)摹2S協(xié)議只定義三根信號線:時鐘信號SCK、數(shù)據(jù)信號SD和左右聲道選擇信號WS。

時鐘信號 Serial Clock

SCK是模塊內的同步信號,從模式時由外部提供,主模式時由模塊內部自己產(chǎn)生。不同廠家的芯片型號,時鐘信號叫法可能不同,也可能稱BCLK/Bit Clock或SCL/Serial Clock

數(shù)據(jù)信號 Serial Data

SD是串行數(shù)據(jù),在I2S中以二進制補碼的形式在數(shù)據(jù)線上傳輸。在WS變化后的第一個SCK脈沖,先傳輸最高位(MSB, Most Significant Bit)。先傳送MSB是因為發(fā)送設備和接收設備的字長可能不同,當系統(tǒng)字長比數(shù)據(jù)發(fā)送端字長長的時候,數(shù)據(jù)傳輸就會出現(xiàn)截斷的現(xiàn)象/Truncated,即如果數(shù)據(jù)接收端接收的數(shù)據(jù)位比它規(guī)定的字長長的話,那么規(guī)定字長最低位(LSB: Least Significant Bit)以后的所有位將會被忽略。如果接收的字長比它規(guī)定的字長短,那么空余出來的位將會以0填補。通過這種方式可以使音頻信號的最高有效位得到傳輸,從而保證最好的聽覺效果。

根據(jù)輸入或輸出特性,不同芯片上的SD也可能稱SDATA、SDIN、SDOUT、DACDAT、ADCDAT等;

數(shù)據(jù)發(fā)送既可以同步于SCK的上升沿,也可以是下降沿,但接收設備在SCK的上升沿采樣,發(fā)送數(shù)據(jù)時序需考慮

左右聲道選擇信號 Word Select

WS是聲道選擇信號,表明數(shù)據(jù)發(fā)送端所選擇的聲道。當:

WS=0,表示選擇左聲道

WS=1,表示選擇右聲道

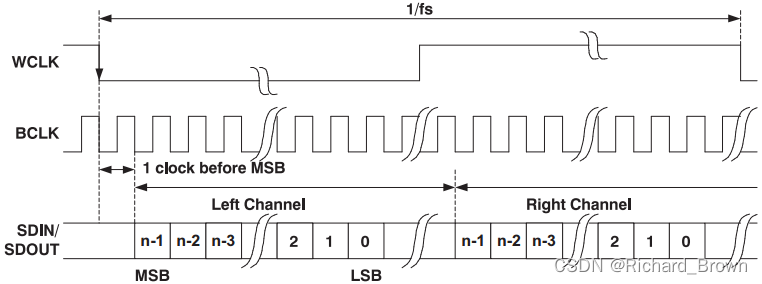

WS也稱幀時鐘,即LRCLK/Left Right Clock。WS頻率等于聲音的采樣率。WS既可以在SCK的上升沿,也可以在SCK的下降沿變化。從設備在SCK的上升沿采樣WS信號。數(shù)據(jù)信號MSB在WS改變后的第二個時鐘(SCK)上升沿有效(即延遲一個SCK),這樣可以讓從設備有足夠的時間以存儲當前接收的數(shù)據(jù),并準備好接收下一組數(shù)據(jù)。

3. I2S操作模式

根據(jù)SD相對于SCK和WS位置的不同,I2S分為三種不同的操作模式,分別為標準I2S模式、左對齊模式和右對齊模式:

I2S Phillips Standard I2S格式

Left Justified Standard 左對齊格式

Right Justified Standard 右對齊格式

I2S模式屬于左對齊中的一種特例,也叫PHILIPS模式,是由標準左對齊格式再延遲一個時鐘位變化來的。時序如下圖所示,左聲道的數(shù)據(jù)MSB在WS下降沿之后第二個SCK/BCLK上升沿有效,右聲道數(shù)據(jù)的MSB在WS上升沿之后第二個SCK/BCLK上升沿有效。

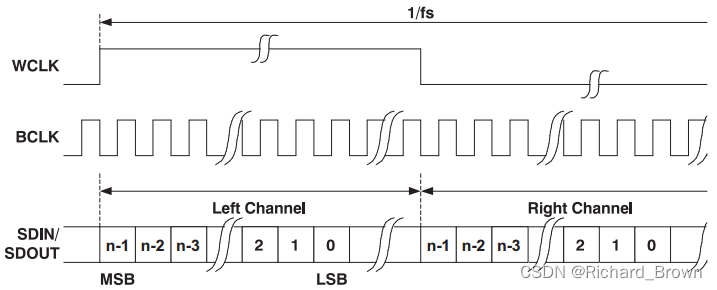

標準左對齊較少使用,下圖為左對齊時序圖,和PHILIPS格式對比可以看出,標準左對齊格式的數(shù)據(jù)的MSB沒有相對于BCLK延遲一個時鐘。左對齊格式的左聲道的數(shù)據(jù)MSB在WS上升沿之后SCK/BCLK的第一個上升沿有效;右聲道的數(shù)據(jù)MSB在WS下降沿之后SCK/BCLK第一個上升沿有效。標準左對齊格式的優(yōu)點在于,由于在WS變化后的第一個SCK上升沿就開始采樣,它不需要關心左右聲道數(shù)據(jù)的字長,只要WS的時鐘周期足夠長,左對齊的方式支持16-32bit字長格式。

標準右對齊也叫日本格式,EIAJ (Electronic Industries Association of Japan) 或SONY格式,下圖為右對齊時序圖。右對齊格式左聲道的數(shù)據(jù)LSB在WS下降沿的前一個SCK/BCLK上升沿有效,右聲道的數(shù)據(jù)LSB在WS上升沿的前一個SCK/BCLK上升沿有效。相比于標準左對齊格式,標準右對齊的不足在于接收設備必須事先知道待傳數(shù)據(jù)的字長。這也解釋了為什么許多CODEC都會提供多種右對齊格式選擇功能。

注:

標準左對齊和標準右對齊模式的LRCK/WS高低電平對應的左右聲道與標準I2S模式的規(guī)定恰好相反!標準左右對齊LRCK/WS高電平對應左聲道,LRCK/WS低電平對應右聲道;而I2S低電平對應左聲道,LRCK/WS高電平對應右聲道!

4. I2S數(shù)據(jù)時鐘(SCK)頻率計算

例如:設聲音的采樣頻率為44.1 kHz,即聲道選擇信號(幀時鐘)WS的頻率必須也為44.1 kHz;左/右2個聲道的量化深度均為16 bit,則I2S的SCK的頻率為:44.1 kHz×16×2=1.4112 MHz

SCK = 采樣率 * 位寬 * 通道數(shù)

WS = 采樣率

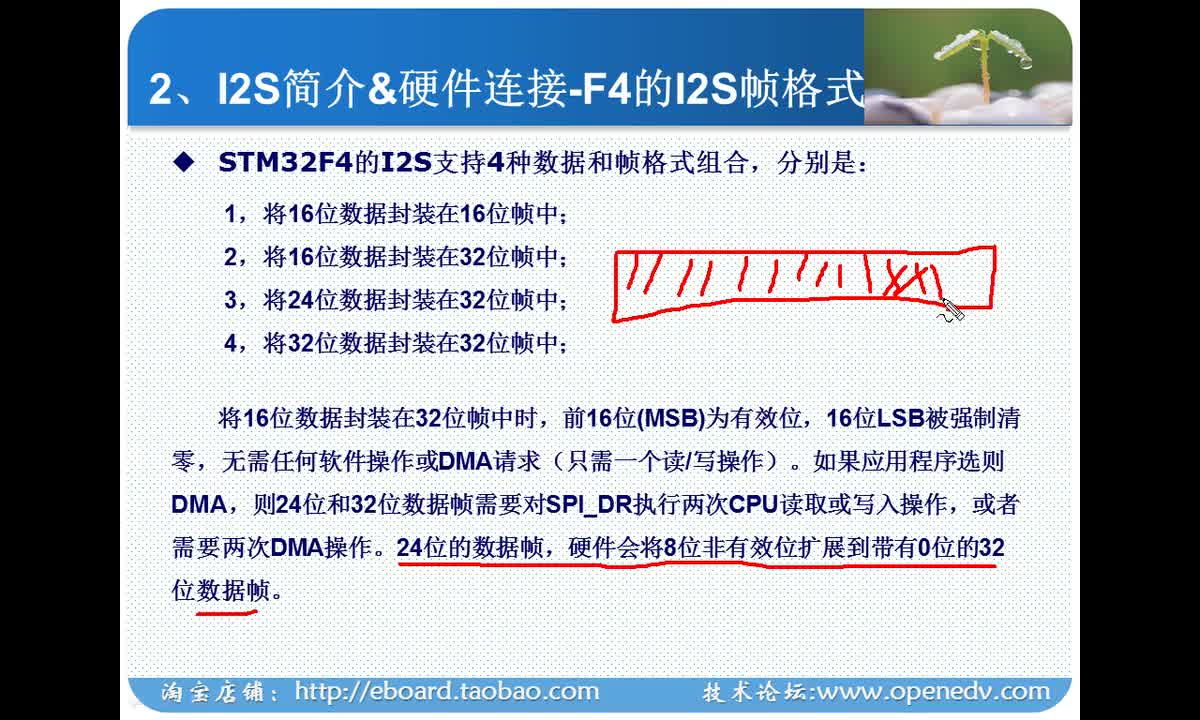

如果需要傳輸20 bit、24 bit或32 bit的左右聲道的數(shù)據(jù),可以提高SCK的頻率,由上式可以計算出需要的SCK的頻率。

PCM接口

1. PCM簡介

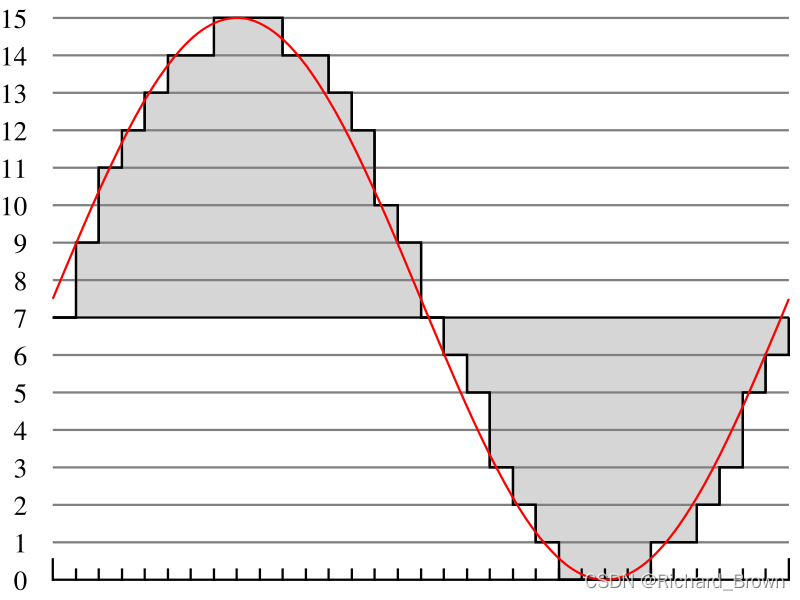

PCM (Pulse Code Modulation) 是通過等時間隔(即采樣率時鐘周期)采樣將模擬信號數(shù)字化的方法。下圖為 4 bit 采樣深度的PCM數(shù)據(jù)量化示意圖。

PCM數(shù)字音頻接口,即說明接口上傳輸?shù)囊纛l數(shù)據(jù)通過PCM方式采樣得到的,以區(qū)別于PDM方式。在音頻領域,PCM接口常用于板級音頻數(shù)字信號的傳輸,與I2S相似。PCM和I2S的區(qū)別于數(shù)據(jù)相對于幀時鐘(FSYNC/WS)的位置、時鐘的極性和幀的長度。其實,I2S上傳輸?shù)囊彩荘CM類型的數(shù)據(jù),因此可以說I2S不過是PCM接口的特例。

相比于I2S接口,PCM接口應用更加靈活。通過時分復用(TDM, Time Division Multiplexing)方式,PCM接口支持同時傳輸多達N個(N>8)聲道的數(shù)據(jù),減少了管腳數(shù)目(實際上是減少I2S的“組”數(shù),因為每組I2S只能傳輸兩聲道數(shù)據(jù)嘛)。TDM不像I2S有統(tǒng)一的標準,不同的IC廠商在應用TDM時可能略有差異,這些差異表現(xiàn)在時鐘的極性、聲道配置的觸發(fā)條件和對閑置聲道的處理等。

TDM/PCM數(shù)字音頻接口的硬件拓撲結構也與I2S相近。

綜合不少廠商的數(shù)據(jù)手冊,筆者發(fā)現(xiàn),在應用PCM音頻接口傳輸單聲道數(shù)據(jù)(如麥克風)時,其接口名稱為PCM;雙聲道經(jīng)常使用I2S;而TDM則表示傳輸兩個及以上聲道的數(shù)據(jù),同時區(qū)別于I2S特定的格式。

2. 信號定義

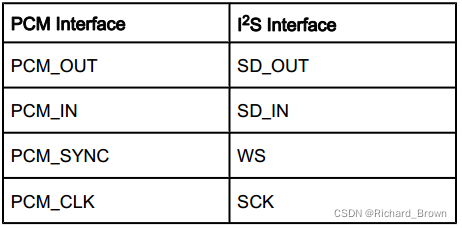

PCM接口與I2S相似,電路信號包括:

PCM_CLK 數(shù)據(jù)時鐘信號

PCM_SYNC 幀同步時鐘信號

PCM_IN 接收數(shù)據(jù)信號

PCM_OUT 發(fā)送數(shù)據(jù)信號

TDM/PCM與I2S接口對應關系見下表:

3. 操作模式

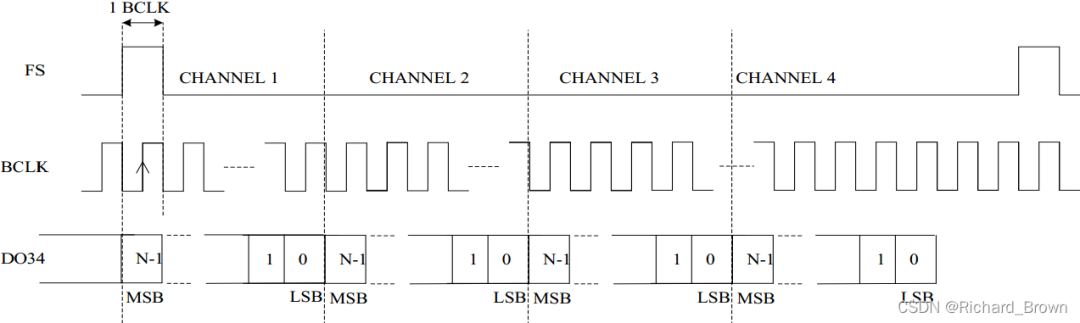

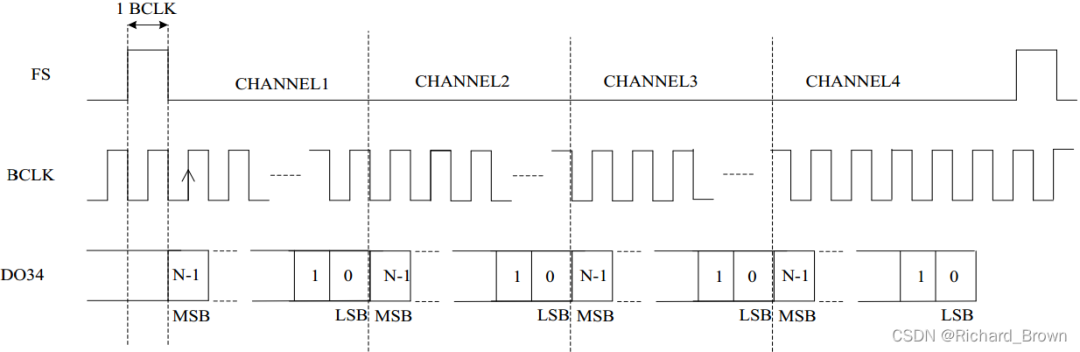

根據(jù) SD相對幀同步時鐘FSYNC的位置,TDM分兩種基本模式:

Mode A: 數(shù)據(jù)在FSYNC有效后,BCLK的第2個上升沿有效

Mode B: 數(shù)據(jù)在FSYNC有效后,BCLK的第1個上升沿有效

注:由于沒有統(tǒng)一標準,不同廠商對Mode A和Mode B定義可能有所差別。

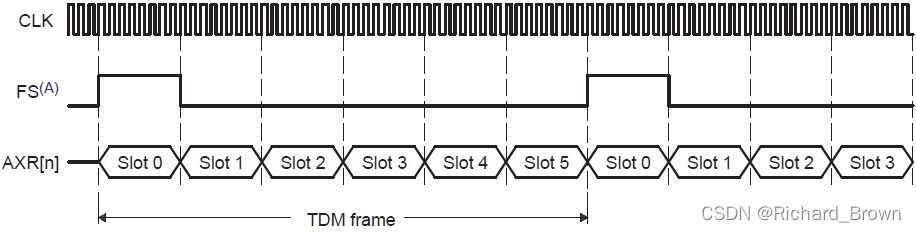

在實際應用中,總是以幀同步時鐘FSYNC的上升沿表示一次傳輸?shù)拈_始。幀同步時鐘的頻率總是等于音頻的采樣率,比如44.1 kHz,48 kHz等。多數(shù)應用只用到FSYNC的上升沿,而忽略其下降沿。根據(jù)不同應用FSYNC脈沖寬度的差別,PCM幀同步時鐘模式大致分為兩種:

長幀同步 Long Frame Sync

短幀同步 Short Frame Sync

注:

a. 長幀同步,如圖所示,F(xiàn)SYNC脈沖寬度等于1個Slot的長度。Slot在TDM中表示的是傳輸單個聲道所占用的位數(shù)。如圖所示TI McASP接口的TDM包括6個Slots,即它最多可包括6聲道數(shù)據(jù)。注意,Slot的位數(shù)并不一定等于音頻的量化深度。比如Slot可能為32 bit,其中包括24 bit有效數(shù)據(jù)位(Audio Word) + 8 bit零填充(Zero Padding)。不同廠商對Slot的叫法可能有所區(qū)別,比如Circus Logic稱之為Channel Block;

b. 短幀同步,F(xiàn)SYNC脈沖寬度等于1個BCLK周期長度;

c. 由于沒有統(tǒng)一標準,不同廠商對FSYNC脈沖寬度及觸發(fā)邊沿的設置可能不同,以器件手冊為準。

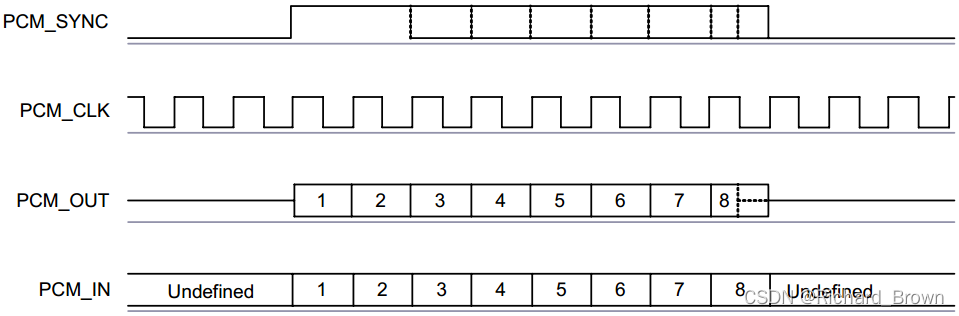

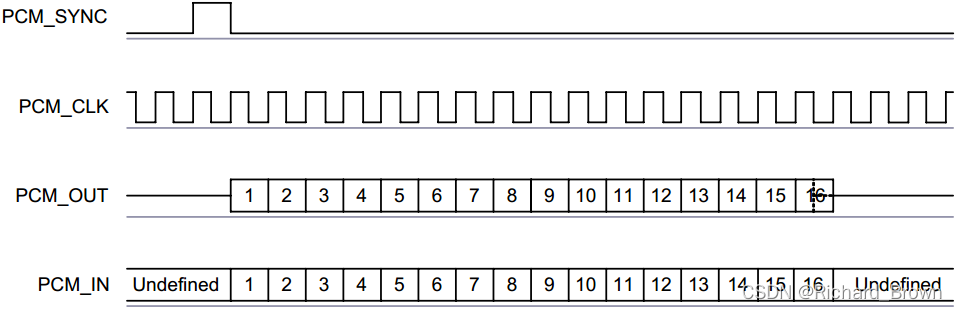

8-bit長幀同步模式

16bit 長幀同步模式

5. 時鐘(BCLK)頻率的計算

FSYNC的頻率等于音頻的采樣率(例如44.1 kHz,48 kHz等)。Frame每次傳輸包括所有聲道的數(shù)據(jù)。PCM采樣音頻數(shù)據(jù)量化深度一般在16-32bit(最常見為16/24bit)。那么對于8聲道,每個聲道32bit音頻數(shù)據(jù),采樣率48kHz的系統(tǒng),TDM的系統(tǒng)時鐘速率為:8 × 32 × 48kHz = 12.288 MHz

BCLK = 采樣率 * 位寬 * 通道數(shù)

FYNC = 采樣率

在器件Datasheet中,可以見到TDM128/TDM256/TDM384/TDM512等說法,數(shù)字的含義為單個TDM數(shù)據(jù)幀包含數(shù)據(jù)的比特數(shù)(即幀長)。TDM128:16bit * 8 channel。TDM256:32bit * 8channel。依次類推。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論