權衡利弊,挑戰和采納

Ashraf Takla, Mixel, Inc., CEO

(2018年4月首次發布。于2022年3月更新。)

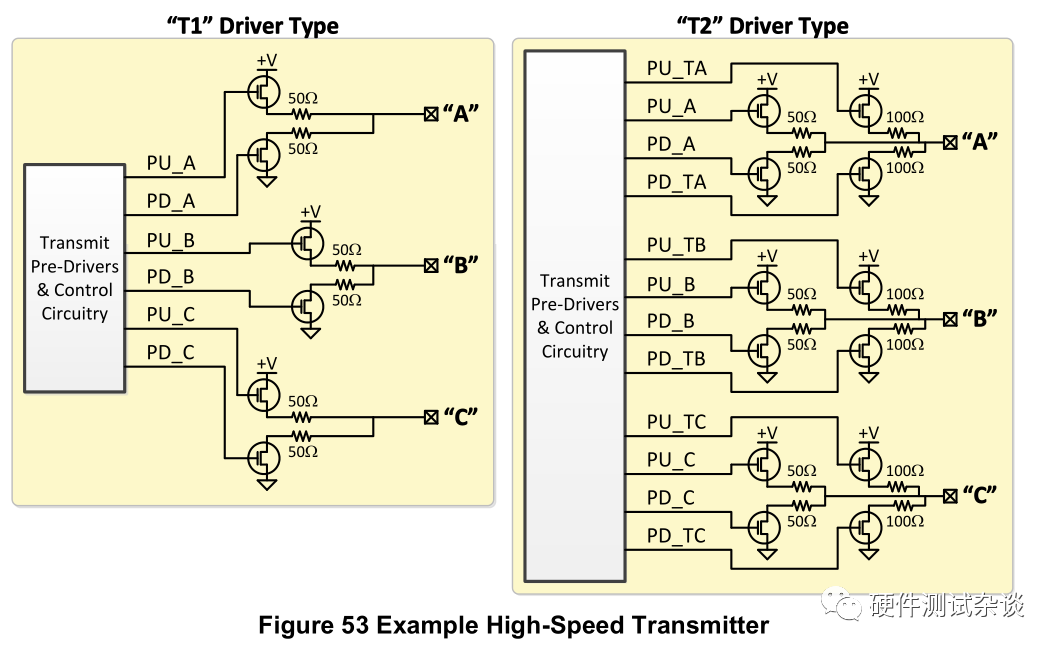

MIPI C-PHYSM于2014年10月面世,讓人既興奮又擔憂。這個新的C-PHY與MIPI D-PHYSM和M-PHY相比如何?C-PHY有什么不同,它是否與D-PHY足夠兼容,以便兩者可以在一個混合子系統中共存?

多年后的今天,答案已經很清楚了。

本文將闡述這些答案,提供D-PHY和C-PHY架構的高層次概述,突出其相似性和差異性,確定每種PHY的優點和缺點,并提供在實施C-PHY時遇到的一些挑戰的見解。最后,我們將研究Mixel對C-PHY/D-PHY組合IP的創新實現,從多個來源獲得的硅結果,涵蓋使用案例,并檢查C-PHY/D-PHY組合解決方案在市場上的采用情況。

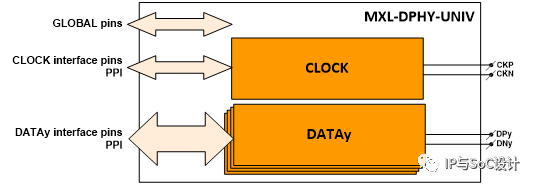

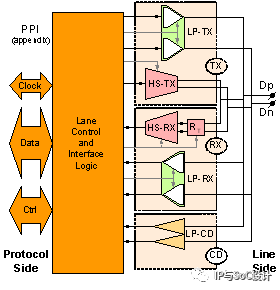

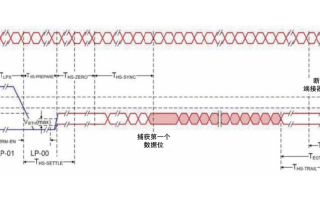

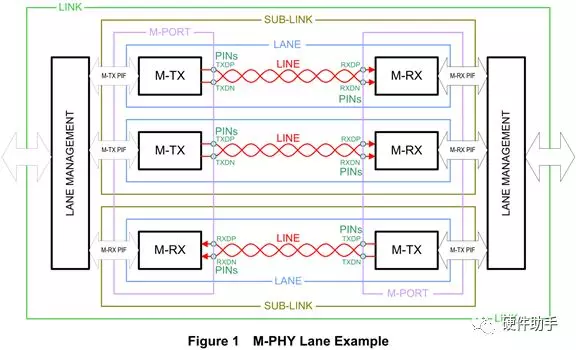

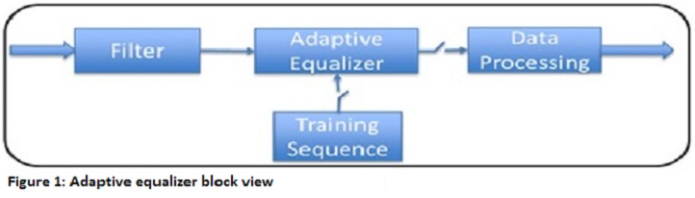

讓我們首先仔細看看D-PHY,它自2009年以來就已經存在,因此得到了更好的理解和廣泛應用。D-PHY是一種簡單的源同步PHY,使用一個時鐘通道和不同數量的數據通道。四個數據通道的D-PHY的框圖如圖1所示,每個通道的細節如圖2所示。由于D-PHY在市場上已經存在了近十年,因此有豐富的文獻涵蓋了它的獨特功能和使用情況(1)。

圖 1:四數據通道 D-PHY 框圖

圖 2:D-PHY 數據通道的框圖

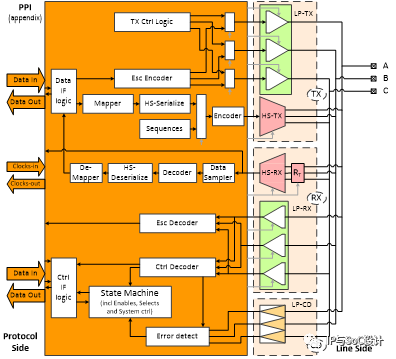

相比之下,C-PHY是一種更新、更復雜的PHY。它在三個信號上運行,三合一,時鐘被嵌入到數據中,從而不需要單獨的時鐘通道。C-PHY的框圖如圖3所示。

圖 3:C-PHY 框圖

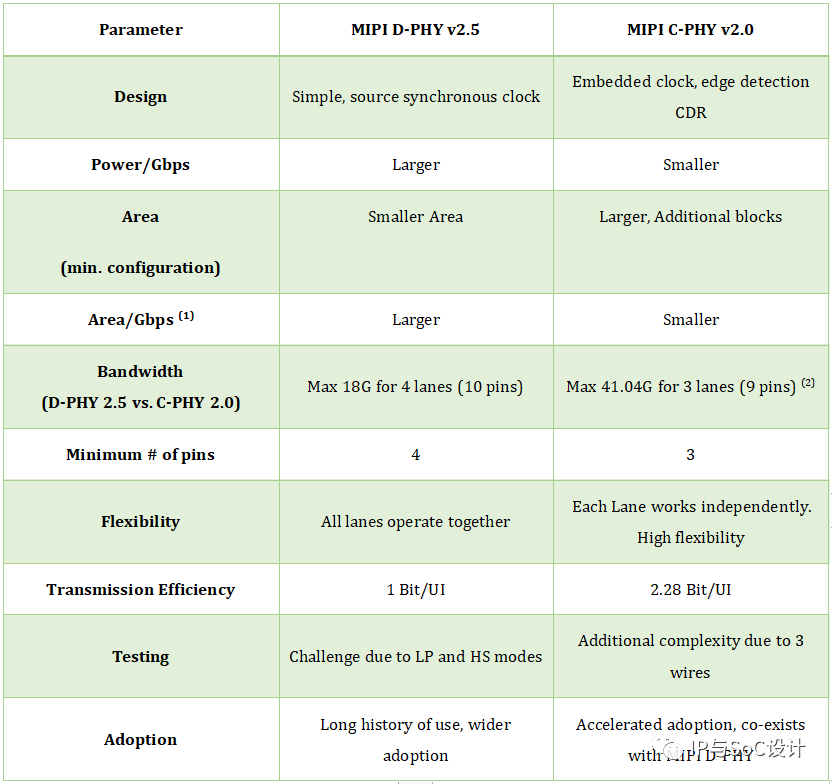

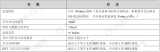

表1對D-PHY和C-PHY進行了比較。

Table 1: C-PHY vs. D-PHY parameters comparison

注釋:

(1) 四個數據D-PHY通道與三個MIPI C-PHY三通道相比

(2) 編碼帶來的更高帶寬

C-PHY使用編碼數據來打包16/7≈2.28位/符號,而D-PHY不使用任何編碼。正因為如此,與D-PHY相比,C-PHY可以實現更高的數據速率,同時以相同的轉換或符號速率運行。??

乍一看,C-PHY的工作原理,以及潛在的C-PHY/D-PHY組合似乎很神秘。C-PHY信令是多級的,但它的接收器不需要檢測多級之間的差異!這是怎么回事?為什么C-PHY和D-PHY有明顯的差異,但它們不僅可以共存,而且可以有效地結合成一個IP?D-PHY使用差分信號,而C-PHY使用三重信號。它們有可能一起工作嗎?如何有效地實現C-PHY/D-PHY的組合,使用所有的D-PHY構建模塊,而沒有任何重復?每個符號的數據位數的比率16/7是怎么來的?有這么多的問題需要思考!

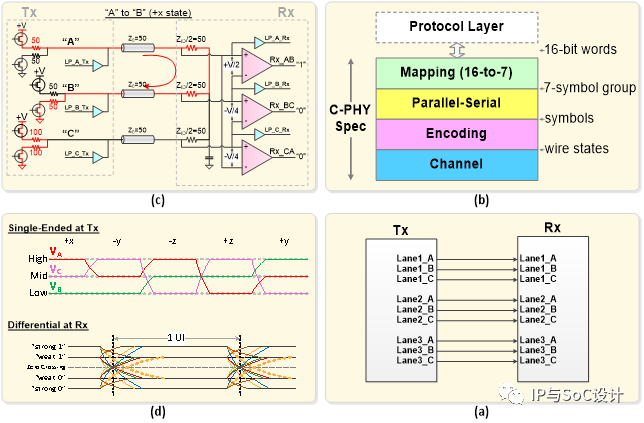

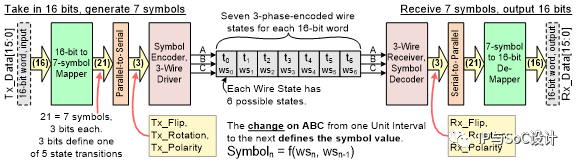

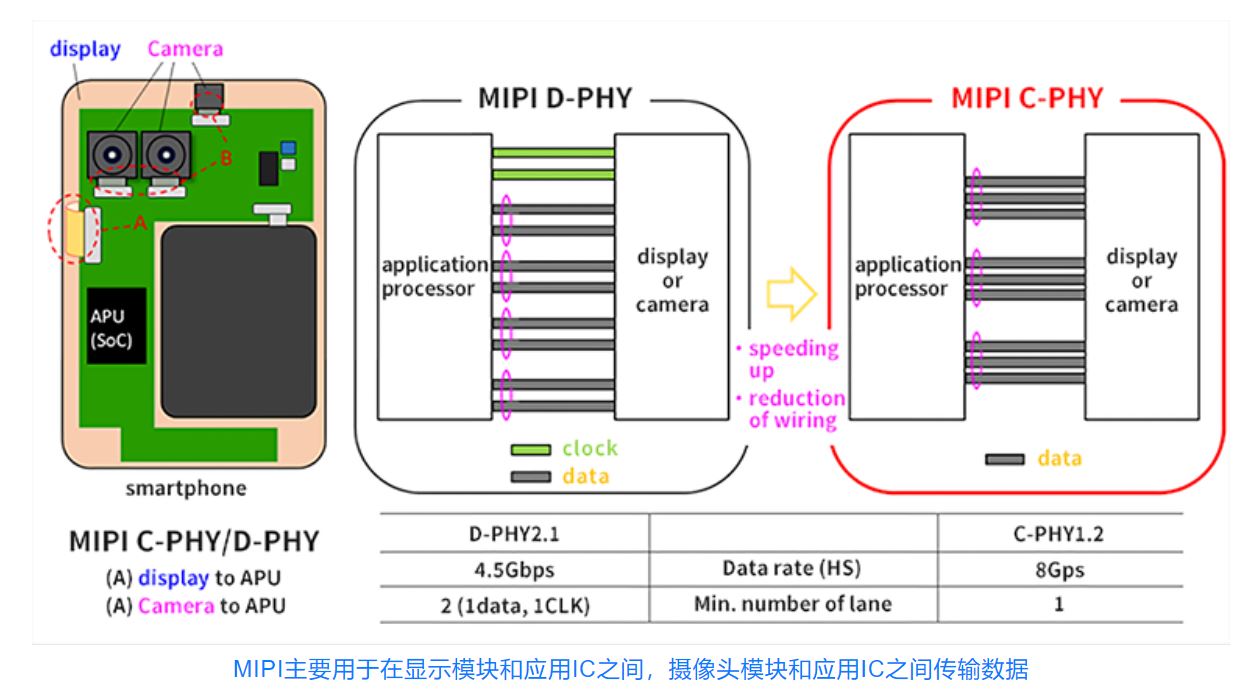

讓我們嘗試著回答這些問題,首先試著揭開C-PHY的神秘面紗。這并不是一件容易的事。在下面的圖4中,我們提供了一個C-PHY的快速概述。圖4(a)中的框圖顯示了一個三通道的C-PHY的TX和RX是如何連接的。圖4(b)顯示了C-PHY子系統的不同子塊,即映射、并行/串行功能、編碼和通道。圖4(c)是TX和RX之間交互的更詳細的圖片,圖4(d)說明了C-PHY的信令級別。?

圖 4:C-PHY (a) TX 和 RX 連接,(b) C-PHY 子系統中的不同功能,(c) 詳細的 TX 和 RX 交互,(d) TX 和 RX 輸出的 C-PHY 信號電平

一個C-PHY車道是由A、B、C三者組成的,如上圖4(c)所示。C-PHY的接收器由3個差分RX組成,每個都是看3個信號中的2個的差分,即(A-B)、(B-C)和(C-A)。

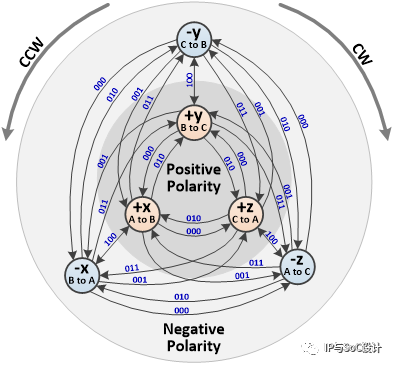

C-PHY的編碼器保證(i)每個符號至少有一個邊緣/轉換,(ii)所有三個RX的差分輸入都是非零,(iii)所有3個信號的共模是恒定的。上述(ii)和(iii)項是通過限制TX信號在任何單一單位間隔(UI)內的組合為高、中、低,以及保持三個信號中每個信號的電壓水平不同來實現的。符合上述限制(i)的三個TX信號水平的組合,即高、中、低,可以得到6個不同的信號水平組合(線態)。線路狀態的數量,6,是三個TX信號電平的排列組合,3! 此外,C-PHY編碼器將翻轉、旋轉、極性符號編碼為基于編碼器規則的狀態變化。

為了保證每個符號至少有一個邊緣,上述第(i)項,C-PHY 在從一個符號移動到下一個符號時必須在不同的線路狀態之間轉換,并且不能在兩個連續的符號中保持相同的線路狀態。由于這一限制,在六個線態之間有五個不同的獨特轉換。這意味著編碼數據有五種不同的可能性,即每個符號有五種可能的狀態,使 C-PHY 成為五進制系統或四進制系統。這樣我們就在二進制系統和四進制系統之間移動。這就是為什么需要C-PHY映射器的原因。現在我們使用的是五進制系統,比特/符號的最大理論數量是log2(5)=2.3219。? 映射器功能的構建是為了使映射率盡可能接近而不超過該理論極限。此外,映射器必須在兩個整數之間進行映射。選擇比率16/7≈2.28是為了實現上述限制。

另一種描述方式是,映射器需要將16個二進制位映射到一定數量的C-PHY符號,但我們如何確定映射到多少個符號(S)?在并行接口上有2^16種組合,映射器輸出端的組合是5^S => 2^16,所以S = 7。?

圖 5:C-PHY 編碼和映射功能概述

要理解為什么C-PHY接收器只需要檢測輸入信號的極性,而不是多振幅信令的振幅,我們只需要記住,信號振幅中沒有嵌入數據。多振幅信令僅用于增加可能的轉換次數,并保證每個符號至少有一個轉換。

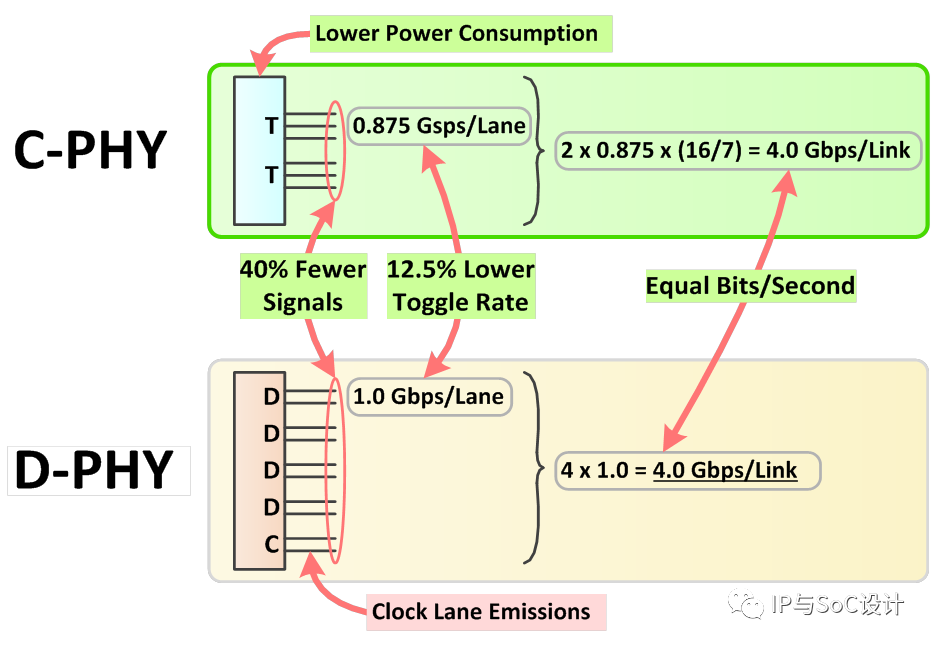

在C-PHY和D-PHY的性能之間做一個相似物比較的方法是,當它們支持4.0Gbps的總數據速率并以類似的轉換速率運行時,對它們進行比較。對于D-PHY來說,這可以通過使用四通道D-PHY來實現,使用10條數據線,每個通道以1.0Gbps/通道運行。為了獲得與C-PHY相同或更低的轉換速率的總數據速率,我們可以使用具有6根線的雙通道C-PHY,以0.875Gsps運行,低于D-PHY的1.0Gsps。在這種情況下,C-PHY的總數據速率是2 * 0.875 * 16/7 = 4Gbps。這種比較顯示在下面的圖6中。

圖 6:支持 4Gbps 聚合數據速率并使用相同轉換速率的 D-PHY 和 C-PHY 之間的比較

基于這種比較,C-PHY有更少的電線(最多減少40%),更低的切換率/通道(降低12.5%),更低的功耗(降低約20-50%),更少的通道數量,因此相同Gbps的面積更小,并且沒有時鐘通道的消耗。?

因此,當比較C-PHY和D-PHY在相同的總數據速率下,C-PHY有很多優勢;更少的引腳和焊球(由于每個引腳的性能更高)、靈活性,因為每個C-PHY通道是獨立的,帶有嵌入式時鐘,可以將一條通道從一條鏈路借用到另一條鏈路,同時與MIPI D-PHY共存于同一引腳上。C-PHY還允許在更高的數據率應用中降低功率。此外,C-PHY的嵌入式時鐘通道可以將應用處理器上的任何通道分配給任何鏈路,并消除了時鐘雜散發射,這在多頻段無線設備中尤為重要。??

C-PHY的嵌入式控制代碼還能夠有效地支持新興的功能,如快速總線周轉(BTA)操作,對時間敏感鏈路的低延遲(LRTE),以及備用低功耗模式(ALP),這將通過消除單端LP模式實現更長的傳輸距離,從而減少面積。最后,C-PHY較低的切換率通常可以簡化制造,降低低成本產品的成本,例如低端相機。?

現在我們已經了解了C-PHY和D-PHY的各個屬性,我們可以列舉出C-PHY和D-PHY組合的一些優勢。這包括能夠共享串行接口引腳,重用LP(低功耗)模式,共享公共塊,從而減少面積,降低功率/Gbps,在MIPI D-PHY和MIPI C-PHY之間平穩過渡,利用MIPI C-PHY的功率/性能/面積(PPA)改進,同時保持與MIPI D-PHY的兼容性。?

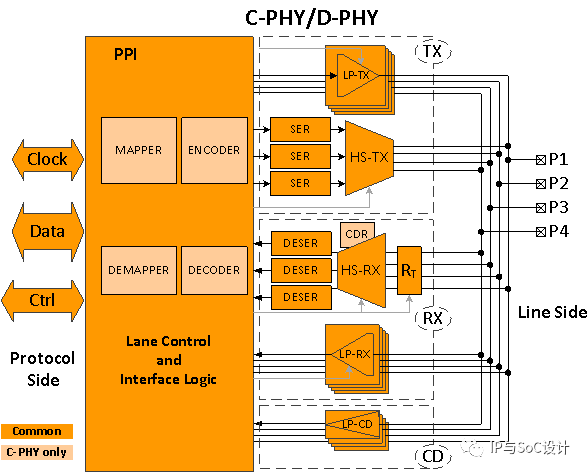

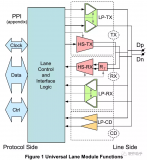

Mixel的C-PHY/D-PHY組合IP的實現是獨一無二的。所有的D-PHY塊都被重新用于C-PHY操作(HS-TX、HS-RX、SER、DESER、LP-TX、LP-RX和LP-CD),使支持C-PHY的面積開銷最小化。雖然所有的塊都被重復使用,但編碼器、解碼器、CDR、映射器和解映射器是C-PHY功能所需的附加模塊。Mixel實現的框圖如圖7所示。

圖 7:C-PHY/D-PHY 組合 IP 框圖

Combo C-PHY/D-PHY已經由Mixel在許多不同的節點和代工廠實現。事實上,Mixel的MIPI IP已經在12個不同的節點和8個不同的代工廠進行了硅驗證。

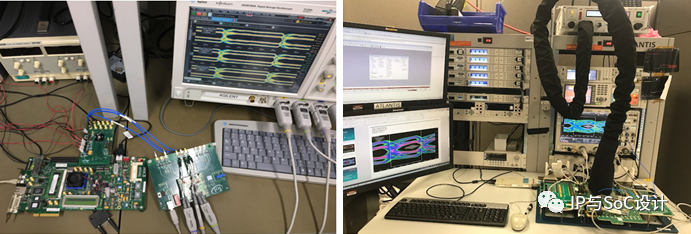

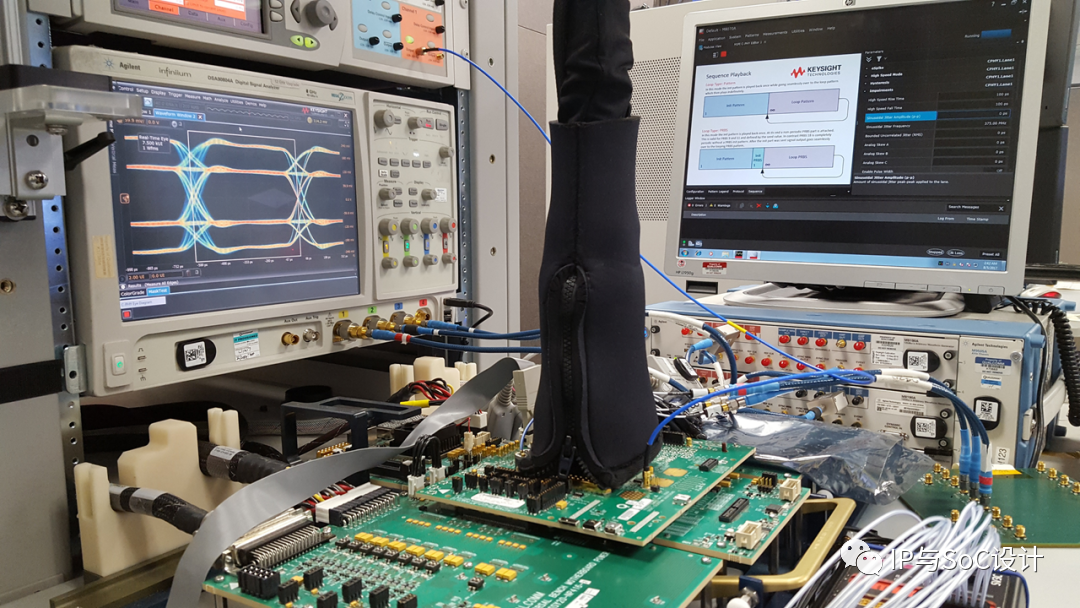

下面我們展示了C-PHY和D-PHY發射器的測試設置和芯片評估。

圖 8:MIPI C-PHY 發射機測試設置

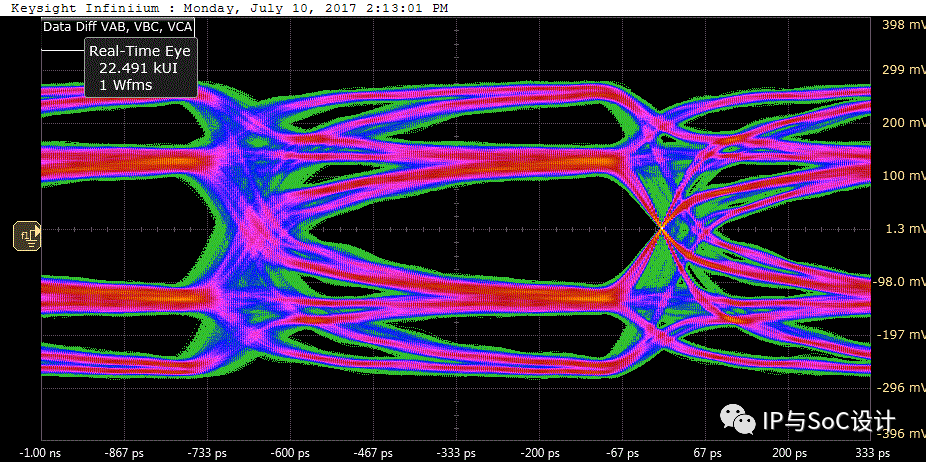

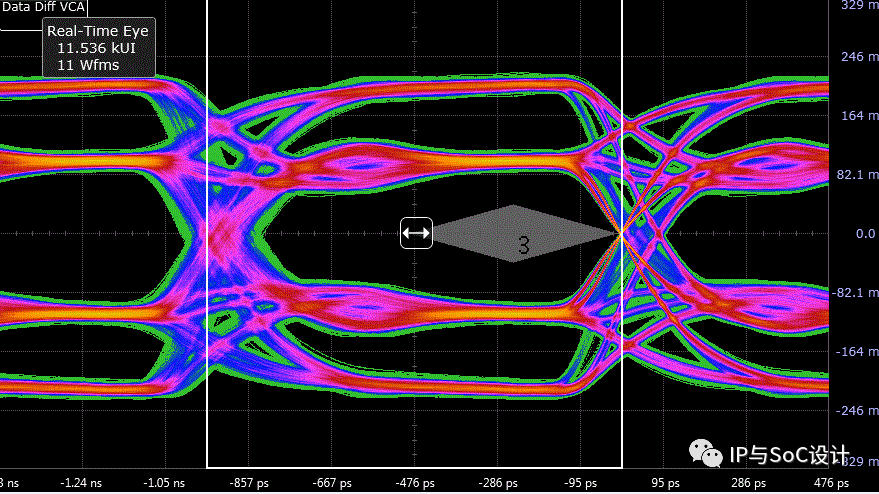

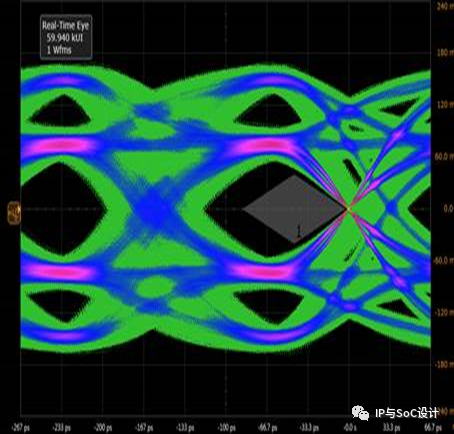

1.5Gsps

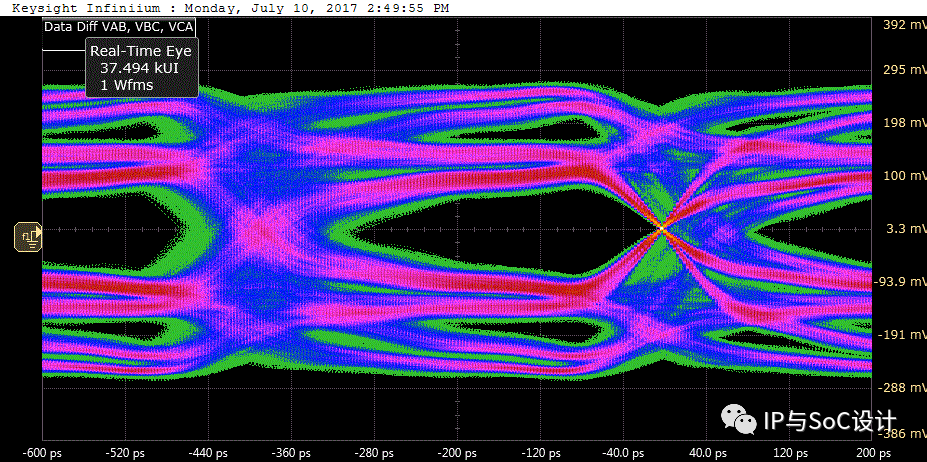

2.5Gsps

圖 9:芯片結果:TX MIPI C-PHY – 眼圖(Mixel)

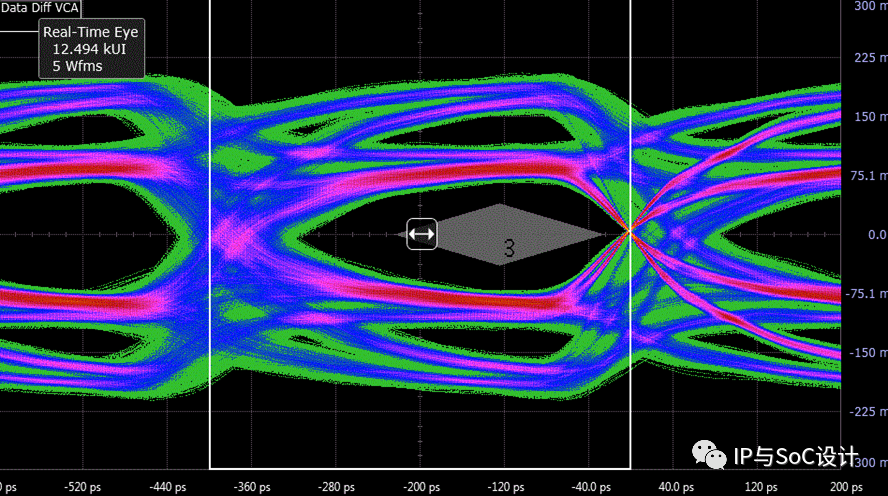

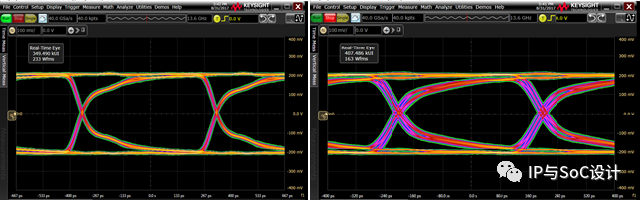

1.05Gsps @ std channel

2.5Gsps @ short channel

2.5Gsps @ std channel?

圖 10:芯片結果:TX MIPI C-PHY – 眼圖(高通)

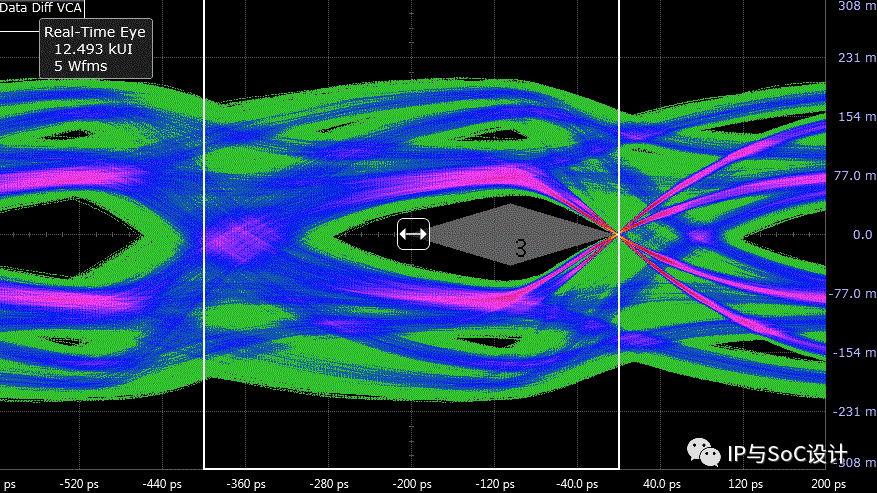

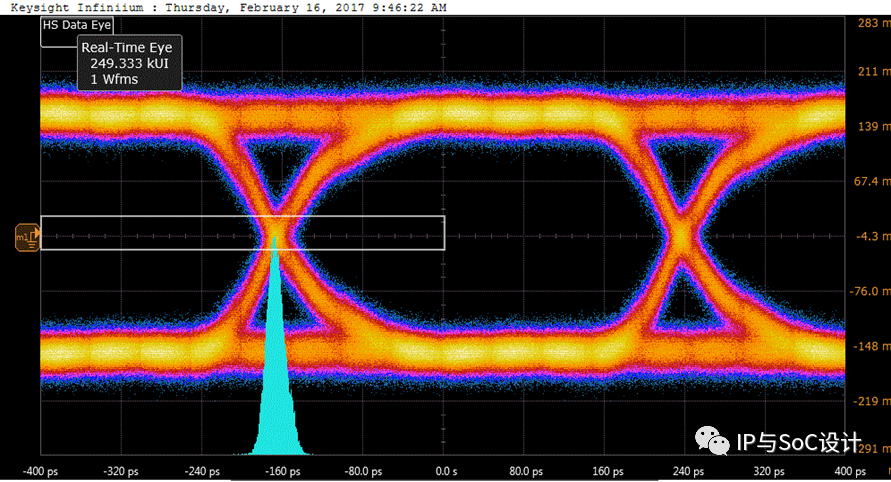

3.5Gsps @ standard channel

6.5Gsps @ short channel?

圖 11:芯片結果:TX MIPI C-PHY – 眼圖(索尼)

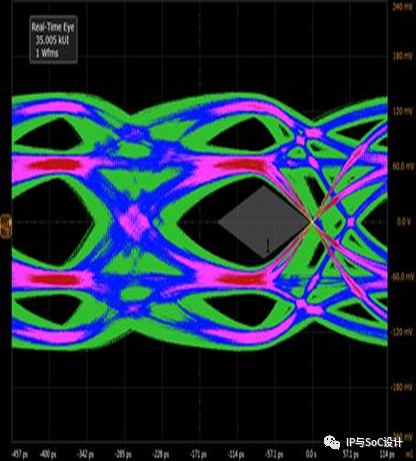

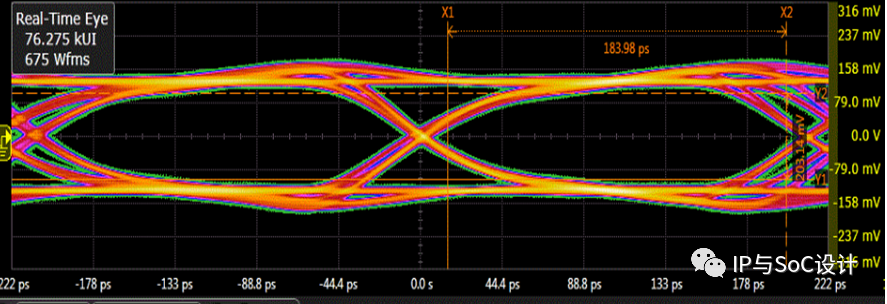

1.5Gbps? ? ? ? ? ? ? ? 2.5Gbps? ? ??

圖 12:芯片結果:TX MIPI D-PHY – 眼圖(Mixel)

2.5Gbps @ short channel

4.5Gbps @ short channel

圖13:芯片結果:TX MIPI D-PHY - 眼圖(高通)

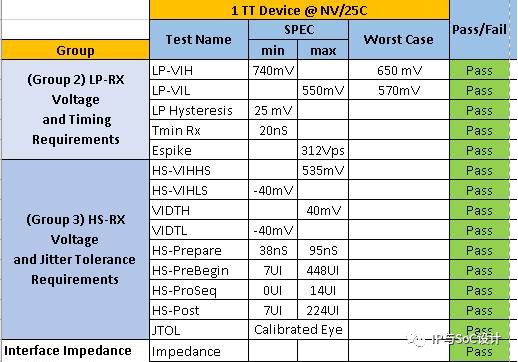

下面我們展示了C-PHY和D-PHY接收器的測試設置和硅評估。

圖14:芯片結果:RX MIPI C-PHY-電氣(高通公司)

圖 15:芯片結果:RX MIPI C-PHY – 鏈路(高通)

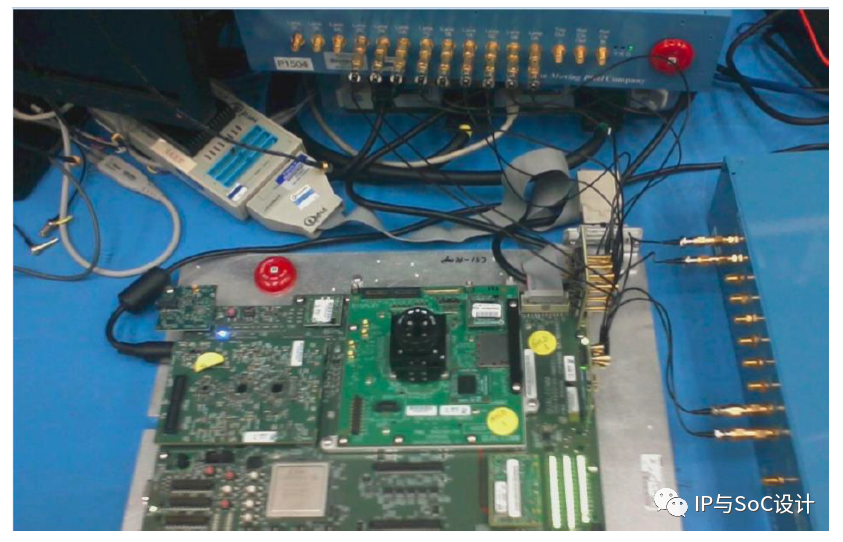

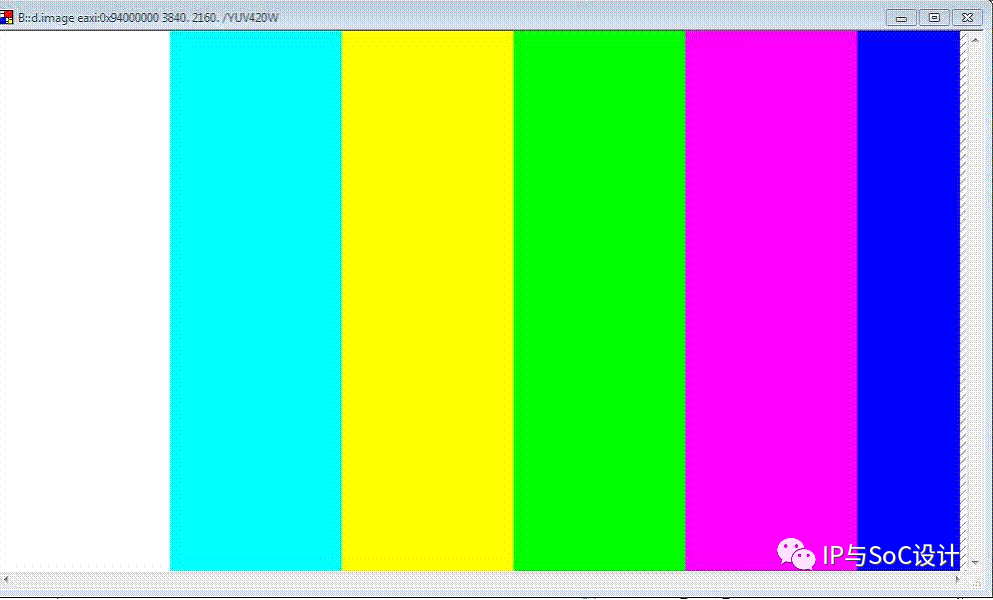

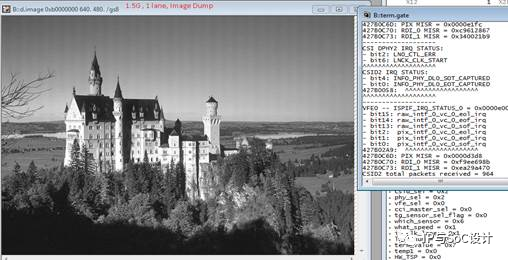

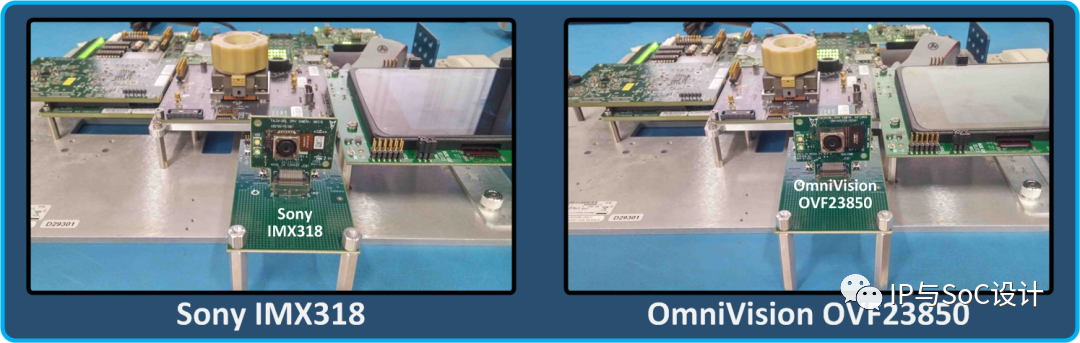

圖 16:示例用例:攝像頭調出

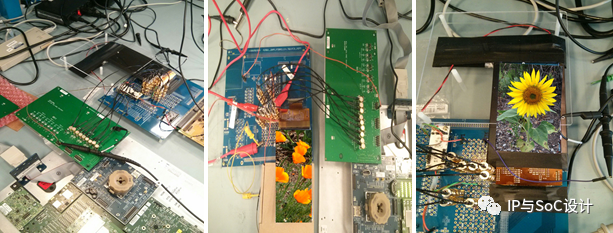

圖 17:示例用例:顯示調出

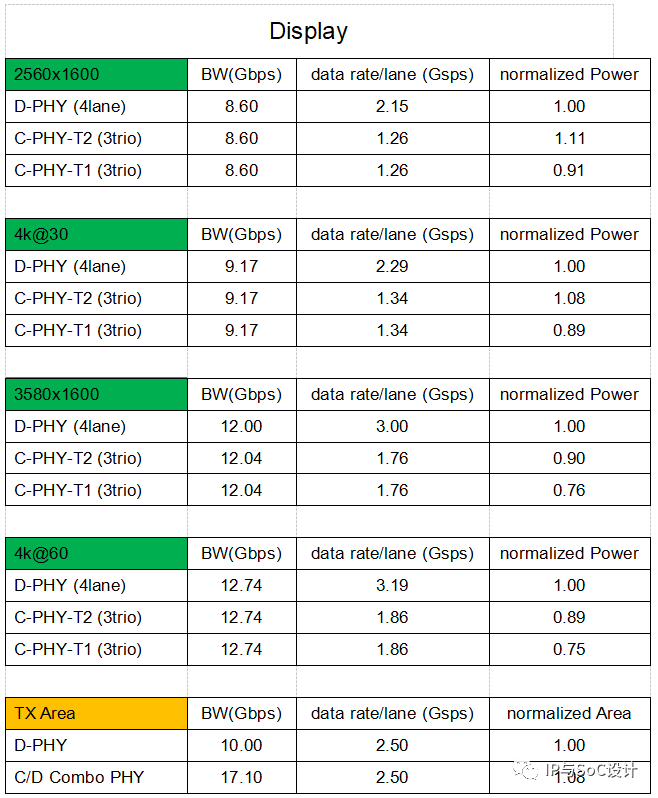

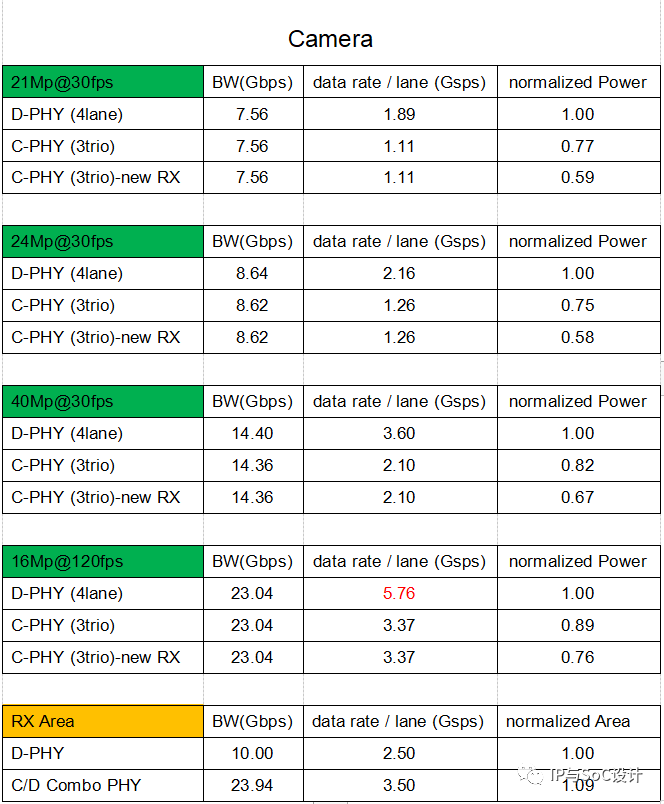

現在,讓我們來看看當前顯示器和照相機應用中不同使用情況的功率、性能和面積。這些都顯示在表3中。?

在相同的數據速率下,比較D-PHY和C-PHY/D-PHY組合時,面積增加很小。僅C-PHY模塊的歸一化功率,當在相同的Gbps下比較時是相當的。在相同的轉換率下,C-PHY比D-PHY有明顯的優勢,可以實現更高的數據速率。

然而,功率增量組合PHY可以通過在C-PHY模式配置中啟用多種設計選項來取消(此處未顯示)。

Table 3: PPA of different use-cases for Display applications

Table 4: PPA of different use-cases for Camera applications

注意事項:

1.Combo PHY面積增量< 10%

2.Combo PHY 可以覆蓋廣泛的分辨率:80Mpbs – 10Gbps – 17.1Gbps – 18Gbps – 23.94Gbps

3.MIPI C-PHY 模式:由于頻率低/偏置較小/通道數較少,功耗比 DPHY 模式低約 10-30%

4.由高通公司提供

C-PHY/D-PHY組合已經在多個使用案例、許多不同的供應商和許多不同類型的產品中得到廣泛采用,包括相機(索尼、OVT和其他)、顯示器(與大多數主要DDIC公司完成互操作性測試)。該生態系統得到了廣泛參與的支持,包括IP(Mixel)、AP/SOC(Snapdragon等)、測試儀(Keysight、Tektronix、Introspect、The Moving Pixel Company)和共模濾波器(Murata、Panasonic、TDK)。?

然而,C-PHY的更高的性能并不是免費的;C-PHY帶來了一些挑戰,包括需要針對不同數據速率范圍進行編程的獨特 CDR、引入編碼抖動的多級信號傳輸以及使 PCB 設計復雜化的獨特的基于 trio 的信號傳輸。

總之,MIPI C-PHY是一個更復雜、更強大、更高效的PHY,而C-PHY/D-PHY組合在各方面更是如此。Mixel 創建并經過硅驗證的雙模 MIPI D-PHY/MIPI C-PHY,實現了兩個 PHY 之間的平滑過渡。Mixel的雙模MIPI D-PHY/MIPI C-PHY共享所有的通用模塊,從而減少了面積,并降低了功率/Gbps。它具有MIPI C-PHY PPA改進的優點,同時保持與MIPI D-PHY的兼容性,并使用相同的串行接口引腳。此外,MIPI C-PHY/MIPI D-PHY組合已經在多個節點和代工廠進行了硅驗證,并且已經被許多一級SOC、傳感器和顯示器供應商集成到幾個終端產品中。自其首次亮相以來,我們看到MIPI C-PHY/MIPI D-PHY組合在各種應用中對攝像頭和顯示器的吸引力不斷增強,包括移動和移動鄰近應用,如VR/AR/MR、汽車、物聯網等。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論