一、概述

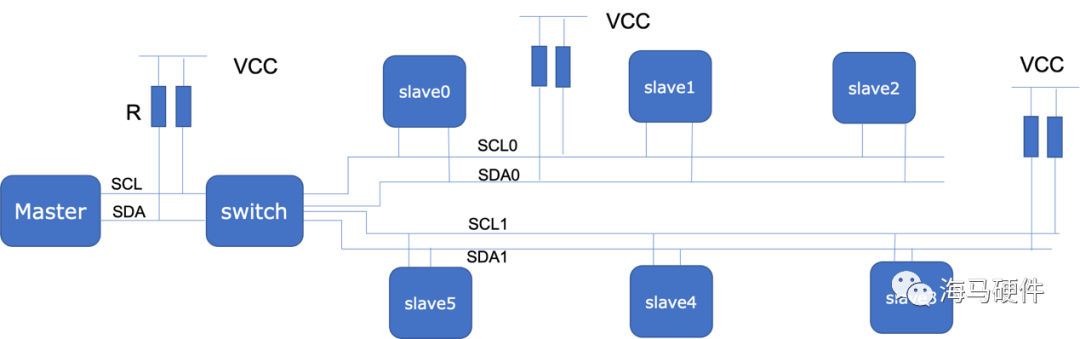

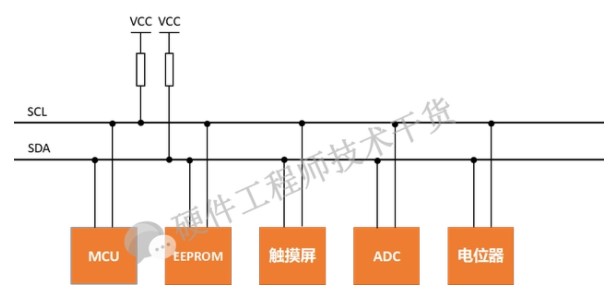

在我們的各種硬件產(chǎn)品中,經(jīng)常會用到IIC總線,IIC是一種兩線接口(Inter-Integrated Circuit)。它是一種串行通信總線,使用多主從架構(gòu),是由飛利浦公司在1980年代初設(shè)計的,方便主板、嵌入式系統(tǒng)或手機(jī)與周邊設(shè)備組件之間的通訊。由于使用簡單,它被廣泛用于微控制器與傳感器陣列、顯示器、EEPROM、IOT等設(shè)備之間的通信。

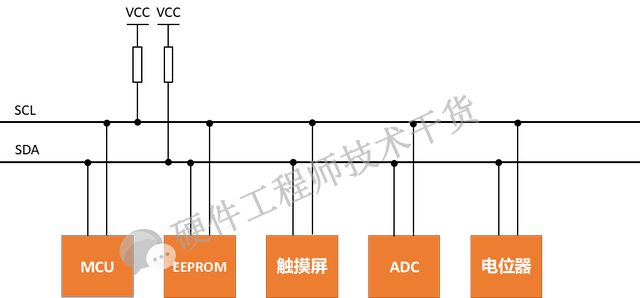

圖1 IIC常用鏈路拓?fù)?/p>

IIC的主要特點(diǎn)如下:

只需要兩條總線,串行數(shù)據(jù)線(SDA),串行時鐘線(SCL);

沒有嚴(yán)格的波特率要求,主設(shè)備生成總線時鐘;

所有組件之間都存在簡單的主/從關(guān)系,連接到總線的每個設(shè)備均可通過唯一地址進(jìn)行軟件尋址;

IIC是多主設(shè)備總線,可提供仲裁和沖突檢測;

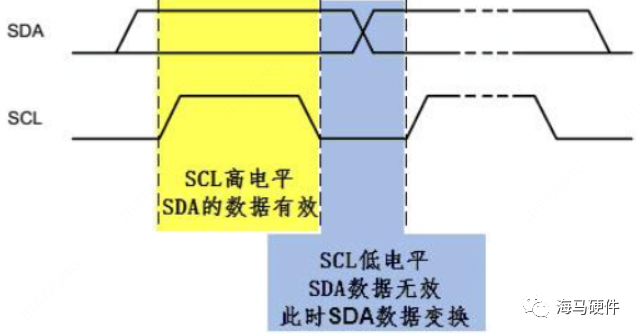

SDA 線上的數(shù)據(jù)必須在時鐘的高電平周期保持穩(wěn)定,數(shù)據(jù)線的高或低電平狀態(tài)只有在 SCL 線的時鐘信號是低電平時才能改變;

常用速率如下:普通模式:100kHz;快速模式:400kHz;高速模式:3.4MHz;

二、物理及協(xié)議層

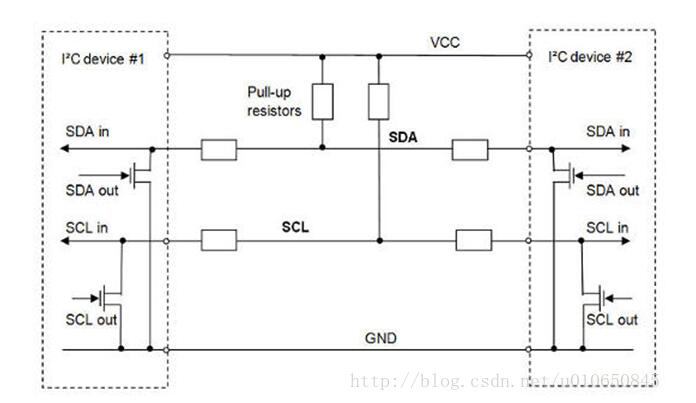

2.1 硬件層

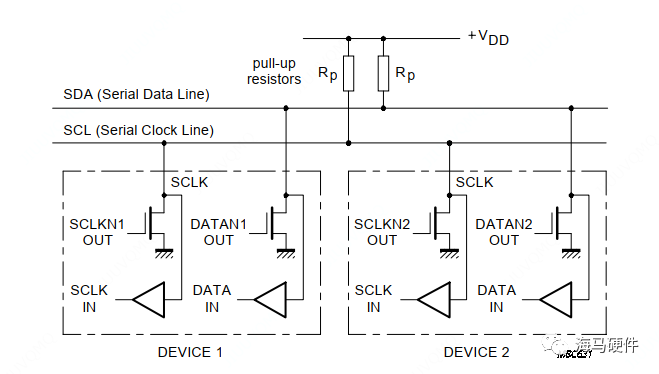

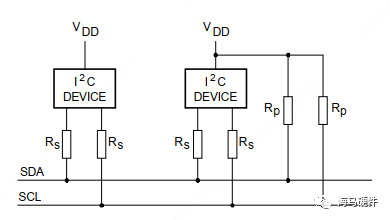

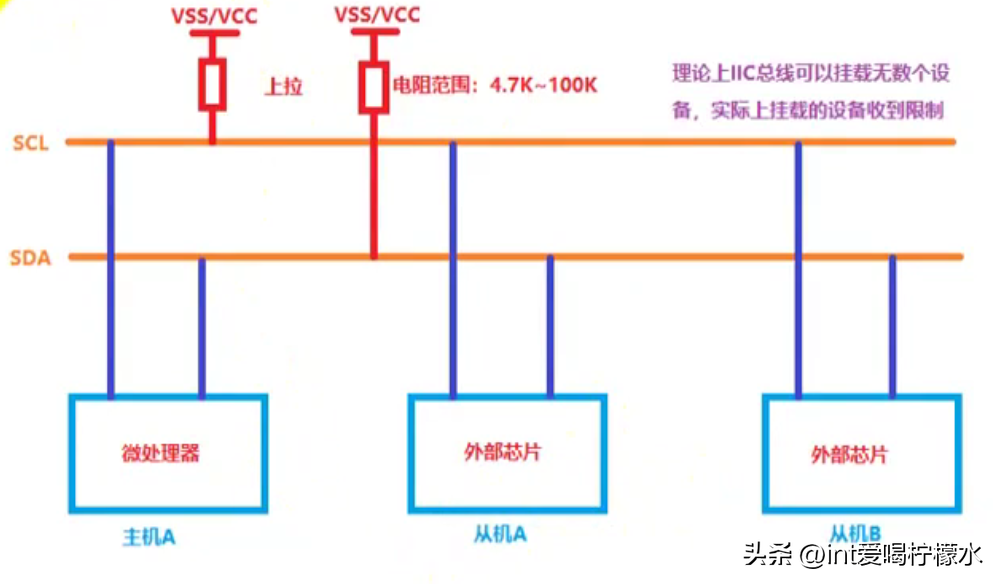

SDA和SCL都是雙向線路,都通過一個電流源或上拉電阻連接到正的電源電壓,連接到總線的接口數(shù)量主要受總電容限制(一般小于400pF),最大從機(jī)數(shù)理論上是127個;

由于SDA、SCL為漏極開路結(jié)構(gòu)(OD),因此它們必須接有上拉電阻,阻值的大小可以是 1k8、 4k7 、10k等,當(dāng)總線空閑時,兩根線均為高電平;

圖2 IIC總線內(nèi)部OD門

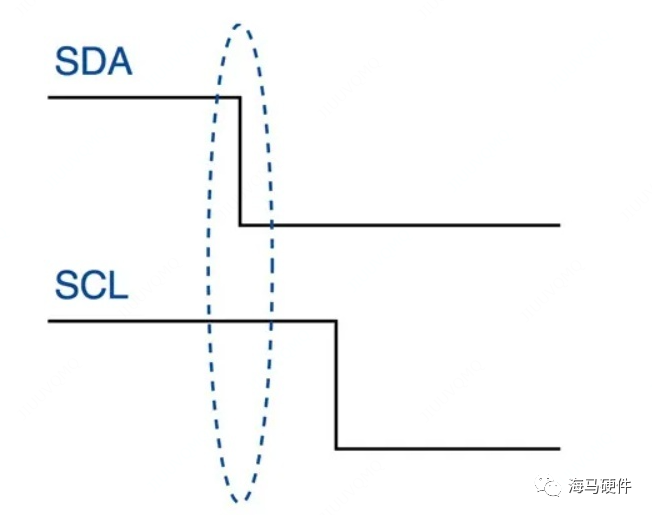

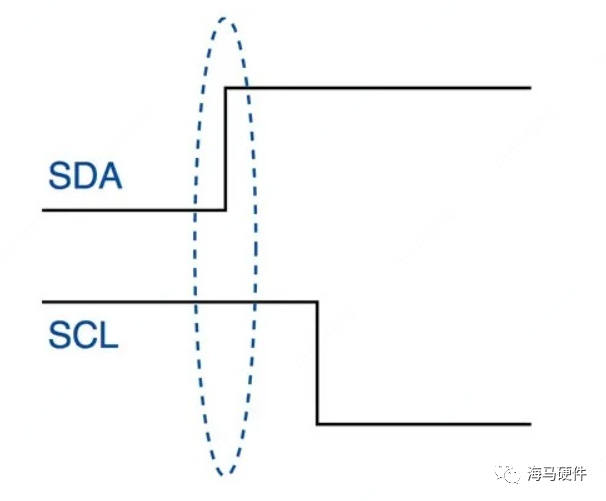

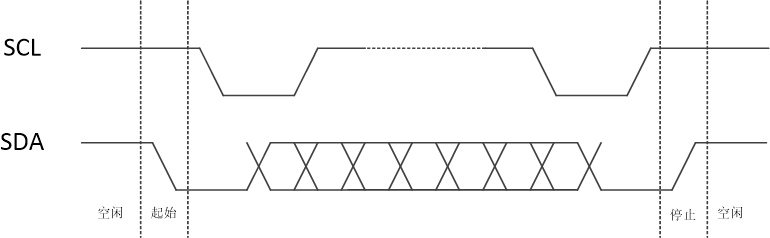

當(dāng)主設(shè)備決定開始或結(jié)束通訊時,需要執(zhí)行以下動作:

當(dāng) SCL 是高電平時

SDA 線由高電平向低電平切換當(dāng) SCL 是高電平時

SDA 線由低電平向高電平切換

通信開始條件通信停止條件

圖3 通信開始/停止條件IIC總線的數(shù)據(jù)有效性

IIC總線既不是上升沿采樣也不是下降沿采樣,而是高電平采樣;IIC 使用 SDA 信號線來傳輸數(shù)據(jù),使用 SCL 信號線進(jìn)行數(shù)據(jù)同步;

SDA在SCL的每個時鐘周期傳輸一位數(shù)據(jù)。SCL為高電平的時候SDA表示的數(shù)據(jù)有效,即此時的 SDA 為高電平時表示數(shù)據(jù)“1”,為低電平時表示數(shù)據(jù)“0”。

當(dāng) SCL為低電平時, SDA 的數(shù)據(jù)無效,一般在這個時候 SDA 進(jìn)行電平切換,為下一次表示數(shù)據(jù)做好準(zhǔn)備。

圖3 數(shù)據(jù)有效性

IIC總線的F/S模式器件的時序定義

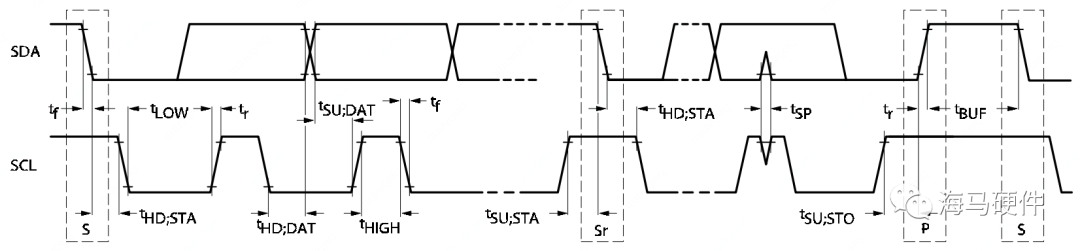

在測試IIC總線的時候時序測試尤為重要,也是IIC信號完整性測試的主要模塊,很多情況下IIC通信問題都是時序不對導(dǎo)致的。IIC總線在快速模式和普通模式下的時序定義如下圖;

圖5 IIC總線在F/S模式時序定義

重復(fù)起始條件的建立時間(tSU;SAT)

起始條件的保持時間(tHD;SAT)

數(shù)據(jù)保持時間(tHD;DAT)

數(shù)據(jù)建立時間(tSU;DAT)

SDA和SCL信號的上升時間(tr)

SDA和SCL信號的下降時間(tf)

停止條件的建立時間(tSU;STO)

停止和啟動條件之間的總線空閑時間(tBUF)

測試信號時序時需要注意具體的波形卡點(diǎn)位置,卡點(diǎn)位置不對情況下會導(dǎo)致測出來的數(shù)據(jù)不是真正的實(shí)際數(shù)據(jù);具體的卡點(diǎn)位置還要參考被測單板所使用的芯片規(guī)格書的要求,根據(jù)具體的datasheet要求來測試卡點(diǎn),一般情況下這三種情況較多:【10%,90%】、【0.8V,2.0V】、【0.3VDD,0.7VDD】;

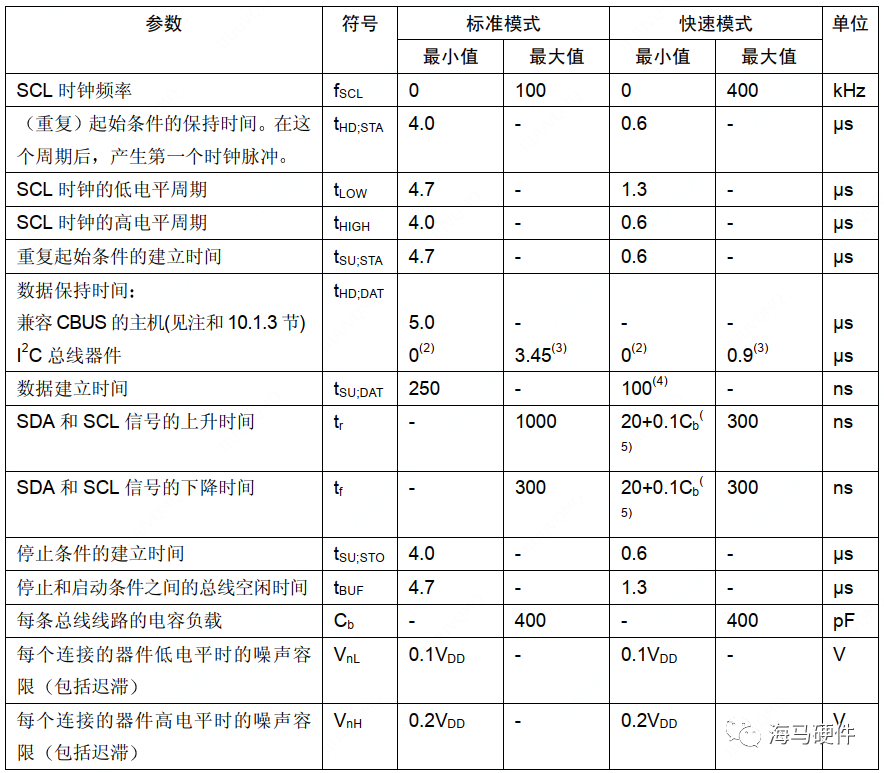

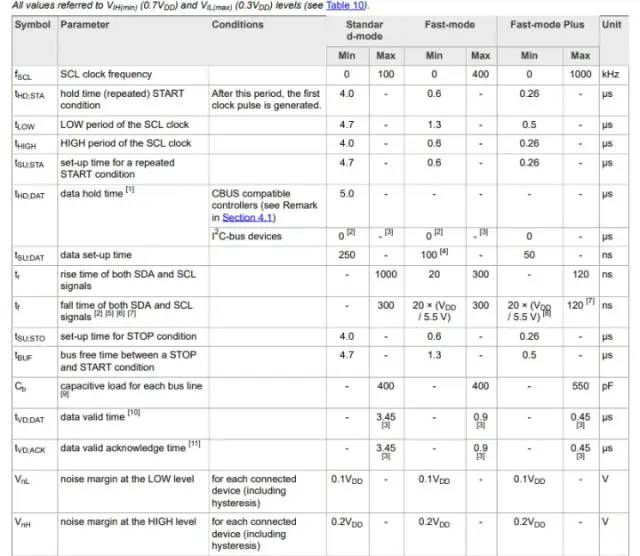

F/S模式IIC總線器件SDA和SCL總線時序標(biāo)準(zhǔn)

在標(biāo)準(zhǔn)模式和快速模式情況下,總線的時序標(biāo)準(zhǔn)是一致的,無論在哪種產(chǎn)品都要以如下標(biāo)準(zhǔn)來判定時序測試的通過與否。

圖6 F/S模式IIC總線器件SDA和SCL總線時序標(biāo)準(zhǔn)

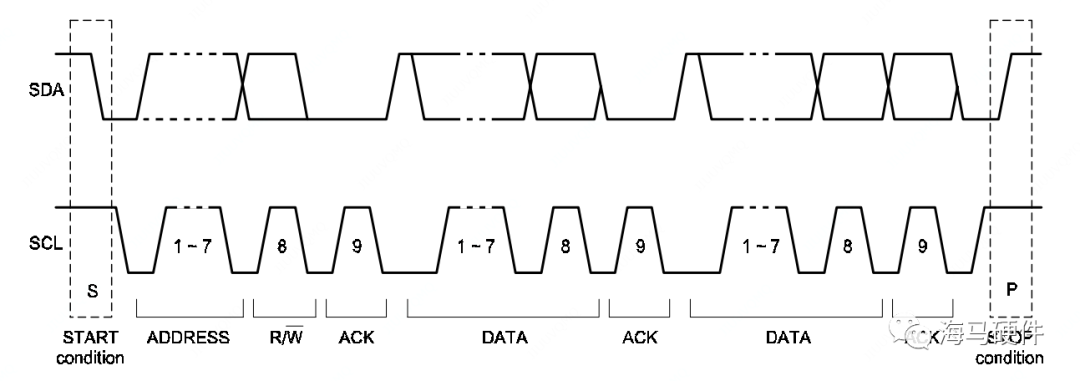

IIC總線的數(shù)據(jù)傳輸格式(7位尋址)

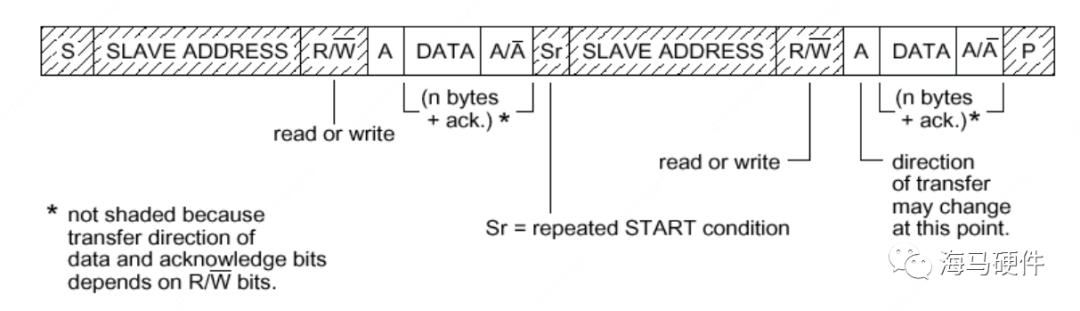

IIC總線尋址方式分為7位尋址和10位尋址,因?yàn)槟壳拔覀冇布a(chǎn)品所用到的都是7位尋址方式,所以介紹一下7位尋址模式的數(shù)據(jù)傳輸格式。

圖7. 7位尋址方式數(shù)據(jù)傳輸格式

如上圖所示:在起始條件 S 后,主機(jī)發(fā)送了一個從機(jī)地址,這個地址共有 7 位;第8位是數(shù)據(jù)方向位 R/ W; 0 表示發(fā)送 (寫), 1 表示請求數(shù)據(jù) (讀);第9位為應(yīng)答位(ACK),應(yīng)答位低電平有效;后面為數(shù)據(jù)傳輸,每一組數(shù)據(jù)對應(yīng)一個應(yīng)答位。

如果主機(jī)仍希望在總線上通訊,可以產(chǎn)生重復(fù)起始條件 Sr(restart)和尋址另一個從機(jī)或寄存器,而不是首先產(chǎn)生一個停止條件,在這種傳輸中,一個數(shù)據(jù)串中可能既包括讀也包括寫的格式。

圖8 帶重復(fù)起始條件的7位尋址方式數(shù)據(jù)傳輸格式

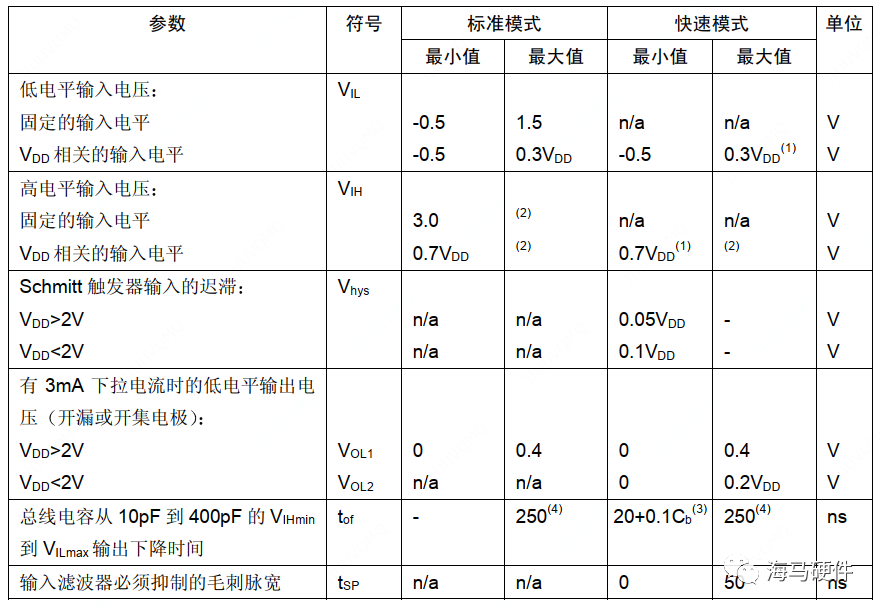

IIC總線器件SDA和SCL的I/O級的特性

1、使用非標(biāo)準(zhǔn)電源電壓(不遵從IIC 總線系統(tǒng)電平規(guī)定)的器件必須將輸入電平連接到有上拉電阻Rp 的 VDD 電壓;

2、 最大的 VIH=VDDmax+0.5V;

圖9 F/S 模式 IIC 總線器件 SDA 和 SCL I/O 級的特性

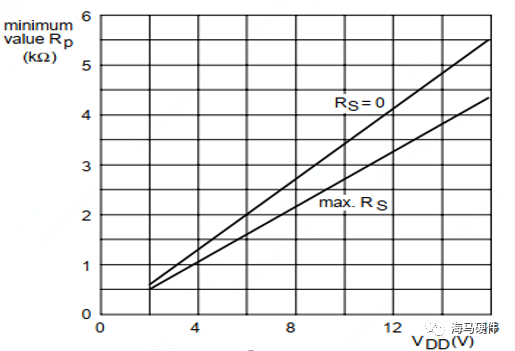

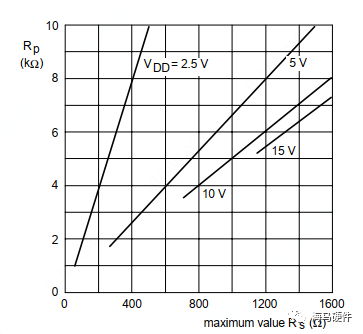

標(biāo)準(zhǔn)模式IIC總線器件電阻Rp和RS的最大和最小值

1. 電源電壓限制了電阻 Rp 的最小值 ,因?yàn)檩敵黾壴?VOLmax=0.4V 時指定的最小下拉電流是 3mA ;

2. 低電平要求的 0.1VDD 噪聲容限限制了 RS 的最大值;

3. 總線規(guī)定的上升時間及電容的存在限制了 Rp 的最大值 ;

Rp:總線的上拉電阻值;

Rs:總線的串阻值;

圖10 IIC上拉和電源供電示意圖

最小上拉電阻vs電壓串阻vs上拉電阻

2.2 IIC總線固件工作過程

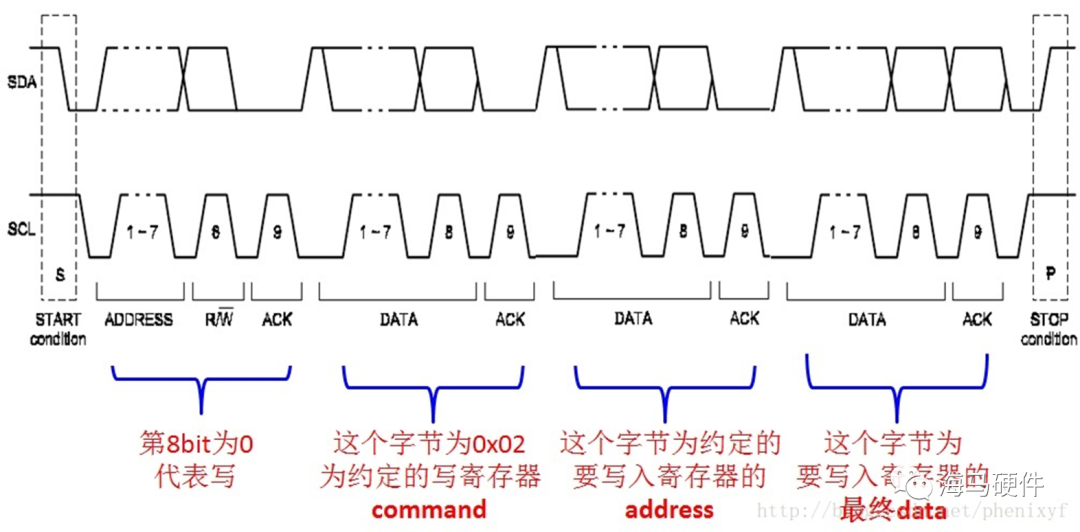

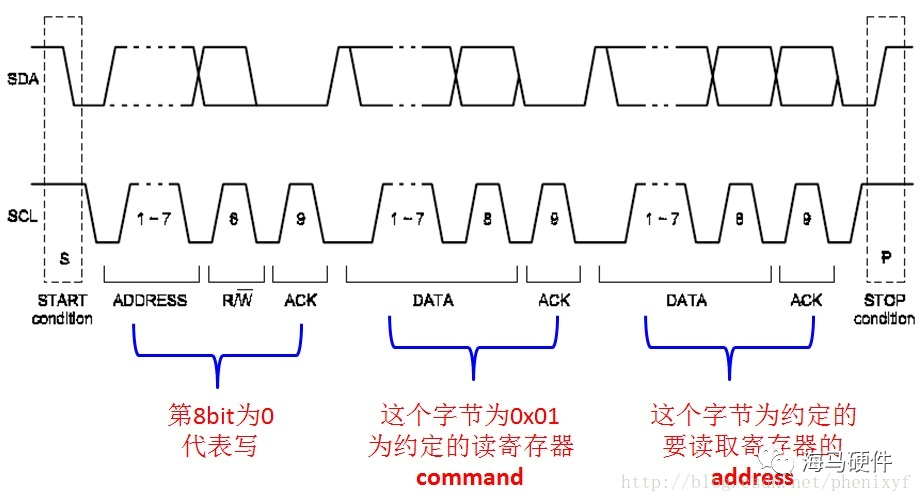

在通信之初,主從機(jī)必須根據(jù)自己的要求約定好通信規(guī)則:command的定義和位置、address的位數(shù)和位置。

以讀寫從機(jī)的寄存器數(shù)據(jù)為例:假設(shè)主機(jī)寄存器地址為8位、從機(jī)寄存器也為8位;約定讀寄存器的command為0x01,寫寄存器command為0x02;約定主機(jī)發(fā)起通信后,第一個slave address字節(jié)收到ack后,緊跟的一個字節(jié)為command,再下面一個字節(jié)為寄存器地址address

寫(主往從設(shè)備寫數(shù)據(jù))

主機(jī):發(fā)起通信,按約定依次寫入command、要寫入的從機(jī)寄存器地址address和要寫入的數(shù)據(jù)data;

從機(jī):分別提取command、address和data,根據(jù)command做出判斷是讀還是寫,將data存入入與到接收的address對應(yīng)的寄存器;

圖13 主設(shè)備往從設(shè)備寫數(shù)據(jù)格式

讀(主設(shè)備讀取從設(shè)備數(shù)據(jù))

主機(jī):先發(fā)起一次通信,將讀command(0x01)和需要讀取的寄存器地址address寫入總線;

從機(jī):分別提取command和address提取;判讀command的定義;根據(jù)收到的address,將對應(yīng)的寄存器數(shù)據(jù)放入從機(jī)的IIC輸出buffer;

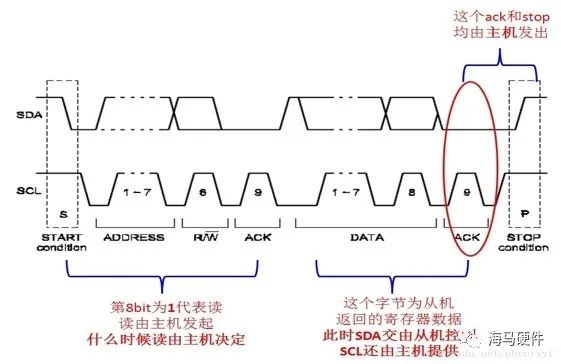

主機(jī):再次發(fā)起一次通信(restart),讀取從機(jī)的數(shù)據(jù);

主設(shè)備讀取從設(shè)備數(shù)據(jù)格式

restart讀取從設(shè)備數(shù)據(jù)格式

三、IIC總線測試分析

幾乎所有的iot產(chǎn)品、it產(chǎn)品、攝像機(jī)、服務(wù)器產(chǎn)品等在單板和整機(jī)通信中都會使用到IIC總線用于信息傳輸,所以對總線的可靠性、穩(wěn)定性的要求也是非常高,測試的把關(guān)需嚴(yán)格要求。

IIC總線測試主要包括主機(jī)對從機(jī)的讀測試和寫測試、總線信號的信號質(zhì)量測試和信號時序測試等。根據(jù)所使用的芯片不同,一般需要查找芯片規(guī)格書的參數(shù),以制定不同的測試用例參數(shù)。

以下是關(guān)于IIC總線測試的一些典型問題。

波形畸變

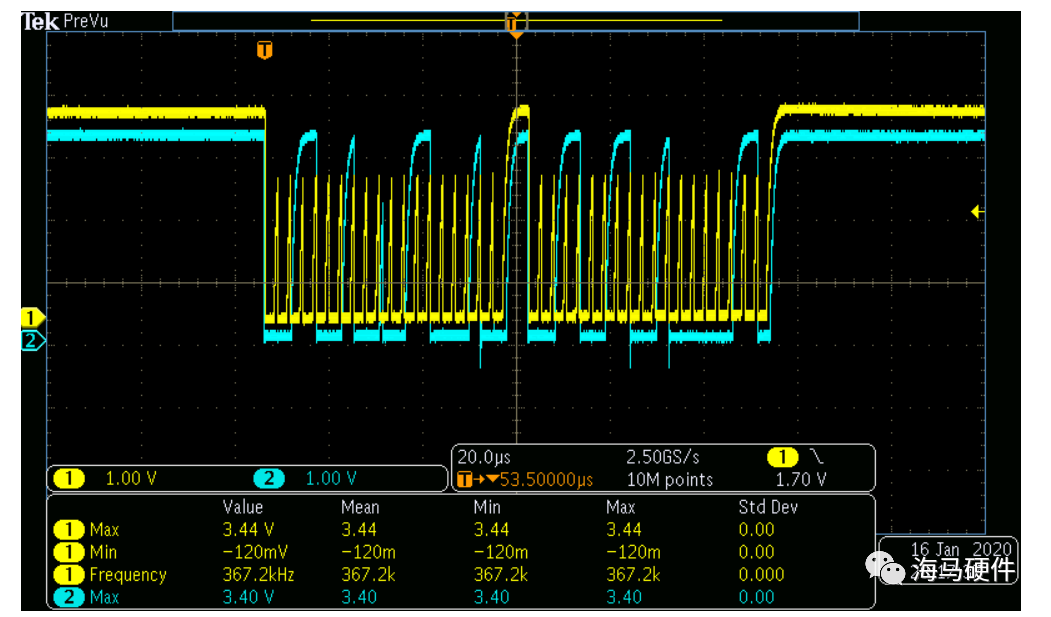

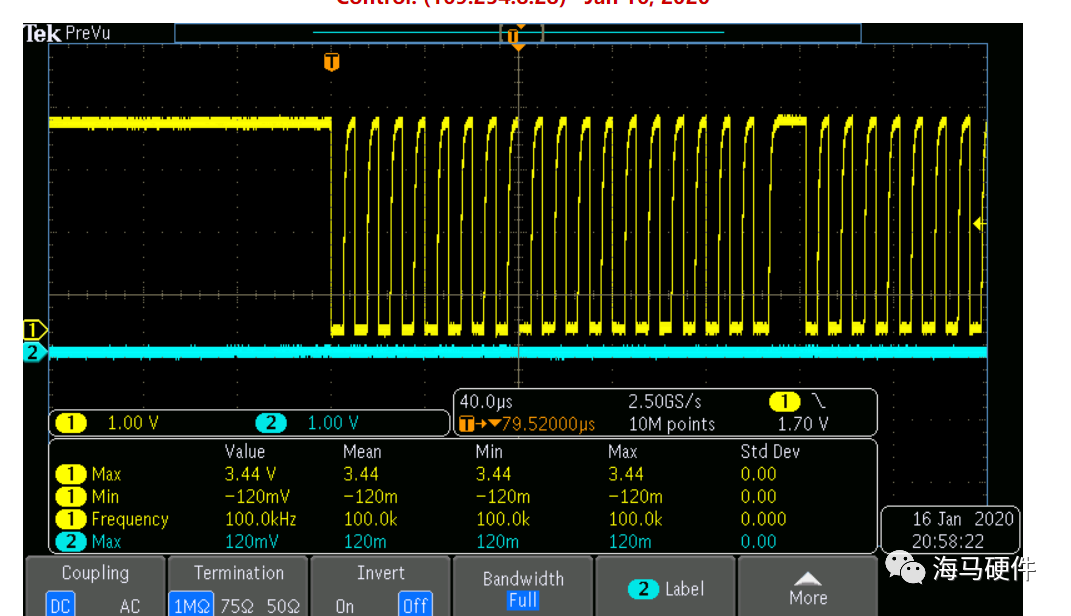

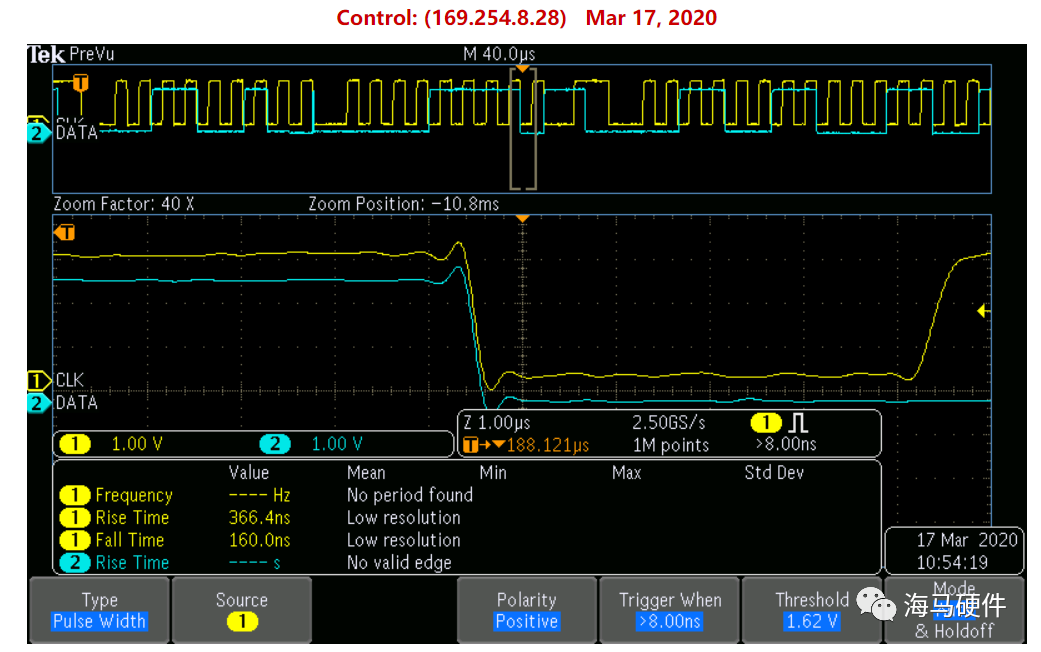

White或Read時發(fā)現(xiàn)時鐘信號畸變,測試時鐘頻率約為367kHz。

測試發(fā)現(xiàn)SCL波形畸變

整改后SCL波形正常

原因分析:固件配置IIC傳輸速率錯誤,沒有按照要求的速率配置,實(shí)際速率與IC和硬件電路的參數(shù)不匹配,導(dǎo)致波形畸變。

時序問題

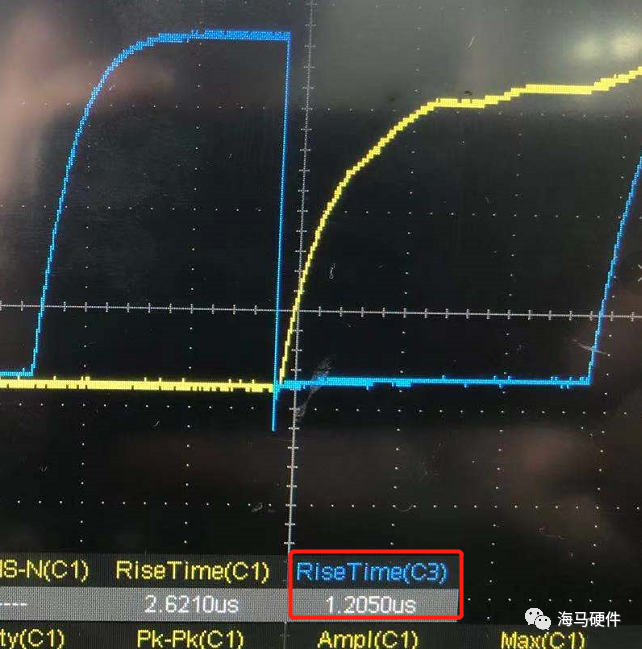

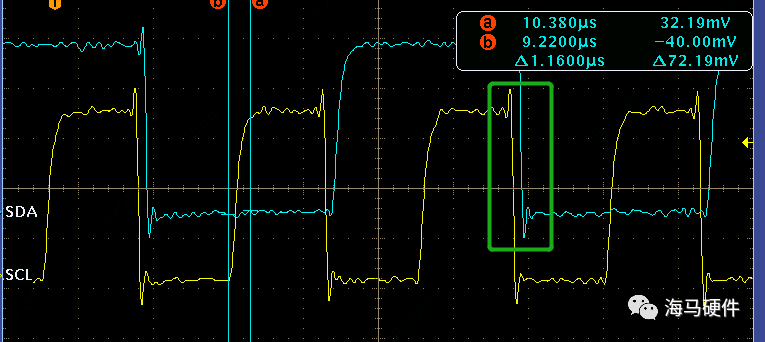

MCU和從機(jī)之間IIC的SCL上升時間為1.2us,指標(biāo)要求1us以下。

SCL的上升時間超標(biāo)

整改后SCL上升時間正常

原因分析:由于此鏈路的IIC總線的上拉電阻選用太大;導(dǎo)致了SCL的上升時間太大(上拉電阻太大還可能導(dǎo)致電平時間低于預(yù)期)。

時序問題

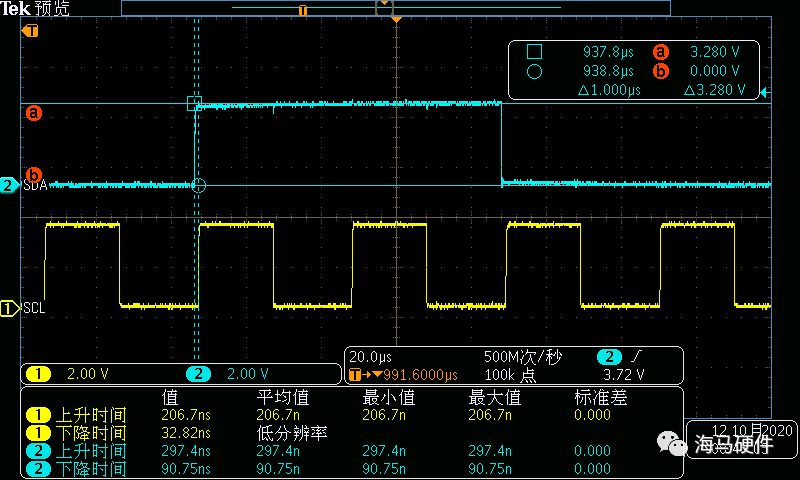

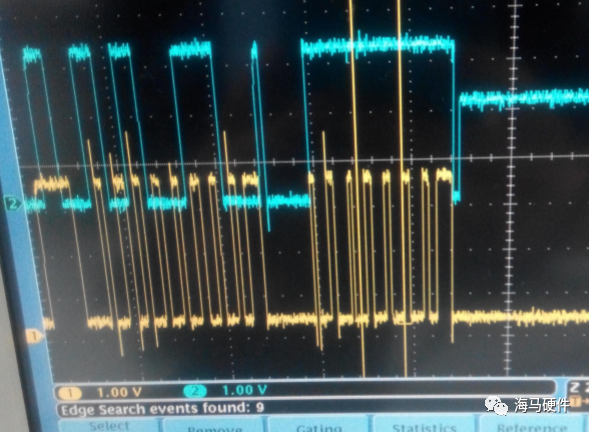

數(shù)據(jù)保持時間不符合要求,數(shù)據(jù)超前時鐘。

時鐘在SDA之外變化

整改后SCL在SDA內(nèi)變化

原因分析:slave芯片部分批次存在固有缺陷,使用舊批次芯片問問題解決。

信號質(zhì)量問題

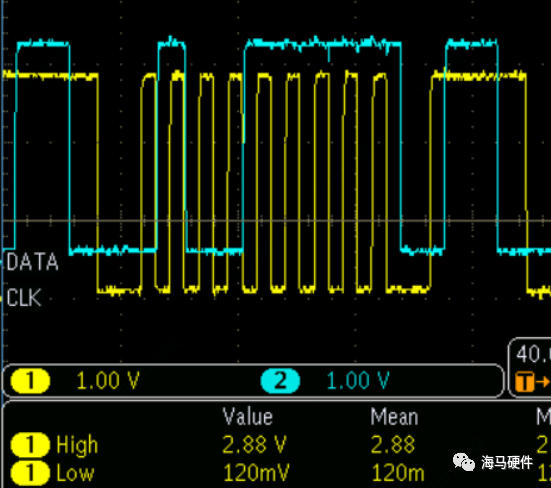

測試發(fā)現(xiàn)IIC總線存在過沖現(xiàn)象,最大電壓能達(dá)到4.1V;超過芯片能承受的最大3.6V和最小-0.3V電壓。

SCL存在過沖現(xiàn)象

整改后SCL在標(biāo)準(zhǔn)內(nèi)

原因分析:接收端信號震蕩導(dǎo)致,存在一定的信號反射導(dǎo)致scl存在尖峰波形超過標(biāo)準(zhǔn)。(注意:探頭接地線太長也會導(dǎo)致類似過沖現(xiàn)象)解決方案:接收端加一個22歐姆的電阻作為阻抗匹配,后效果明顯改善;

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論