2022 年 4?月 14?日,中國北京訊?- 全球半導(dǎo)體解決方案供應(yīng)商瑞薩電子(TSE:6723)今日宣布,率先推出符合PCIe Gen6嚴(yán)格標(biāo)準(zhǔn)的時鐘緩沖器和多路復(fù)用器。作為業(yè)內(nèi)先進的時鐘

2022-04-14 15:33:49 1941

1941

PCIe總線概述 隨著現(xiàn)代處理器技術(shù)的發(fā)展,在互連領(lǐng)域中,使用高速差分總線替代并行總線是大勢所趨。與單端并行信號相比,高速差分信號可以使用更高的時鐘頻率,從而使用更少的信號線,完成之前需要許多

2020-11-21 10:42:13 3562

3562

PCIe 時鐘發(fā)生器的 PI6CG33xxxC 系列產(chǎn)品與 PCIe 時鐘緩沖器的 PI6CB33xxxx 系列產(chǎn)品分別包含八個與九個裝置,提供多樣選擇,例如輸出數(shù)與輸出阻抗。

2020-03-10 11:49:35 964

964 使用自己做的6678的板卡. PCIe參考時鐘100MHz. 運行例程中的PCIe測試.pcie_phy_loopback. 當(dāng)運行完 gpPCIE_app_regs->CMD_STATUS

2019-01-03 11:36:50

_int_cfg.number_tx_MSI = PCIE_16_MSI;這個結(jié)構(gòu)體里面配置了MSI16這個中斷向量。然后工程跑的是loopback模式。調(diào)用了這個語句KeyStone_PCIE

2018-06-21 03:49:49

1.PCIE的發(fā)送和接收數(shù)據(jù)本工程的目的是在XC7K325tffg的平臺上實現(xiàn)pcie的數(shù)據(jù)發(fā)送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的結(jié)構(gòu):架構(gòu)各個模塊的作用PCIE部分

2019-12-26 10:46:09

1 PCIE基本概念1.1 PCIE拓撲架構(gòu)圖1.2 PCIE Switch內(nèi)部結(jié)構(gòu)圖1.3 PCIE協(xié)議結(jié)構(gòu)圖2 PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓撲示例

2022-02-16 06:08:26

我想用C6657的PCIE接口擴展一個WIFI.

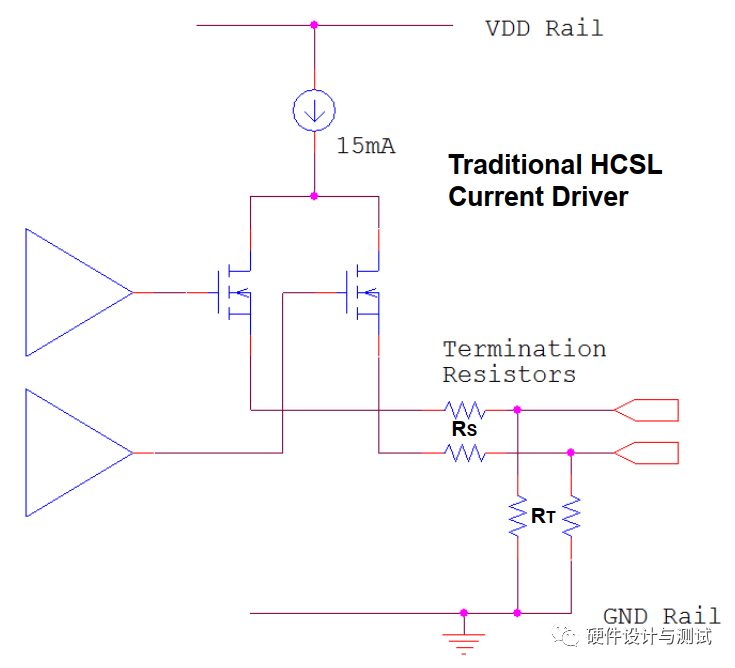

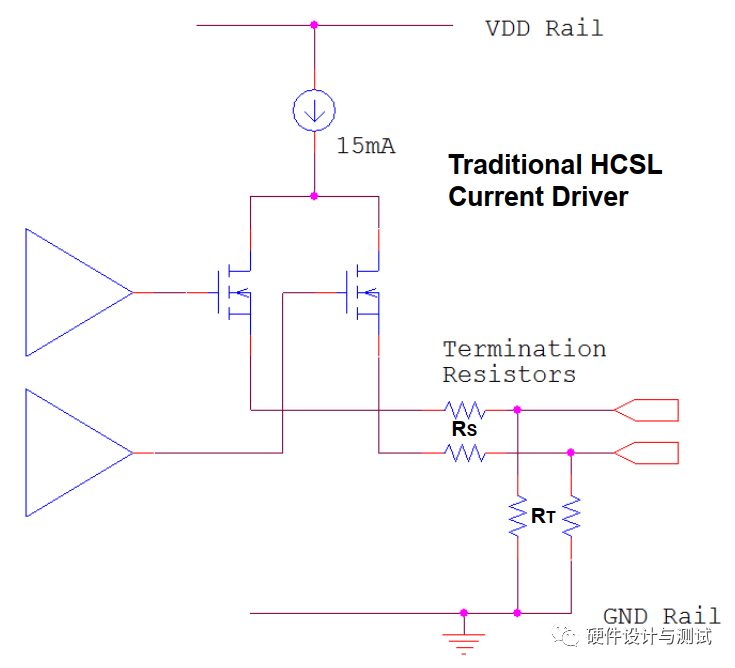

C6657的PCIE需要一個LVDS的參考時鐘(PCIECLKP, PCIECLKN),? WIFI芯片的PCIE需要一個HCSL的參考時鐘

2018-06-21 18:45:06

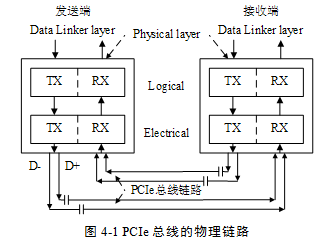

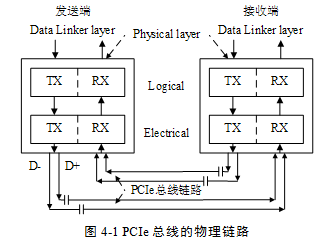

PCIe提供了一種可裁減高速串行I/O點到點的總線連接。PCIe的LAN是一個全雙工的通道,由一對接收差分對和一對發(fā)送差分對構(gòu)成。PCIe的帶寬可以通過增減LANE數(shù)來調(diào)整。PCIe規(guī)范定義了x1

2019-06-03 07:09:56

”,簡寫PCIe。2、AC耦合電容:高速差分信號電氣規(guī)范要求PCIe發(fā)送端串聯(lián)一個電容,進行耦合。3、鏈路類型與差分信號數(shù)量:X1:1對時鐘差分信號,1對收發(fā)差分信號,單面pin數(shù)18pi...

2021-11-11 08:05:11

PCIe總線概述隨著現(xiàn)代處理器技術(shù)的發(fā)展,在互連領(lǐng)域中,使用高速差分總線替代并行總線是大勢所趨。與單端并行信號相比,高速差分信號可以使用更高的時鐘頻率,從而使用更少的信號線,完成之前需要許多單端并行數(shù)據(jù)信號才能達到的總線帶寬。PCI總線使用并行總線結(jié)構(gòu),在同一條總線上的所有外...

2021-07-29 07:07:06

串行外設(shè)接口 (SPI) 是微控制器和外圍 IC(如傳感器、ADC、DAC、 移位寄存器、SRAM等)之間使用最廣泛的接口之一。SPI 是一種同步、全雙工、主從式接口。來自主機或從機的數(shù)據(jù)在時鐘上升

2018-10-25 16:32:48

剛?cè)隨TM32 用了也有一段時間了,先做了中斷,CAN,SPI。都是跟著網(wǎng)上的例子直接粘貼外設(shè)的初始化代碼,看的大概能懂,但是時鐘一直迷迷糊糊,不清不楚。 STM32為了實現(xiàn)低功耗,而設(shè)計的功能完善

2021-08-11 07:15:27

一文讀懂DS18B20溫度傳感器及編程對于新手而言,DS18B20基本概念僅做了解,最重要的是利用單片機對DS18B20進行編程,讀取溫度信息,并把讀取到的溫度信息利用數(shù)碼管,LCD1602或者上位

2021-07-06 07:10:47

RTC是什么?RTC芯片有哪些應(yīng)用?RTC芯片的硬件結(jié)構(gòu)是由哪些部分組成的?RTC實時時鐘的作用是什么?

2021-08-24 07:39:34

一文讀懂中斷方式和輪詢操作有什么區(qū)別嗎?

2021-12-10 06:00:50

掌握每種電路結(jié)構(gòu)的工作原理與基本特性。一、20種開關(guān)電源拓撲對比常見的基本拓撲結(jié)構(gòu):■ Buck 降壓■ Boost 升壓■ Buck-Boost 降壓-升壓■ flyback 反激■ Forward 正激

2022-04-07 10:56:48

一文讀懂什么是NEC協(xié)議?

2021-10-15 09:22:14

一文讀懂傳感器傳感器在原理與結(jié)構(gòu)上千差萬別,如何根據(jù)具體的測量目的、測量對象以及測量環(huán)境合理地選用傳感器,是在進行某個量的測量時首先要解決的問題。當(dāng)傳感器確定之后,與之相配套的測量方法和測量設(shè)備也就

2022-01-13 07:08:26

一文讀懂如何去優(yōu)化AC耦合電容?

2021-06-08 07:04:12

一文讀懂接口模塊的組合應(yīng)用有哪些?

2021-05-17 07:15:49

`電感器是能夠把電能轉(zhuǎn)化為磁能而存儲起來的元件。電感器的結(jié)構(gòu)類似于變壓器,但只有一個繞組。電感器具有一定的電感,它只阻礙電流的變化。如果電感器在沒有電流通過的狀態(tài)下,電路接通時它將試圖阻礙電流流過它

2018-09-20 11:34:20

要了解它們的主要參數(shù)。一般情況下,對電阻器應(yīng)考慮其標(biāo)稱阻值、允許偏差和標(biāo)稱功率;對電容器則需了解其標(biāo)稱容量、允許偏差和耐壓。一文讀懂電阻和電容的不同 電阻器和電容器的標(biāo)稱值和允許偏差一般都標(biāo)在電阻體

2017-11-14 10:25:25

SI53159-EVB,用于PoE無線接入點的100至210MHz時鐘發(fā)生器評估板。 Si53159是一款九端口PCIe時鐘緩沖器,符合PCIe Gen1,Gen2和Gen3標(biāo)準(zhǔn)

2020-08-27 12:20:38

一篇讀懂無線充電技術(shù)(附方...

2021-09-14 06:00:53

本帖最后由 人間煙火123 于 2018-6-15 09:30 編輯

如題,PCIe Spec是允許EP使用自己的時鐘的,不知道8168 可否?不然,就必須要改動硬件。

2018-06-15 07:41:57

查過mini pcie的信號引腳定義,有52個信號(大多引腳無用),X1 LANE 的情況,查看飛思卡爾或INTEL處理器的設(shè)計資料,關(guān)于這個應(yīng)用除了主要 的差分收、發(fā)和差分時鐘信號之外還需要額外

2017-11-29 11:50:51

嗨,在ML605設(shè)計中,信號“PCIE_250M_MGT1_P / N”從器件“ICS874001”驅(qū)動到PCIe MGT參考時鐘。根據(jù)以下鏈接中給出的相位噪聲值,http

2020-06-08 15:30:33

我正在使用 i.MX8M Plus。使用 pcie 時,外部時鐘參考運行良好。但是當(dāng)涉及到內(nèi)部時鐘參考時,它變得很奇怪。root@tek3-imx8mp:~# dmesg |grep -E

2023-03-22 06:59:51

你好

作為我們在 ls1028 上努力的一部分

我們通過 pcie 將自定義 fpga 連接到 M.2 連接器(通道 C/2 - j16)

相關(guān)uboot日志:

U-Boot

2023-05-09 12:00:30

時鐘系統(tǒng)為硬件系統(tǒng)的各個模塊提供時鐘信號,就像人的脈搏心跳一樣不可或缺,而stm32的結(jié)構(gòu)較為復(fù)雜,不同的硬件可能對時鐘信號有不同的要求,因此在系統(tǒng)中設(shè)置多個振蕩器,分別提供時鐘信號,實際中經(jīng)常從一

2022-01-11 07:31:55

最近將xilinx官方PCIe end point例子下到VC709中,插上電腦主板時沒有任何反應(yīng),通過分析原因,發(fā)現(xiàn)主板提供的差分時鐘在經(jīng)過IBUFDS_GTE2后無輸出時鐘(該時鐘用于PCIe核

2016-04-08 16:47:28

個典型的小型應(yīng)用網(wǎng)關(guān)不需要各種I/O接口。盡管如此,NUC還是包含了一個PCIe插槽,并提供了一個可用的插頭,可以通過它訪問USB、SMBus以及電源和地。來源:網(wǎng)絡(luò),如侵刪

2018-10-01 22:26:01

使用VTT電源。一般情況下,DDR的數(shù)據(jù)線都是一驅(qū)一的拓撲結(jié)構(gòu),且DDR2和DDR3內(nèi)部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到較好的信號質(zhì)量。DDR2的地址和控制信號線如果是多負載的情況下

2018-08-09 22:09:18

的主要參數(shù)。一般情況下,對電阻器應(yīng)考慮其標(biāo)稱阻值、允許偏差和標(biāo)稱功率;對電容器則需了解其標(biāo)稱容量、允許偏差和耐壓。一文讀懂電阻和電容的不同電阻器和電容器的標(biāo)稱值和允許偏差一般都標(biāo)在電阻體和電容體上,而在

2017-11-14 15:43:40

COF結(jié)構(gòu)智能屏 單獨強大的51系統(tǒng)框架 資源充足,頻率高。我對原來工業(yè)控制加熱設(shè)備部分簡化一下程序移植,基本達到目的。 實現(xiàn)工業(yè)控制加熱設(shè)備等功能。硬件框架如上圖所示,硬件部分基于 迪文COF結(jié)構(gòu)智能

2022-03-31 17:34:45

是將PCIe參考時鐘更改為引腳Y4,Y3與ucf文件中的默認P4,P3引腳。我懷疑GTP_DUAL_X0Y4,X0Y3磁貼在X4,X1實現(xiàn)中沒有接收時鐘。 (我無法讓一個LED閃爍,以便

2019-08-15 07:47:42

?開發(fā)板測試:1、 安裝windrive 2、LED狀態(tài)顯示 3、測試讀寫 PCIE開發(fā)板介紹:1、原理圖介紹 PCIE TLP協(xié)議介紹:1、分析存儲器寫報文結(jié)構(gòu) 2、分析存儲器讀報文結(jié)構(gòu) PCIE

2022-02-14 09:50:22

example例程。紫光的PCIE IP雖然沒有像xilinx那樣可以直接使用Block Design設(shè)計,但是仔細讀一遍官方例程的DMA模塊,進而開發(fā)自己的東西,還是能夠很好用起來紫光的PCIE

2023-11-17 14:35:30

小弟最近在研究PCIE的系統(tǒng)結(jié)構(gòu)。有一點想不明白。如果一個CPU外掛一個系統(tǒng)內(nèi)存DDR,同時一片F(xiàn)PGA通過PCIE接口連接CPU,CPU做為Host主橋,F(xiàn)PGA做為PCIE設(shè)備。那么根據(jù)PCIE

2016-04-06 16:24:36

本帖最后由 eehome 于 2013-1-5 10:01 編輯

1.一個pciex16插座包含16條pcie通道能拆分使用么或者擴展么 比如構(gòu)成兩個獨立的pciex8接口如果能,兩個能同時

2012-10-19 00:57:16

的,而且輸入噪聲與輸出噪聲無關(guān)。緩沖器的抖動輸出可通過該公式計算: 。LMK00338 是一款超低附加抖動 PCIe 時鐘緩沖器。對于第 3 代 PCIe 應(yīng)用而言,一般具有 30fs rms 的附加

2018-09-17 16:12:25

如何讀懂一份datasheet文檔

2017-11-05 14:57:22

學(xué)習(xí)硬件的第一節(jié)課:學(xué)習(xí)讀懂原理圖讀懂原理圖對嵌入式軟件工程師和程序員尤為重要。在深入細節(jié)之前請注意,對所有的嵌入式設(shè)計人員來說、能懂得硬件工程師創(chuàng)建和使用的來描述其硬件設(shè)計的原理圖和符號是非

2021-12-20 07:14:36

PCI Express? (PCIe?) 是一項業(yè)界領(lǐng)先的標(biāo)準(zhǔn)輸入/輸出 (I/O) 技術(shù),是服務(wù)器、個人電腦以及其它應(yīng)用中最常用的 I/O 接口之一。該標(biāo)準(zhǔn)多年來不斷發(fā)展,以適應(yīng)更高的數(shù)據(jù)速率

2022-11-22 08:04:25

錯誤的路徑約束嗎?2. ILA能否以200Mhz或250Mhz的工作頻率工作?3. MMCM的輸出是否構(gòu)成一個自由運行的時鐘?因為從ipcorem出來的user_clk源于我相信的PCIe時鐘。4.

2019-09-25 09:26:14

PCI Express (PCIe)是嵌入式和其它系統(tǒng)類型的背板間通信的一個非常理想的協(xié)議。然而,在嵌入式環(huán)境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結(jié)構(gòu)的PCIe時鐘分配方案就變得

2019-09-26 07:56:41

PCI Express (PCIe)是嵌入式和其它系統(tǒng)類型的背板間通信的一個非常理想的協(xié)議。然而,在嵌入式環(huán)境中,背板連接器引腳通常很昂貴。因此,采用點對點連接的星型結(jié)構(gòu)的PCIe時鐘分配方案就變得

2019-08-30 06:54:47

如何優(yōu)化PCIe應(yīng)用中的時鐘分配?

2021-05-24 06:44:45

。準(zhǔn)備用ARM11來作為移植linux的平臺現(xiàn)在在做什么:linux的內(nèi)核太復(fù)雜,牽扯到很多數(shù)據(jù)結(jié)構(gòu),我還是剛上大三的本科生,很多數(shù)據(jù)結(jié)構(gòu)得自己補習(xí)。給自己的短期目標(biāo)就是:讀懂一個輕量級的操作系統(tǒng)內(nèi)核

2014-09-19 13:01:51

。準(zhǔn)備用ARM11來作為移植linux的平臺現(xiàn)在在做什么:linux的內(nèi)核太復(fù)雜,牽扯到很多數(shù)據(jù)結(jié)構(gòu),我還是剛上大三的本科生,很多數(shù)據(jù)結(jié)構(gòu)得自己補習(xí)。給自己的短期目標(biāo)就是:讀懂一個輕量級的操作系統(tǒng)內(nèi)核

2014-09-19 13:08:39

SI52147-EVB,用于PoE無線接入點的時鐘發(fā)生器評估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標(biāo)準(zhǔn)的9端口PCIe時鐘發(fā)生器

2020-08-27 14:27:11

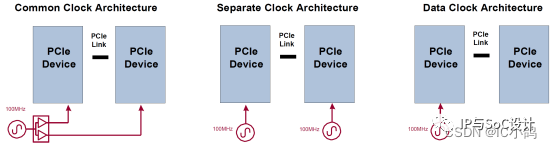

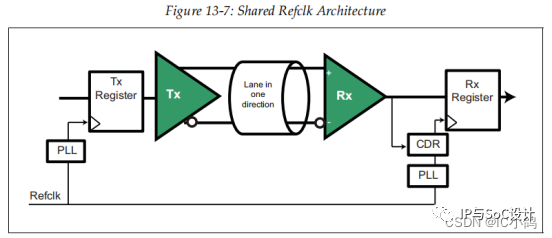

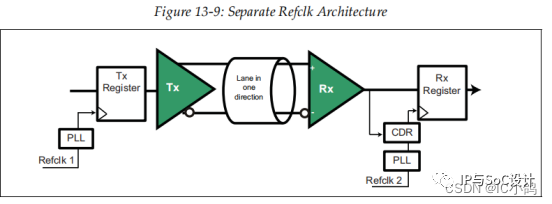

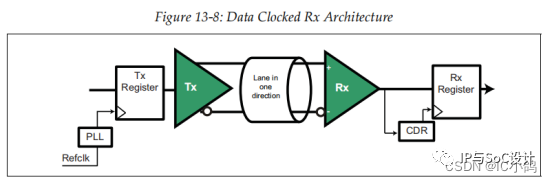

問題描述及復(fù)現(xiàn)步驟:PCIE通常采用Common REFCLK Rx Architecture (CC):PCIE Separate Refclk Architecture:請問3588Q pcie3.0 RC和EP端是否支持采用獨立的REFCLK時鐘。如果支持,有沒有特殊要注意的地方。

2023-02-07 15:13:55

我們的設(shè)計利用了PCIe內(nèi)核,該內(nèi)核遇到了一些時序錯誤。為了確保設(shè)計得到適當(dāng)?shù)募s束,我一直在審查所有輸入/輸出延遲,輸入抖動和系統(tǒng)抖動限制。在我們的設(shè)計中,PCIe時鐘源是125MHz振蕩器。我無法

2020-08-04 10:31:33

PCI Express是一種高性能互連協(xié)議,被廣泛應(yīng)用于網(wǎng)絡(luò)適配、圖形加速器、網(wǎng)絡(luò)存儲、大數(shù)據(jù)傳輸以及嵌入式系統(tǒng)等領(lǐng)域。文中介紹了PCIe的體系結(jié)構(gòu),以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

一文讀懂駐波比(VSWR)的常識及意義

2021-01-07 07:13:18

COF(chip on FPC)智能屏是基于迪文低功耗雙核T5L0 ASIC,將整個智能屏核心電路放到液晶模組

2021-12-28 15:44:28

迪文T5L平臺COB結(jié)構(gòu)智能屏是基于迪文自主研發(fā)的高性價比雙核T5L系列芯片,將整個智能屏核心電路放到PCB板子上,集成整合觸摸屏(電阻觸摸和電容觸摸

2022-06-15 13:49:45

總線時鐘結(jié)構(gòu)科利登系統(tǒng)有限公司大部分并行總線和高速串行總線的區(qū)別主要在于發(fā)送端和接收端不同的同步方式。由于其很高的復(fù)雜性,總線時鐘結(jié)構(gòu)成為芯片架構(gòu)的最主要

2009-12-19 15:25:48 17

17 PCIe授時卡時鐘板卡支持多種參考輸入和輸出,可根據(jù)需求采用不同的組合為計算機系統(tǒng)提供高精度時間信息,同時也可對外授時。支持GPS/北斗、PTP輸入、B碼(DC)作為參考源,輸出10M、B(DC)碼

2024-01-09 13:28:11

Silicon Laboratories (芯科實驗室有限公司)日前宣布擴展其PCI Express(PCIe)時鐘發(fā)生器和時鐘緩沖器產(chǎn)品組合。

2012-02-02 09:31:56 1395

1395 基于子樹重構(gòu)的三維時鐘樹拓撲結(jié)構(gòu)優(yōu)化_錢晨

2017-01-07 18:56:13 0

0 I DT公司多重市場時序產(chǎn)品部總經(jīng)理Kris Rausch介紹說:“隨著我們9FGL產(chǎn)品系列的發(fā)布,IDT公司的低功耗、高性能PCIe時鐘發(fā)生器產(chǎn)品組合中增加了3.3V器件,所有這些產(chǎn)品都可以滿足

2018-04-13 10:09:00 2291

2291 一個簡化的PCIe總線體系結(jié)構(gòu)如上圖所示,其中Device Core and interface to Transaction Layer就是我們常說的應(yīng)用層或者軟件層。這一層決定了PCIe設(shè)備的類型和基礎(chǔ)功能,可以由硬件(如FPGA)或者軟硬件協(xié)同實現(xiàn)。

2018-04-21 09:21:13 5264

5264 LMK0033x是德州儀器(TI)推出的業(yè)界最低抖動的PCIe時鐘扇形緩沖器。現(xiàn)在就讓德儀的工程師向你介紹它的具體情況吧!

2018-06-13 11:52:00 4883

4883 本文檔的主要內(nèi)容詳細介紹的是MINI PCIE座子接插件的結(jié)構(gòu)原理圖免費下載。

2020-08-10 08:00:00 23

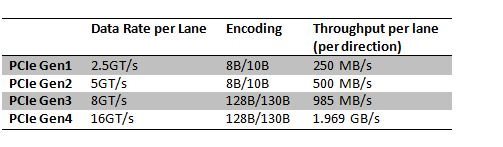

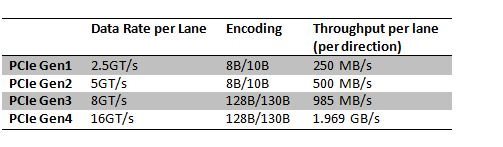

23 具有 16 G 每秒傳輸 (GT/s) 的比特率。第 4 代的規(guī)范預(yù)計將在 2014 或 2015 年發(fā)布。

表 1:各代 PCIe 的數(shù)據(jù)吞吐量

隨著數(shù)據(jù)速率的提升,參考時鐘需求

2021-11-23 11:07:32 3237

3237

1 PCIE基本概念1.1 PCIE拓撲架構(gòu)圖1.2 PCIE Switch內(nèi)部結(jié)構(gòu)圖1.3 PCIE協(xié)議結(jié)構(gòu)圖2 PCIE枚舉原理2.1 Type0&Type1配置頭空間2.2 拓撲示例

2021-12-17 18:29:51 26

26 PCIe 和網(wǎng)絡(luò)時鐘抖動測量之間的另一個顯著差異在圖 2 中并不明顯。數(shù)字采樣示波器 (DSO) 用于獲取時鐘周期或波形文件以計算 PCIe 時鐘抖動,而不是 PNA。造成這種情況的主要原因是 PCIe 時鐘支持?jǐn)U頻,而網(wǎng)絡(luò)時鐘不支持,而且從歷史上看,PNA 一直無法使用正在擴頻的時鐘。

2022-05-05 15:50:44 4513

4513

?xilinx 的 FPGA 時鐘結(jié)構(gòu),7 系列 FPGA 的時鐘結(jié)構(gòu)和前面幾個系列的時鐘結(jié)構(gòu)有了很大的區(qū)別,7系列的時鐘結(jié)構(gòu)如下圖所示。

2022-07-03 17:13:48 2592

2592 PCIe 協(xié)議指定標(biāo)準(zhǔn)的參考時鐘為 HCSL 電平的 100 MHz 時鐘,Gen1~Gen4 下要求收發(fā)端參考時鐘精度在 ±300 ppm 以內(nèi),Gen5 要求頻率穩(wěn)定性 ±100 ppm。一顆性能優(yōu)秀的參考時鐘是整個PCIe系統(tǒng)成功的基礎(chǔ)。

2022-07-08 14:19:16 5616

5616 如何優(yōu)化 PCIe 應(yīng)用中的時鐘分配

2022-11-07 08:07:15 0

0 PCIe發(fā)展至今已經(jīng)從最初的1.0升級到了6.0,但很多人對于PCIe只知其然而不知其所以然,小編今天就帶大家一起來看一看。

2022-12-01 10:37:49 1025

1025 9ZXL1951D PCIe 時鐘發(fā)生器評估板用戶指南

2023-03-21 19:21:13 0

0 由PCI-SIG發(fā)布的PCIe板卡結(jié)構(gòu)規(guī)范。Revision 4.0 Version 0.9.

2023-06-19 09:59:44 5

5 極景微發(fā)布超小封裝PCIe5.0時鐘發(fā)生器日前,極景微(UltraSilicon)宣布,推出兩款支持PCIe5.0接口標(biāo)準(zhǔn)的1輸出及2輸出時鐘發(fā)生器,分別為US6D101和US6D102。該芯片具有

2023-02-02 15:25:54 999

999

9ZXL1951D PCIe 時鐘發(fā)生器評估板用戶指南

2023-07-07 19:19:11 0

0 電子發(fā)燒友網(wǎng)站提供《PI6CDBL401B低功耗PCIe時鐘芯片.pdf》資料免費下載

2023-07-25 14:41:49 0

0 的標(biāo)準(zhǔn);PCIe時鐘采用HCSL這個電平標(biāo)準(zhǔn)使RC(CPU)側(cè)與EP(子卡)側(cè)時鐘,在不同生產(chǎn)廠家之間能夠保持電平兼容。它需要串行33Ω電阻和驅(qū)動源端50Ω電阻下拉到地。HCSL為電流輸出驅(qū)動,輸出結(jié)構(gòu)通過50Ω電阻器下拉接地的15mA開關(guān)電流驅(qū)動,標(biāo)稱信號擺幅750mV。

2023-09-15 14:39:54 2447

2447

一文讀懂,什么是BLE?

2023-11-27 17:11:14 634

634

今天來聊一聊時鐘樹。首先我先講一下我所理解的時鐘樹是什么,然后介紹兩種時鐘樹結(jié)構(gòu)。

2023-12-06 15:23:47 482

482 高性能20路PCIe時鐘緩沖器新品推介SQ82100PCI-Express(PCIe)是一種高速串行計算機擴展總線標(biāo)準(zhǔn),主要用于擴充計算機系統(tǒng)總線數(shù)據(jù)吞吐量以及提高設(shè)備通信速度。目前服務(wù)器

2023-12-20 08:19:38 240

240

電子發(fā)燒友App

電子發(fā)燒友App

評論