AHCC2001PCI/CPCI 是能提供 4 路高速串行數據通信的模板, 完成系統內部計算機網絡與外部多路串行接口的互連功能。它內含一片高性能的串行通信控制器,可以用于各種高速數據通信場合。每路

2019-04-25 09:40:07

74LS194引腳功能74LS194功能特征74ls194串行數據到并行數據的轉換

2021-03-02 07:00:20

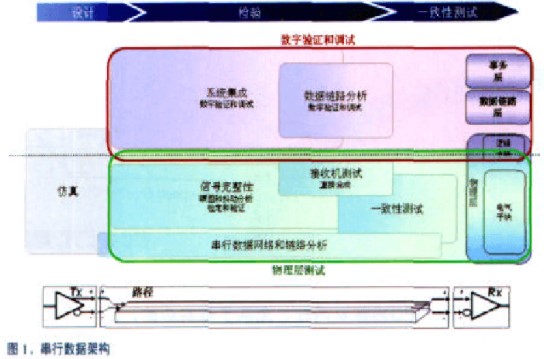

和其它8000 系列采樣示波器上使用。關閉的眼圖、接收端均衡和發送端目前,大量的串行數據鏈路設計和標準進入了信道(互連)嚴重限制高速信號、使接收端一端眼圖關閉的時代。經過鏈路傳輸后可以使用均衡方法張開

2008-11-26 10:44:02

` 本帖最后由 Stark揚 于 2018-9-26 08:56 編輯

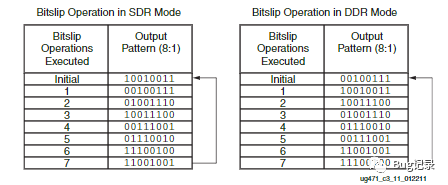

我使用的是序列因子為4的iserdes,數據輸入形式為6bit的差分數據。我在對設計進行仿真時發現,轉成單端后,只有最低

2018-09-22 15:51:22

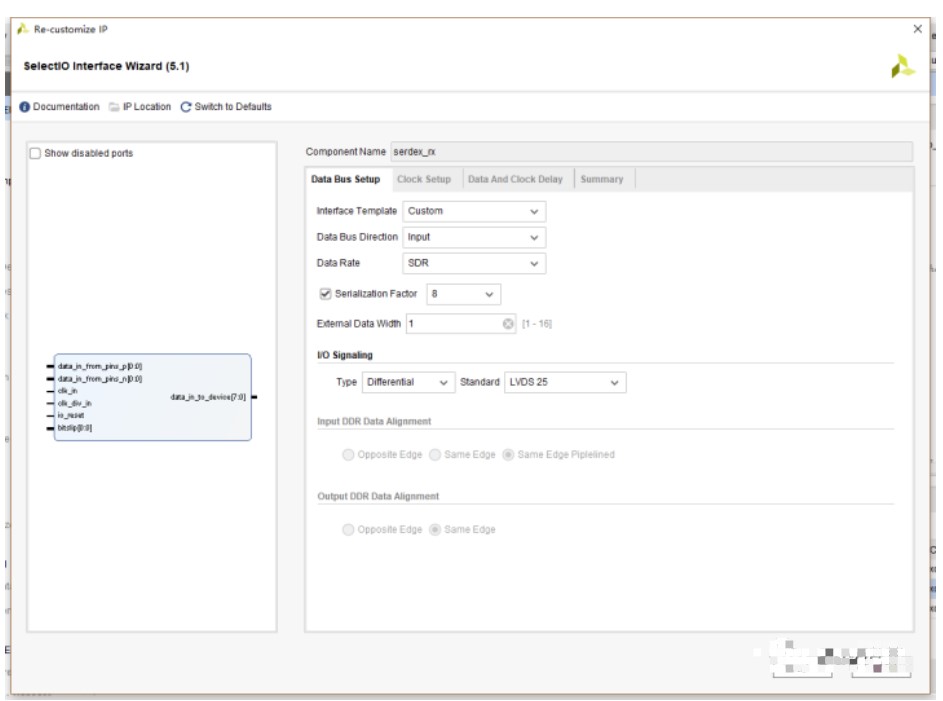

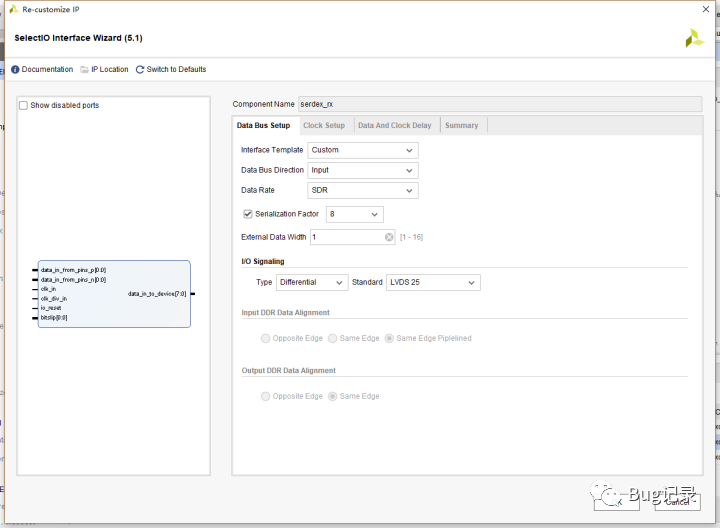

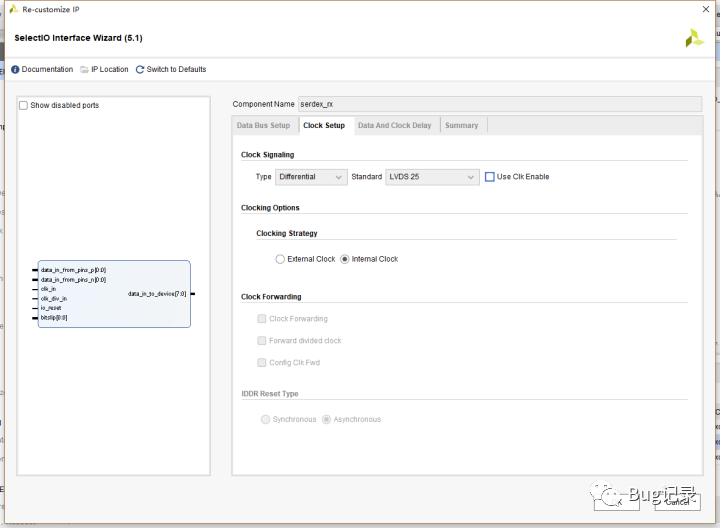

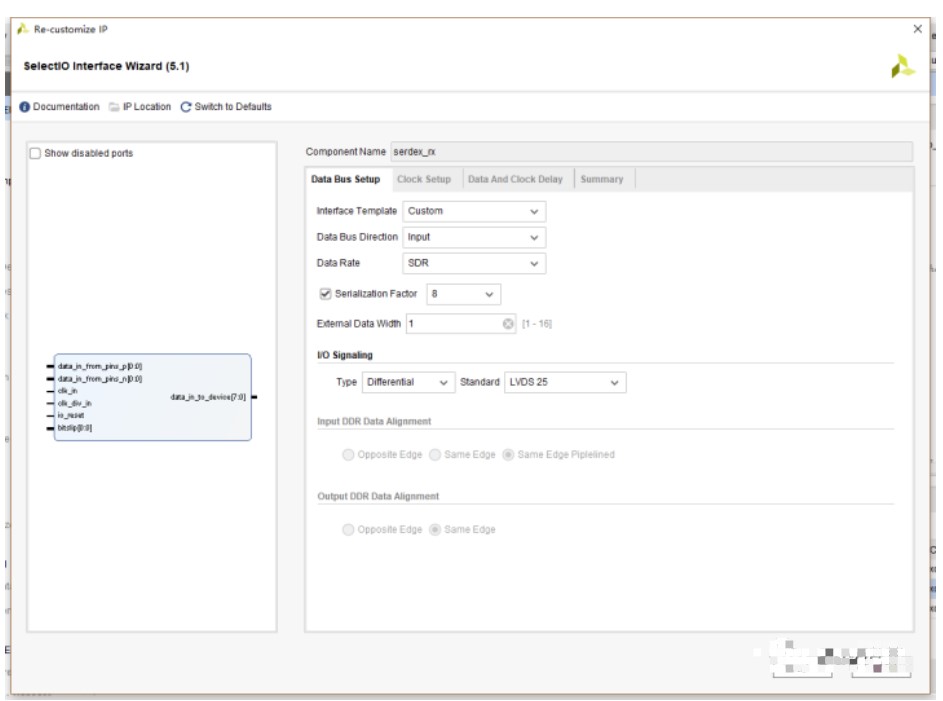

現在輸入2路lvds串行數據和1路lvds時鐘信號,頻率480M,請問如何解出串行數據,并恢復成并行TTL信號

2013-04-28 18:08:32

摘要:串行數據通信要解決兩個關鍵技術問題,一個是數據傳送,另一個是數據轉換。所謂數據傳送就是指數據以什么形式進行傳送。所謂數據轉換就是指單片機在接受數據時,如何把接收到的串行數據轉化為并行數據,單片機在發送數據時,如何把并行數據轉換為串行數據進行發送。

2012-07-31 23:27:44

發送串行數據,后者用來接收串行數據。兩者物理上是不同的,只是共用一個地址99H。2)輸入移位寄存器:在接收控制器的控制下,將輸入的數據位逐位移入接收SBUF。3)串行控制寄存器SCON:控制串行通信的工作方式,并反映串行通信口的工作狀態。4)定時器T1:作波特率發生器,控制傳輸數據的速度。2.串行通

2021-12-06 07:30:10

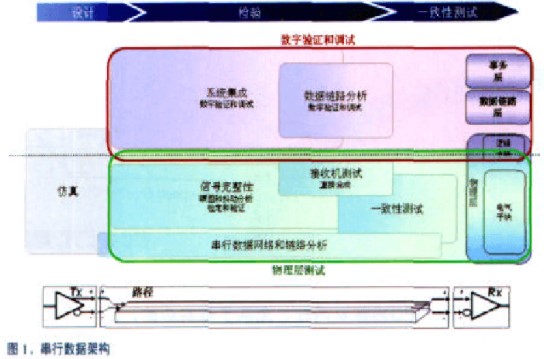

小弟這次給大家帶來了串行數據一致性測試和驗證測量基礎知識其中提到了一些高速串行信號的測試測量方法和簡單的原理性介紹,適合初學者使用。PS。這其中提到的一些測量設備現在已經升級為最新的儀器設備,但是測試的原理和技術還是可以讓大家閑暇時候品一品的。如有任何問題,歡迎壇友們與小弟交流~~~

2013-04-16 16:17:23

想各位高手來指教一下串行發送字節和讀取字節以及數據的寫法,以及使用方式。

2013-08-25 23:34:27

由圖所示,第一個脈沖喚醒作用,后面8個脈沖下降沿時發送數據。 我現在要寫個程序來接收這串數據,用51單片機的INT0中斷, 第一個喚醒脈沖的下降沿觸發中斷,進入中斷后,在每個時間下降沿時讀取數據口

2013-11-05 21:58:10

計算機主板上的典型總線結構有什么共同點?高速串行數據鏈路一致性測試的難點有哪些,該如何應對?

2021-04-09 06:47:14

高速CAN通訊總線接收到無效串行數據是何原因?怎么解決呢?

2023-05-09 10:39:29

32位并行數據轉為串行輸出時,出現部分數據錯誤,想請教一下可能是什么原因導致的

2017-09-12 10:46:53

我發現了一個錯誤,該錯誤使UART 中的串行數據無法傳輸

我使用

frightanic.com

分支的這些文件 NodeMCU 自定義構建:主

提交

2023-05-09 06:31:27

RS-232、RS-422、RS-485都是串行數據接口標準; RS-232:RS-232是全雙工通信方式,采用不平衡傳輸方式,即單端通訊,收發端數據信號是相對于信號地的。有RX和TX兩個信號端

2019-04-23 09:40:05

RocketIO高速串行接口本人在北京工作6年以上,從事FPGA外圍接口設計,熟練使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX協議,Aurora協議

2014-03-01 18:46:35

我可以知道 SPC57S-Eval 套件板上的哪個引腳用于串行時鐘和串行數據嗎?我想將陀螺儀傳感器連接到板上。

2022-12-01 06:13:04

如題,補充 由于下位機發送數據飛非常快,用中斷接收數據的話,MCU一直進入中斷,無法進行數據處理?如何解?小白求大神指點!!

2015-12-09 20:50:06

嗨,我正在使用XILINX IP-Core Generator的GTX。我正在使用Kintex-7。在接收器中,接收器接收串行數據并轉換成并行數據,并行sync_header。 PMA如何將64位數據

2020-07-23 08:14:53

磨練設計思想:輸入信號 clk 和 D【32】(32bit并行數據),經過FPGA轉換后,輸入m_clk和 D(1bit的串行數據)。要求傳輸速度高,可靠性好。大家各抒己見,寫寫自己的總體思想(當然是詳細點好)。

2008-09-19 23:53:51

/*名稱:并行數據轉換為串行數據 說明:切換連接到并串轉換芯片74LS165 的撥碼開關,該芯片將并行數據以串行方式發送到 8051 的RXD引腳,移位脈沖由 TXD提供,顯示在 P0 口

2012-03-02 09:38:12

/*名稱:串行數據轉換為并行數據 說明:串行數據由 RXD 發送給串并轉換芯片 74164,TXD 則用于輸出移位時鐘脈沖,74164 將串行輸入的 1 字節轉換為并行數據,并將轉換的數據通過 8

2012-03-01 09:40:49

若1bit串行信號data_in按高位先發的順序傳輸一個8bit的數據,data_en為使能信號,請用位拼接符實現串行數據的接收并輸出接收的8bit數據data[7:0]

2023-08-07 16:05:19

三種常用的串行數據傳輸總線一、SPI1.1 概念SPI(Serial Peripheral Interface - 串行外設接口)是一種用于短距離通信(主要是嵌入式系統中)的同步串行通信接口規范

2022-02-10 06:32:34

接口是外設和主設備連接的方式/規則/協議的名稱;XX總線是主設備連接某一類接口的名稱1.串口串行數據接口標準(根據時間發展順序介紹):RS-232;命名為EIA-232-E標準;通信距離短、速率低

2021-12-17 08:29:16

聯系的。不會因為這位有錯誤,使下一位不能傳輸。并行數據是一組數據其中一位不對,整組數據都不行。高速并行,串行布線的區別并行數據因為是一組一組一起傳的,每一位都必須是一起傳輸到位,不能說有一位可以遲到一點

2019-10-01 07:00:00

接收器、控制器oller被設置為根據接收到的數據字節打開/關閉一個引腳,但是它沒有工作。我試著將計算機輸出的內容讀到另一臺計算機上的串行應用程序上,以調試串行數據,但是數據似乎被正確地發送出去。對此有

2019-06-06 07:07:07

描述JESD204B 鏈路是數據轉換器數字接口的最新趨勢。這些鏈路利用高速串行數字技術提供很大的益處(包括增大的信道密度)。此參考設計解決了其中一個采用新接口的挑戰:理解并設計鏈路延遲。一個示例實現

2018-11-21 16:51:43

高速LVDS數據接收:接收時鐘檢測(檢測接收時鐘的存在),接收時鐘對齊(對接收時鐘進行移相),數據串行轉并行,接收數據字節序對齊(Comma碼對齊),接收數據Los-of-Sync狀態機,8B

2014-03-01 18:47:47

多FPGA系統中自定義高速串行數據接口設計.pdf

2011-03-21 17:28:15

多FPGA系統中自定義高速串行數據接口設計為方便多FPGA系統中主從FPGA之間的命令與數據傳輸,節省連接的引腳數量,設計了一種基于FPGA的自定義高速串行數據傳輸模塊。對主從串行模塊進行了詳盡

2012-08-11 11:49:57

你好,我必須發送3個長TIPE可變形式的PLC到CY8C KIT01,我應該使用這個工具包的串行端口,但我沒有任何線索如何開始。我應該使用哪些組件來編程它來使用串行端口發送和接收數據。懇求幫助

2019-04-09 12:06:23

如何使用STM32與PC進行數據的相互發送接收?

2021-12-06 06:00:58

USART發送接收的基本方式是什么?如何使用STM32與PC進行數據的相互發送、接收?

2022-02-18 07:38:26

:串口按位(bit)發送和接收字節(byte)的通信方式,可以將來自CPU的并行數據字符轉換位連續的串行數據流發送出去,同時可將接收的串行數據流轉換為并行的數據字符提供給CPU的器件,一般...

2021-12-24 06:46:50

已知一串行數據,怎么樣在這串行數據的頭加一個開始標記(如“01111110”),尾部再加一個結束標記,請大家指導指導,謝謝啦

2014-05-26 16:15:28

各位前輩好,新人自學FPGA,現在碰到一個費解的問題,我例化了一個rom核,輸出是十位的數據,現在需要接入到一個串行輸入的DA模塊上,在網上查到說需要將并行數據轉換為串行數據輸入到DA中,即把十位

2019-03-06 08:55:27

本文介紹了基于Xilinx Virtex-6 FPGA的高速串行數據傳輸系統的設計與實現,系統包含AXI DMA和GTX串行收發器,系統增加了流量控制機制來保證高速數據傳輸的可靠性。最后進行了仿真測試,測試結果顯示系統可以高速可靠地傳輸數據。

2021-05-25 06:45:36

我想把一個串行數據發送到一個BLE模塊,而BLE模塊應該將接收到的串行數據廣播到Mesh網絡的所有節點(BLE模塊)。那么我該怎么做呢????在沒有編寫任何程序的情況下,是否有任何應用程序可以完成此

2018-10-17 16:18:01

; P2=SBUF;delay(20); } } 用三個LS165,將并行數據轉為串行數據,為什么第一個芯片控制的,控制的第二部分LED,第二個165控制第三部分LED,求助,這是為什么

2017-05-03 00:17:09

內容如題!就是串行數據輸入430再從430并行輸出數據,并將數據顯示到液晶屏上去。求程序如何編寫?在這里先謝謝大神了

2013-04-24 19:42:45

用于高速數據轉換器的串行接口有哪些選擇?

2021-04-09 06:55:28

串行數據系統的基本知識抖動的基本概念串行數據系統中誤碼率的概念抖動的來源

2021-04-07 06:19:00

怎么模電的方法設計一個紅外串行數據傳送整形電路?

2020-05-03 21:24:55

AD2S1200的串行數據輸出波形及處理的角度波形是什么樣的?

2023-12-20 06:07:28

各位高人! 請問at91sam7s64中,能否利用SSC進行18位串行數據接收?

2018-07-09 01:05:17

嗨,大家好,我正在使用ML550板的參考設計(xapp856),它使用V5,XC5VLX50T,1136引腳,速度等級-1。接收器側的16個ISERDES執行1:4反序列化以產生64位的并行總線

2020-06-01 17:18:53

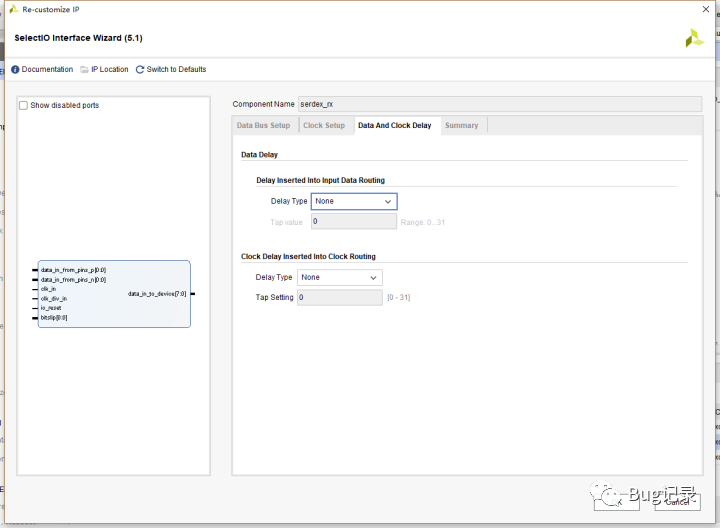

我可以推遲輸入數據的Iserdes嗎?或者我必須在V5中將IOdealy連接到Iserdes嗎?

2020-04-24 09:47:19

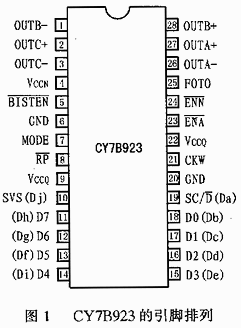

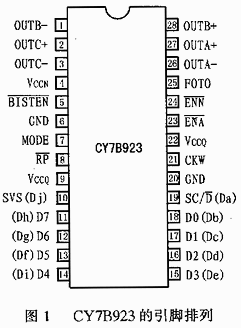

文章介紹了CYPRESS半導體公司推出的一種用于點對點之間高速串行數據通信的發送芯片CY7B923的原理及應用.較詳細的介紹了CY7B923的管腳功能、內部組成、工作原理及工作方式.同時給出

2009-04-27 16:45:21 37

37 USB已經越來越被廣泛的應用,因為它的高速傳輸性能和即插即用特性已逐漸取代了傳統的串行總線.而如果使用USB實現并行數據的高速傳輸,同時為MCU、DSP等處理器開發USB接口以實現與PC

2009-04-27 16:55:19 23

23 本文提出了一種串行數據通信系統的設計方案,利用MATLAB 提供的儀器控制工具箱serial 類對象來實現串行數據通信,硬件設計中采用TL16C550C 芯片使設計具有很好的可擴展性,用信號

2009-06-12 15:23:08 23

23 介紹基于Matlab 環境的微機與單片機串行數據通信方法。該方法利用Matlab 的Instrument Control 工具箱的serial 類對象實現串行數據通信,

2009-09-03 12:10:55 25

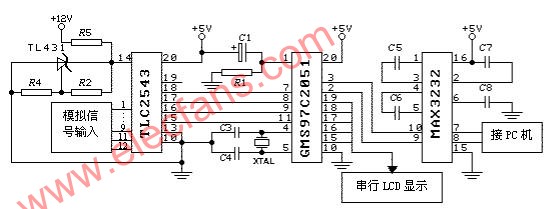

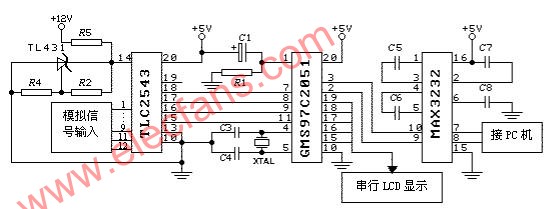

25 以GMS97C2051單片機為核心,采用TLC2543 12位串行A/D轉換器,設計了一個串行數據采集/傳輸模塊,給出了硬件原理圖和主要源程序。關鍵詞:串行A/D轉換器;串行數據傳輸;GMS97C2051單

2010-06-08 07:53:17 49

49 本基礎指南旨在幫助您了解串行數據傳輸的一般方面,并介紹適用于這些新興串行技術的模擬和數字測量要求。 串行數據一致性測試和驗證測量基礎知識本手冊將幫助您理解串行

2010-08-05 15:14:53 32

32 摘 要:介紹了FPGA最新一代器件Virtex25上的高速串行收發器RocketIO。基于ML505開發平臺構建了一個高速串行數據傳輸系統,重點說明了該系統采用RocketIO實現1. 25Gbp s高速串行傳輸的設

2010-09-22 08:41:18 43

43 串行數據轉換器接口

問:我現在需要安裝節省空間的數據轉換器,認為串行式轉換器比較適合。為了選擇 和使用這種轉換器,請問我需要了解些什

2010-01-04 17:40:44 1719

1719

一個單片機串行數據采集/傳輸模塊的設計 摘 要:以GMS97C2051單片機為核心,采用TLC2543 12位串行A/D轉換器,設計了一個串行數據采集/傳輸模塊,給

2010-04-24 22:41:42 1778

1778

對于現代的高速串行系統,系統之間的協調工作顯得更為突出,協議間的任何沖突也會導致整個系統出現問題,本文將為大家重點介紹力科示波器針對高速串行信號物理層、鏈路層和協議層的解決方案。

2011-03-16 10:09:29 1628

1628

摘要 RS-232 或許是PC 和電信應用中最成功的串行數據標準RS-485 和RS-422 則是工業應用中最成功的標準這些標準并不是直接兼容的但是在控制場合和儀表應用中常常需要在它們之間進行數據

2011-07-11 18:02:44 94

94 高速串行數據鏈路的一致性測試是個復雜的課題,既要求測試設備廠家能提供高性能的儀器,又要求測試工程師能充分利用儀器去解決問題。

2012-04-24 16:00:20 994

994 本文討論了RS232串行數據截取器的設計方案,并做出了產品,進行了實驗。系統穩定、可靠,可以有效地截取串行通信數據。該系統可以為有相關需求的人員提供幫助。

2012-06-01 16:46:35 3980

3980

。。。。。。串行數據轉換為并行數據。。。。。。。

2015-11-10 10:01:10 9

9 。。。。。。并行數據轉換為串行數據。。。。。。。

2015-11-10 10:00:07 0

0 多FPGA系統中自定義高速串行數據接口設計

2016-05-10 11:24:33 24

24 基于8051的Proteus仿真-串行數據轉換為并行數據

2016-09-01 23:32:32 10

10 基于8051的Proteus仿真-并行數據轉換為串行數據

2016-09-01 23:32:32 16

16 本文介紹了TDR阻抗測試和高速串行鏈路分析,首先介紹了高速串行數據鏈路的挑戰,然后對高速串行數據鏈路時域-TDR和高速串行數據鏈路頻域-S參數:IConnect 進行了分析,最后提出了泰克TDR與S參數的解決方案。

2017-10-12 16:42:16 7

7 隨著現代工業科技飛速發展,某些特定的大容量數據系統要求有很高的采樣頻率及較高的通信效率。本文通過ADC12D800RF實現高速采樣,并基于Xilinx Virtex6 FPGA的GTX高速串行接口

2017-11-17 04:37:01 11284

11284

移位寄存器是指寄存器中所存的代碼能夠在移位脈沖的作用下依次左移或右移。本文主要介紹了74LS194引腳功能與特征,其次詳細的說明了74ls194串行數據到并行數據的轉換。

2017-12-22 14:18:52 24814

24814

12864液晶串行和并行數據顯示的源程序

2018-04-08 17:51:55 57

57 在數字視頻中,為了便于數字信號的遠距離傳輸,將并行數據轉換成串行數據,經電纜驅動器通過電纜傳輸給接收端。SDI就是這種串行數據接口的簡稱。本文以1080i/50系統為例,對HD-SDI的原理做簡單

2018-09-04 09:38:00 14121

14121 計算機、消費電子和通信行業設計核心正采用最新的高速串行技術,數據傳送速率持續提高,如10Gb/s以太網的出現、PCI Express已經從1.0版演進到2.0版,速率也從2.5Gb/s提高到

2019-09-11 08:03:00 1353

1353

本文檔的主要內容詳細介紹的是單片機并行數據轉換為串行數據的仿真電路圖

2020-01-10 14:37:35 12

12 本文檔的主要內容詳細介紹的是單片機串行數據轉換為并行數據的仿真電路圖免費下載

2020-01-10 14:37:00 12

12 本文檔的主要內容詳細介紹的是單片機串行數據轉換為并行數據的C語言程序和仿真資料免費下載。

2020-06-11 17:30:39 9

9 本文檔的主要內容詳細介紹的是單片機并行數據轉換為串行數據的C語言程序和仿真資料免費下載。

2020-06-11 17:30:36 10

10 CY7B923是CYPRESS半導體公司推出的一種用于點對點之間高速串行數據通信的發送芯片。CY7B923采用的是基帶傳輸通信方式,并支持帶電插拔(熱接插)。其內部電路主要包括時鐘產生器、輸入寄存器、編碼器、移位寄存器、三對差分PECL輸出對以及測試邏輯等。

2021-05-22 17:20:17 3598

3598

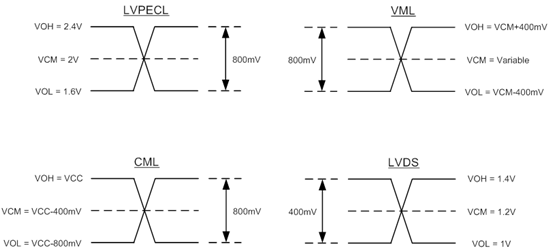

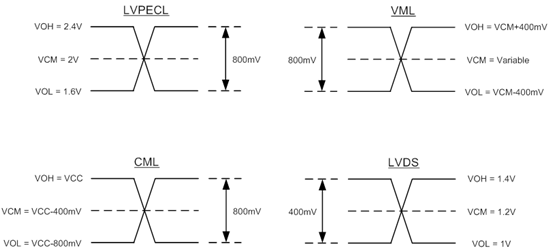

系統當前包含 CML 與 LVDS 等各種接口標準。理解如何正確耦合和端接串行數據通道或時鐘通道的傳輸線路是一項非常重要的技能。

2022-01-28 09:33:00 1333

1333

但是,在內部處理信號時,數據信號往往是多bit信號,而傳輸過程中需要用到單bit串行傳輸技術,所以,中間需要有一個轉換器,實現并串轉換,這就需要用到SERDES技術。

2022-08-20 11:11:09 4044

4044

眼圖醫生(Eye Doctor)是力科于2006年推出的用于高速串行數字電路設計的強大工具,包括了虛擬探測(virtual probing)與接收端均衡(receiver equalization

2022-09-30 09:08:41 976

976 基于AT89C51單片機并行數據轉換為串行數據仿真及代碼

2023-05-04 17:50:20 0

0 基于AT89C51單片機串行數據轉換為并行數據仿真及代碼

2023-05-05 10:32:01 0

0 OSERDES實現并串轉換,只需要管發送并不需要管接收到的數據如何,所以它的操作相對于ISERDES來說簡單;

2023-06-16 14:14:53 708

708

SerDes是Serializer/Deserializer的縮寫,即串行器和解串器,顧名思義是一種將并行數據轉換成串行數據發送,將接收的串行數據轉換成并行數據的”器件“。

2023-12-13 10:02:42 516

516

正在加载...

電子發燒友App

電子發燒友App

評論