1. 什么是UTMI?

UTMI (USB2.0 Transceiver Macrocell Interface):USB2.0 通用傳輸接口。最初設計是為了減少開發廠商的工作量,旨在提供一種通用標準,來完成USB 2.0 的 底層協議數據處理。UTMI 的出現是為了加速USB2.0 外設的開發。

UTMI 最主要的作用主要是負責USB 協議中最底層的物理電信號的轉換。其本質是一個接口規范,與usb phy 相連。

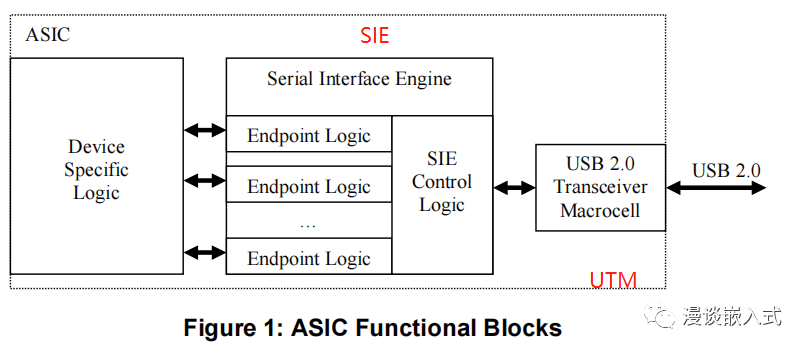

下圖總結了在這個規范中表達的一些概念:

USB 2.0 Transceiver Macrocell(UTM):

Serial Interface Engine(SIE):串行接口引擎

1.1 UTM

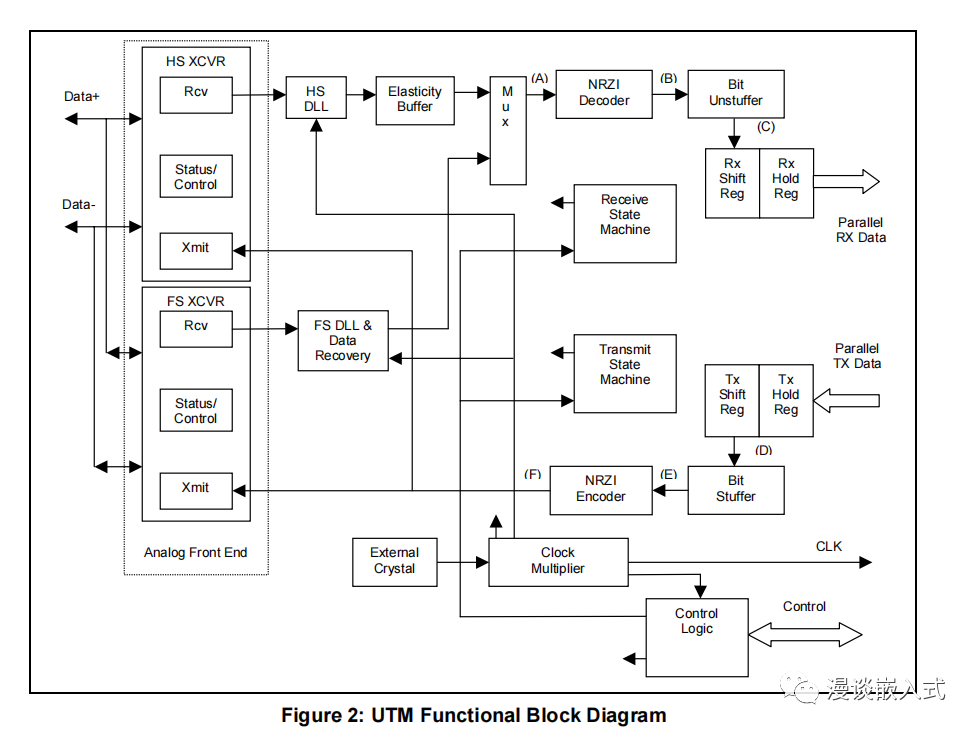

UTM 處理低級別的USB協議和信號。這包括諸如;數據序列化和反序列化、位填充和時鐘恢復和同步等特性。

UTM的主要焦點是將數據的時鐘域從USB 2.0速率轉移到與ASIC中的一般邏輯兼容的速率。

UTM 的關鍵特點:

消除了高速USB 2.0邏輯設計

標準收發器接口為USB 2.0 SIE VHDL提供多個IP源

支持480 Mbit/s“高速”(HS)/ 12 Mbit/s“全速”(FS);僅支持FS和“低速”(LS);僅支持 LS 1.5 Mbit/s串行數據傳輸速率。

利用8位并行接口傳輸和接收USB 2.0電纜數據。

SYNC/EOP生成和檢查

高速和全速運行,以支持“雙模式”設備的發展

bit-stuffing/bit-unstuffing, bit error detect

能夠在FS和HS終端/信號之間切換

等等

UTMI被設計用于支持HS/FS、僅FS和僅LS的UTM實現。這三個選項允許一個單一的SIE實現被使用與任何速度的USB收發器。供應商可以選擇最滿足其需求的收發器性能。

1.2 Serial Interface Engine(SIE)

SIE ?可以進一步細分為兩種類型的子塊:SIE 控制邏輯 和 端點邏輯。

SIE 控制邏輯包含 USB PID 和 地址識別邏輯,以及其他處理USB數據包和事務的排序和狀態機邏輯。

端點邏輯:包含特定于端點的邏輯:端點編號識別、FIFO和FIFO控制等。

一般來說,任何USB實現都需要SIE控制邏輯,而端點的數量和類型將隨著應用程序和性能要求的不同而變化。

1.3 Device Specific Logic

這是將USB接口與設備的特定應用程序連接起來的邏輯。

1.4 UTM function block

UTM block 如上圖。

Device-> HOST:并行 TxData -> bit Stufffer -> NRZI Encoder -> xmit -> D+/D- -> HOSTHOST -> Device:Host -> D+/D- -> NRZI Decoder -> Bit Unstuffer -> 并行Rx Data -> Device

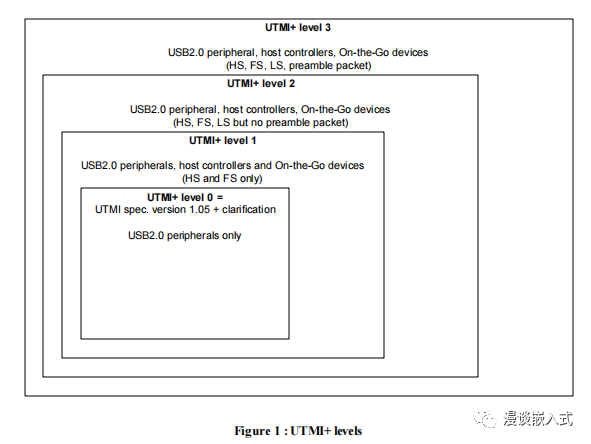

2. UTMI 版本

UTMI 第一個版本,是2001 年 發布的(UTMI spec V1.05)。后續隨著UTM 發展,引出了UMTI+ 版本。具體的版本如下:

?

| 版本 | 功能 | 備注 |

|---|---|---|

| UTMI+ level0 | 僅僅支持 USB2.0 設備 | 也是UTMI 第一個版本, V1.05 版本 |

| UTMI+ leve1 | 支持USB2.0 設備、host 和 OTG 功能(HS/FS)。 | 不支持 LS, 2.0 用得最廣的接口 |

| UTMI+ level2 | 支持USB2.0 設備、host 和 OTG 功能 (HS/FS/LS with no hub support) | 支持LS 模式 |

| UTMI+ level3 | 支持 USB2.0 設備、host 和 OTG 功能(HS/FS/LS with hub support) | ? |

?

UTMI+ 不同版本接口協議規范是向下兼容的。對于學習USB2.0 我們可以研究UTMI+ level0 或者level1 就夠了,高版本的協議無非是在舊有的協議基礎上新增了一些信號處理。

3. UTMI 接口介紹

UMTI+ 不同版本之間信號還是很多的。我們以usb2.0 device 為主先介紹level0/level1。

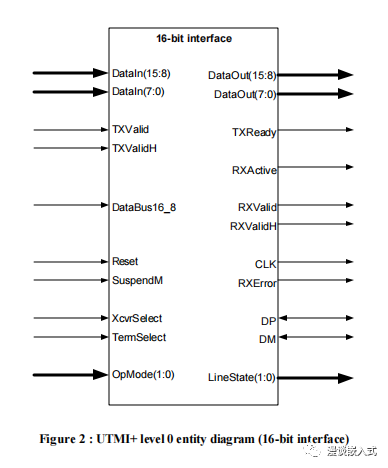

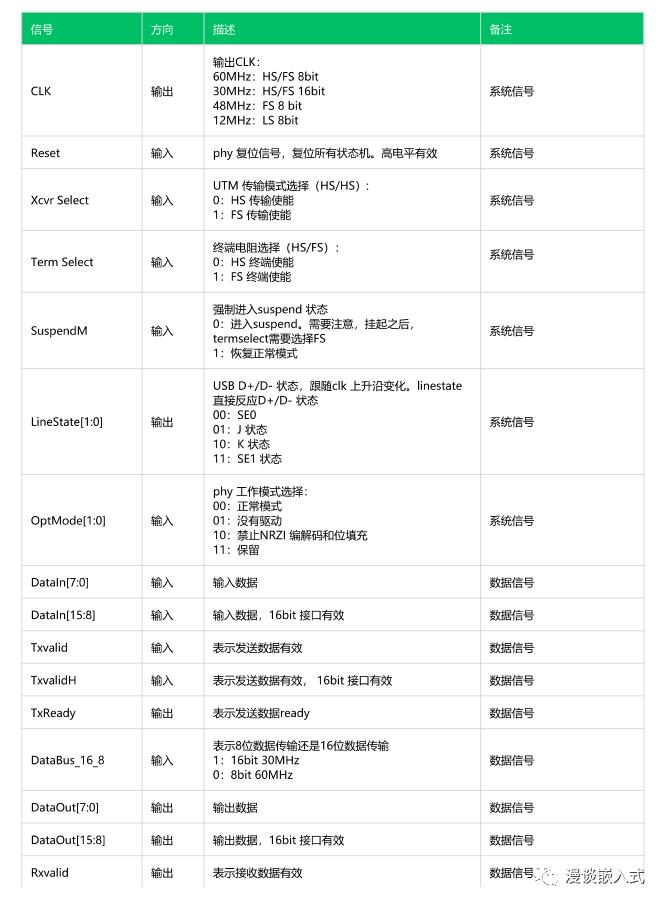

3.1 UTMI+ level0

UTMI+ level0 規范,來源于UTMI 1.05 接口規范。下圖給出了具有16位接口的UTMT+ level0 收發器所需要的所有接口信號:

對于具有8位接口的UTMI+0級收發器,TXValidH、RXValidH、DataBus16_8、DataIn(15:8)和DataOut(15:8)信號,則是不需要的。

對于 USB 2.0 phy 調試我們需要關注的幾個信號(注意phy 的調試可能只在芯片fpga 階段,或者外掛usb phy 才存在。一旦芯片集成完了,無法修改,后續的調試就大概率涉及不到phy 的調試):

CLK:UTMI_CLK 輸出時鐘

Reset:UTMI_RST

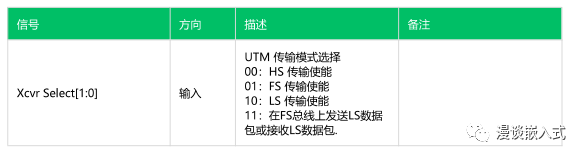

Xcvr Select:傳輸模式選擇

Term Select:終端選擇

LineState:D+/D- 狀態。高速枚舉的時候確認電平狀態是否ok

DataBus_16_8:8bit/16bit 選擇。

一旦速度枚舉成功,說明整個輸入輸出信號無誤,剩下的就到軟件層面了。

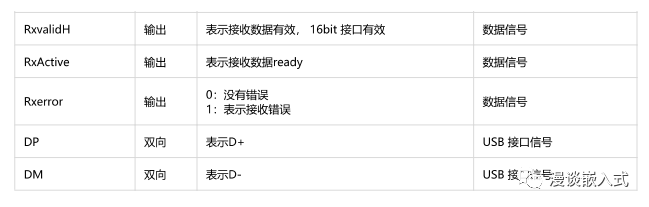

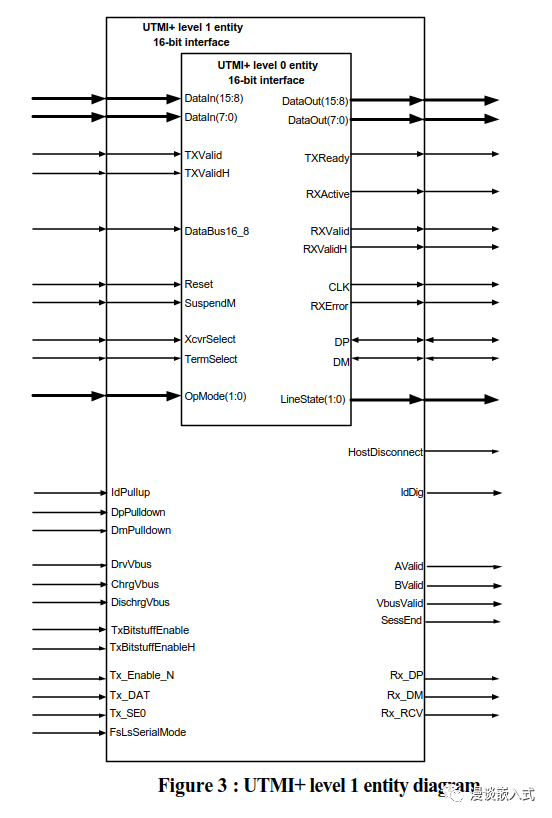

3.2 UTMI+ level1

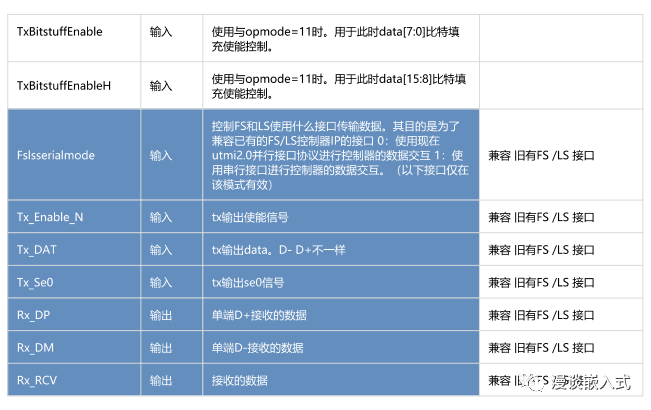

UTMI+ level1 規范相對于 level0 多了對OTG 設備的支持。新增了一些OTG /HOST 相關的接口。

信號接口如下:

對于USB2.0, 我們大多數情況下,用得最多的就是level1。同時支持:

device mode

host mode

OTG mode

對于單純的只需要device 的設備我們在芯片設計階段可以考慮,選擇level0 的接口phy。

當然無論level 幾,都可以向前兼容的。關鍵是usb 控制器的輸入信號給的是什么標準。

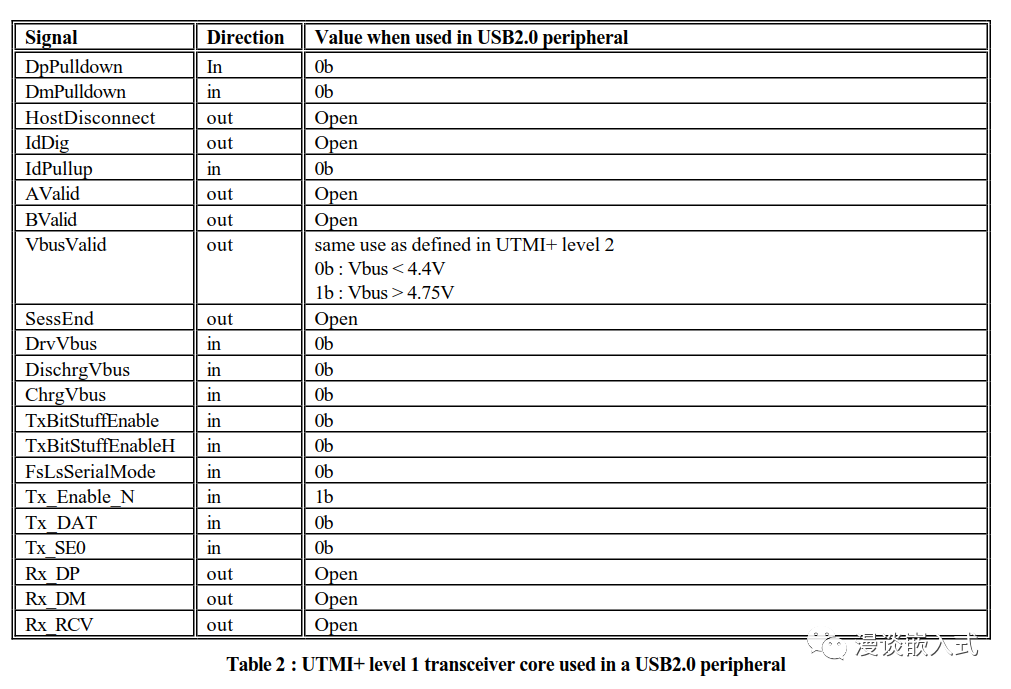

usb 2.0 設備 默認信號:

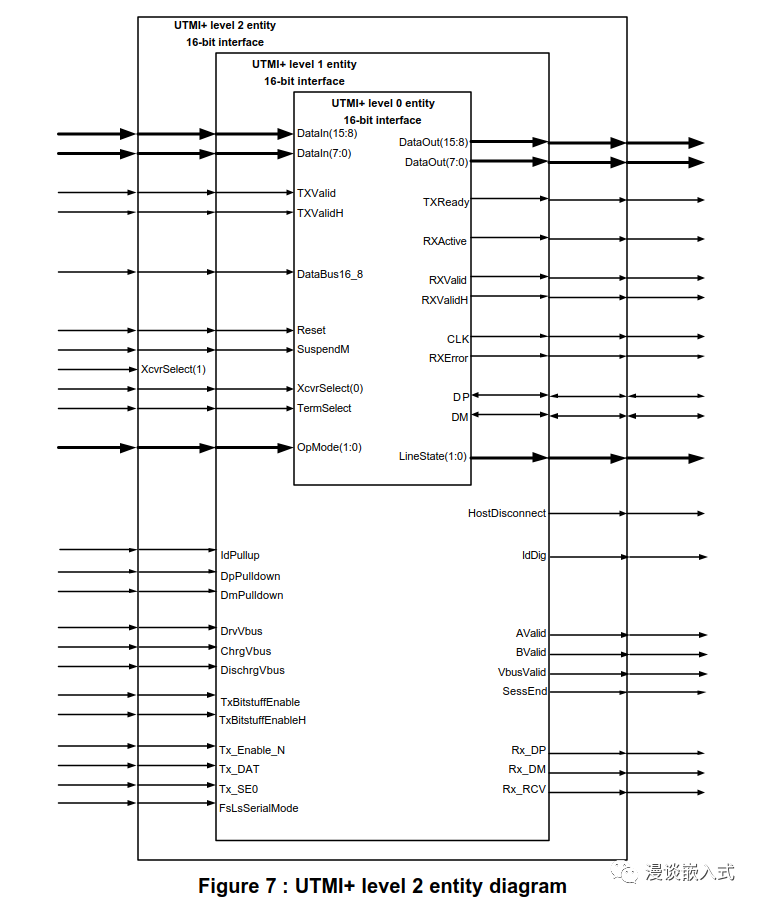

3.3 UTMI+ level2

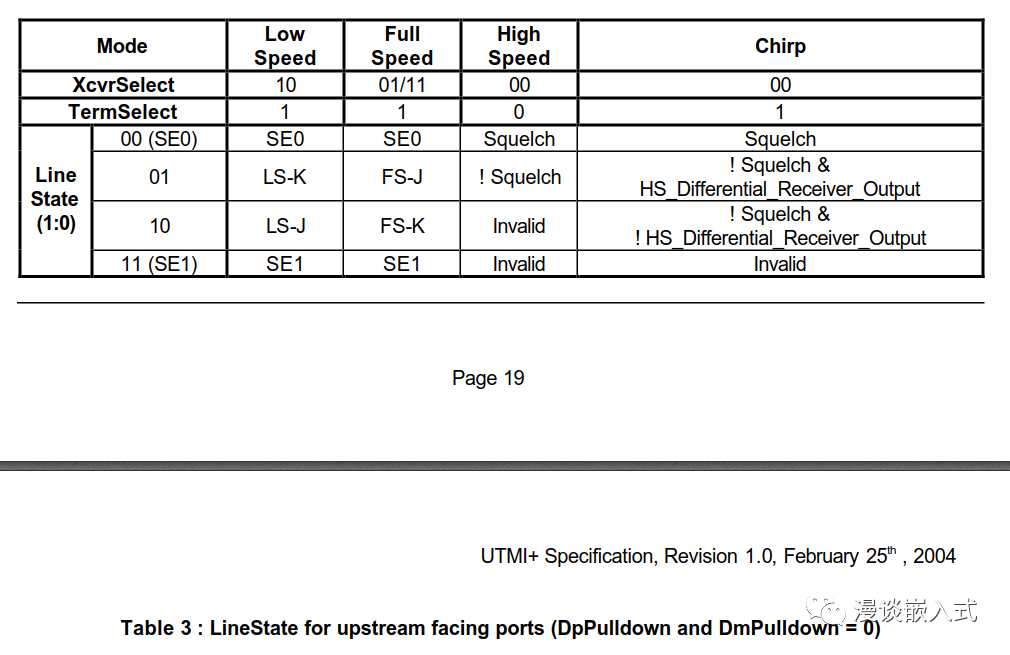

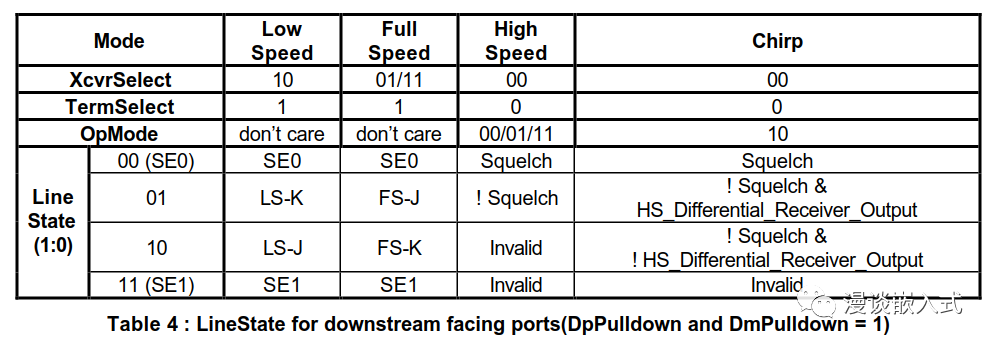

與UTMI+1相比,增加1bit的XcvrSelect信號來控制LS選擇。另外需要注意linestate等信號在LS時也要表示不一樣狀態。

新增接口:

LineStare 狀態:

在全速和低速模式下,lineState(0)總是反應DP,而lineState(1)總是反應DM。

下行端口lineState:設備端

上行端口lineState:host 端

修復一個前文錯誤:

下行端口(downstream):設備到主機行為。

上行端口(upstream):主機到設備行為

3.4 UTMI+ level3

與UTMI+2相比,沒有增加新的信號。只增加XcvrSelect=2'b11時的功能,該功能定義在UTMI+2中該位是保留的。

這是對level2的進一步增強。在這個級別中,處理必須通過FS集線器從主機發送到LS設備的LS流量是可行的。

在level2中,如果使用并行接口,USB On-the-Go DRD的主機控制器部分只能與直接連接到主機的LS設備進行通信。

如果XcrvSelect是11b,則收發器將在發送LS分組之前在FS處發送 preamble packet。在接收模式下,它將等待在LS收發器啟用的情況下接收LS數據包。收發器必須使用FS令牌(快速上升和下降時間以及相反的極性)發送所有數據(FS preamble packet和LS數據)。注意,此時的令牌為特殊令牌PRE(有關PRE,本文不做介紹)。

一句話總結:level2 只能直接和LS 設備通信, level3 可以通過hub 外接LS 設備。

4. 其他

4.1 Chrip Sequence

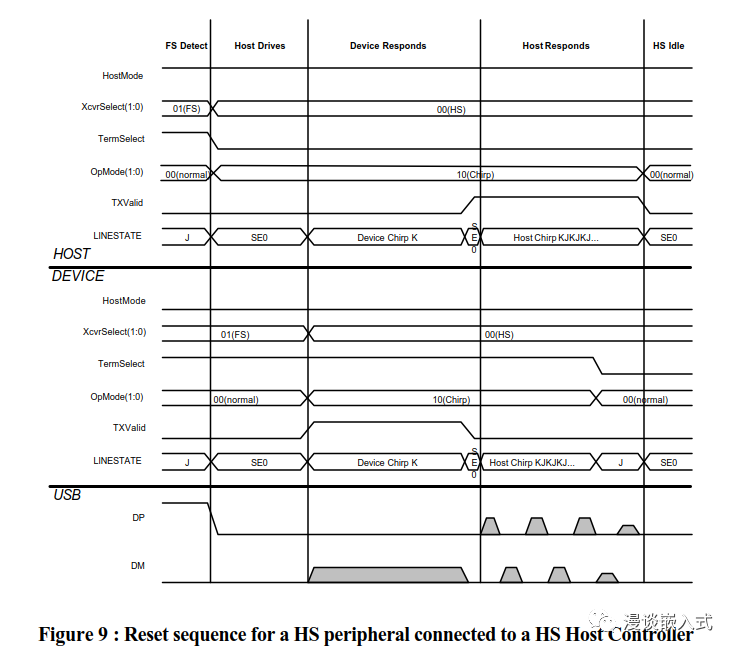

對于高速設備連接到整個usb host 整個時序如圖所示:

FS detect:全速設備檢測

Host Driver:主機產生SE0,持續10ms

Device Responds:設備回應chirp K

Host Responds:主機回應 chirpk/j ?對,設備切換到高速模式

HS Idle:高速Idle

通常我們關注最多的就是 USB 設備端的這段信號(DP/DM)。對于XcverSelect optmode linestate 等信號,一般對軟件層面是隱藏的。一旦這些信號有問題。說明IC 設計有問題,比如信號連接不對,比如控制器輸出的信號有問題 。

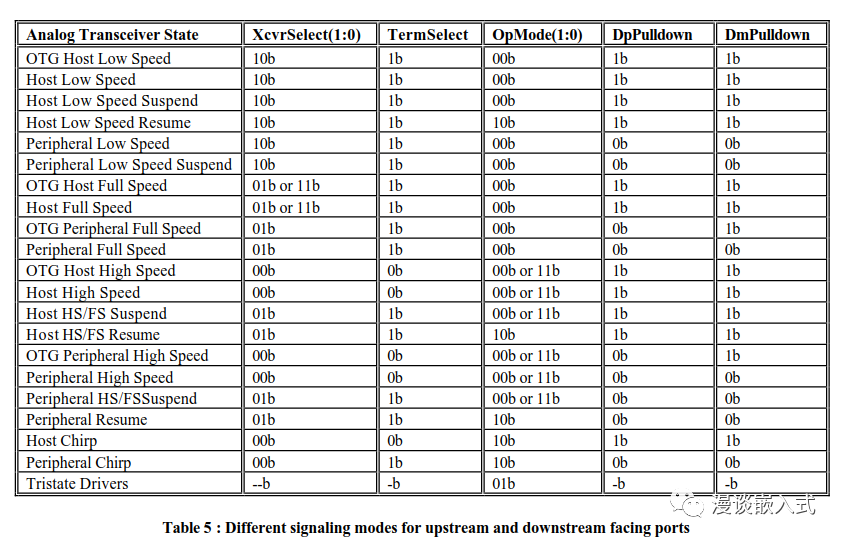

4.2 不同的信號模式

5. 總結

本文主要介紹了UTMI 及 UTMI+ 接口規范。詳細對比了level0/level1/levle2/level3 。對于初學者而言,可以先以level0 為基準學習,后續再逐步深入到其他規范。

本文檔適用于哪些人員:IC 設計人員、FPGA 驗證人員、USB 底層深入學習人員。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論